## THÈSE DE DOCTORAT DE

## L'UNIVERSITÉ DE RENNES 1

ÉCOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Informatique

Par

## Jaechul LEE

# Approximate communication techniques exploration for efficient nano-photonics interconnects

Exploration de techniques de communication approximatives pour des interconnexions nano-photoniques efficaces

Thèse présentée et soutenue à Lannion, le Unité de recherche : IRISA

#### Rapporteurs avant soutenance:

François VERDIER Professeur des universités, Université de Nice Côte d'Azur Camel TANOUGAST Professeur des universités, Université de Lorraine

#### **Composition du Jury:**

Président : Prénom NOM Fonction et établissement d'exercice (à préciser après la soutenance)

Examinateur : Frédéric PETROT Professeur des universités, Université Grenoble Alpes

Examinatrice : Angeliki KRITIKAKOU Maître de conférences HDR, Université de Rennes 1

Dir. de thèse : Cédric KILLIAN Maître de Conférences HDR, Université de Rennes 1

Maître de Conférences HDR, Université de Rennes 1

## RÉSUMÉ

#### Contexte

L'évolution des architectures de calcul a progressivement conduit à des systèmes très complexes, intégrant de plus en plus de transistors soumis à des fréquences toujours plus élevées. Si cette évolution, connue sous le nom de loi de Moore, a perduré pendant de longues années, les problèmes de consommation énergétiques ont remis en cause l'accroissement continu de la fréquence d'horloge, induisant alors une possible stagnation des performances. Pour éviter cette stagnation et continuer à offrir toujours plus de performances au sein des processeurs, les concepteurs ont alors proposé de multiplier le nombre de cœurs de calcul en conservant la fréquence à une valeur élevée, mais sans qu'elle n'augmente. Par ce biais, les capacités de calcul ont continué à croître permettant alors d'implémenter des applications toujours plus complexes. Toutefois pour exploiter pleinement ces capacités de calcul, les applications ont dû être décrites sous forme de tâches ou threads parallèles et déployées sur l'ensemble des cœurs. Or, ce type d'implémentation conduit inévitablement à des échanges entre les cœurs de calcul ou entre les cœurs et la mémoire, nécessitant alors un support de communication efficace.

Parallèlement à cette évolution au sein des processeurs, des architectures plus spécifiques se sont développées, intégrant l'ensemble des éléments permettant de gérer un système, ces architectures sont connues sous le nom de systèmes sur puce (System-on-Chip, SoC). Ces architectures sont généralement soumises à des contraintes plus sévères que les processeurs d'usage général, en particulier elles doivent souvent être frugales en termes d'énergie pour préserver les batteries alimentant le système et limiter les recharges parfois coûteuses ou difficiles à assurer. L'évolution de ces architectures a également conduit à des systèmes fortement parallèles confrontés aux mêmes problèmes de communications précédemment évoqués.

D'une manière générale, pour une architecture disposant d'un faible nombre de cœurs de calcul, un support de communication simple, de type bus, peut être suffisant pour assurer les échanges de données. Par contre, ce type d'interconnexion est connu pour être peu flexible et difficilement capable de suivre une augmentation importante du nombre de cœurs. Pour permettre d'augmenter le nombre de cœurs de calcul tout en assurant une bonne efficacité du système, la notion de réseau sur puce est apparue. Ces réseaux tirent leurs caractéristiques des réseaux d'ordinateurs et miment leur fonctionnement, en particulier, ils sont capables d'acheminer des messages d'un point à un autre à partir d'éléments de routage et d'informations contenues dans les entêtes des messages identifiant, entre autres, la destination à atteindre.

Pour des architectures dont le nombre de cœurs augmente très rapidement, i.e. plusieurs dizaines, centaines voire même plusieurs milliers de cœurs, les réseaux sur puce prennent une place prépondérante et peuvent devenir le goulot d'étranglement si les communications subissent des conflits et des congestions. Le parallélisme matériel disponible dans les architectures n'ayant alors plus d'intérêt puisque les temps de transferts de données deviennent majoritaires devant les temps de calcul. Dans ce contexte, des solutions innovantes doivent donc être définies pour que l'augmentation du nombre de cœurs au sein de ces architectures puisse se poursuivre tout en offrant un gain en performance.

Parallèlement à cette évolution des architectures électroniques, le domaine de la photonique s'est développé et l'intégration de composants optiques sur silicium a fait d'énormes progrès. En effet, depuis plusieurs années déjà, des composants optiques peuvent être intégrés sur du silicium sans remettre en cause tout le processus de fabrication. Bien que de dimensions plus importantes que les transistors, des lasers, des micro-résonateurs, des photo-détecteurs et des guides d'ondes sont désormais disponibles pour supporter des fonctionnalités au sein des architectures numériques classiques. Ainsi, sur la base de ces composants élémentaires, des premières solutions de réseaux sur puce optiques ont vu le jour. Ces réseaux ont la particularité d'offrir des bandes passantes très importantes ainsi que des latences de communications très courtes. Ces caractéristiques les rendent donc très attrayants pour remplacer, ou compléter, les réseaux sur puce électriques classiques qui souffrent de délais assez longs dès lors qu'un message doit atteindre un destinataire éloigné.

## Travaux développés et contributions

Les avantages apportés par ces réseaux optiques (bande passante importante et faible latence) s'accompagnent toutefois d'au moins un inconvénient majeur qui est lié à leur consommation énergétique. En effet, la production d'un signal optique par une source laser est coûteuse, cela est en particulier du à la faible efficacité des lasers, de l'ordre de 15 à 20%. Par ailleurs, le signal optique subit des pertes optiques lorsqu'il transite au sein du guide d'ondes et également à chaque passage par un composant optique, même lorsque celui-ci est inactif. Face à ces constats, l'intégration de photonique sur silicium pour supporter un réseau optique doit donc s'appuyer sur des techniques permettant de profiter des bénéfices de cette technologie tout en réduisant au maximum les inconvénients.

Les travaux présentés dans ce manuscrit adressent cette problématique de l'intégration d'un réseau optique sur puce et proposent des techniques permettant de réduire la consommation énergétique en ajustant au mieux la puissance laser au niveau requis de qualité des communications.

Nos travaux exploitent les propriétés des applications, en particulier par l'utilisation du concept de communications approximatives permettant d'adapter le niveau du signal optique pour conserver globalement de bons résultats au niveau applicatif.

Les travaux que nous avons développés présentent deux contributions qui concernent dans un premier temps i) l'adaptation de la puissance laser aux types de données à transmettre dans le guide d'onde, et dans un deuxième temps, ii) une extension de ces travaux pour prendre en compte la notion de distance entre la source et la destination d'une communication.

Nous avons tout d'abord défini un modèle de coût énergétique des communications pour un réseau sur puce optique. Ce modèle prend en compte l'ensemble des devices optiques supportant les communications. Ce modèle est ensuite exploité pour ajuster la puissance laser optique en vue d'augmenter l'efficacité globale de l'exécution d'une application implémentée sur une architecture multi-cœurs composées de plusieurs dizaines de cœurs de calcul. Seul le type de données est pris en compte dans un premier temps, puis la distance de communication est prise en compte pour aboutir à une solution donnant un compromis intéressant entre la qualité des communications et le coût d'implémentation de la proposition.

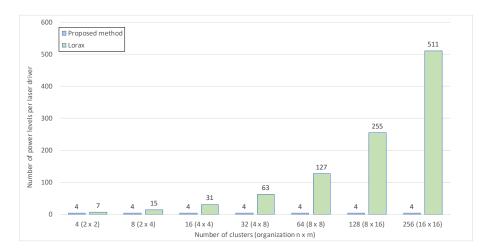

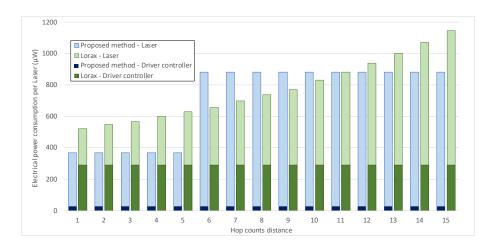

L'ensemble de ces travaux a été validé au travers de simulations principalement basées sur l'outil Sniper. Cet outil nous a permis d'extraire des traces de communication transitant sur le réseau lors de l'exécution de benchmarks sur les architectures cibles. À partir de ces traces, nous avons développé des scripts en Python qui permettent d'analyser le trafic de données et d'appliquer, sur l'ensemble des communications, le modèle de coûts énergétique et temporel précédemment défini. Les résultats montrent qu'il est possible de réduire de façon importante la consommation des lasers tout en maîtrisant le coût matériel d'implémentation de la gestion du système. Notre solution est principalement comparée aux travaux Lorax qui exploitent un concept proche, mais dont le coût d'implémentation est déraisonnable pour des architectures de taille importante. En effet, l'approche développée par les auteurs de la solution Lorax proposent une gestion de la distance de communication très fine, induisant autant de niveaux de puissance laser qu'il existe de cœurs destinataires dans l'architecture. Bien que très intéressante, la solution proposée par ses auteurs n'est pas évaluée en termes d'implémentation matérielle.

## Organisation du manuscrit

Le manuscrit est composé de cinq chapitres. À la suite de l'introduction, un premier chapitre dresse un état de l'art des réseaux sur puce optiques et présente les composants optiques élémentaires nécessaires pour les implémenter. Ce chapitre présente également la technique du calcul approximatif et aborde le concept des interconnexions approximatives qui sera exploité par la suite. Ce chapitre introduit la notion de qualité de communication qui est principalement basée sur un calcul d'erreur de transmission. Les approximations sur les données flottantes sont également abordées au regard de l'erreur générée dans les applications.

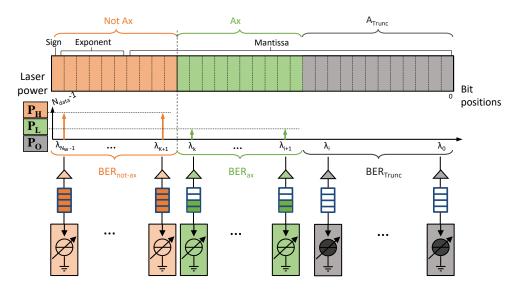

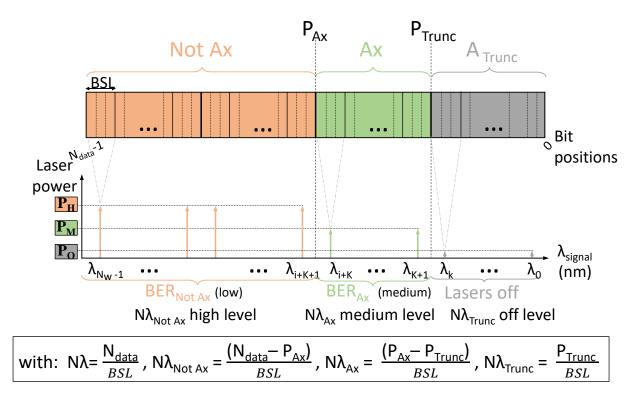

Le chapitre 2 de ce manuscrit aborde la conception d'un lien optique approximatif. Le principe se base sur un lien optique classique sur lequel la gestion des puissances lasers optiques est revisitée pour augmenter l'efficacité énergétique. Le chapitre décrit le lien proposé et explique comment il est possible d'adapter les niveaux de puissance optiques en fonction du type de données à transmettre. Un focus est fait sur les données flottantes dont on sait qu'elles peuvent généralement supporter des approximations sur les bits de poids faibles sans que cela n'entraine de fortes dégradations sur les résultats de certaines

applications, en particulier pour des applications de type traitement d'images, IA, etc.

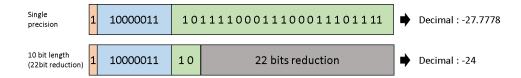

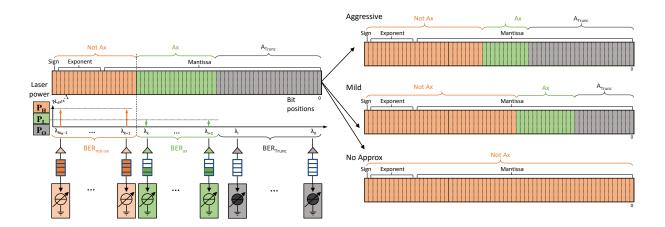

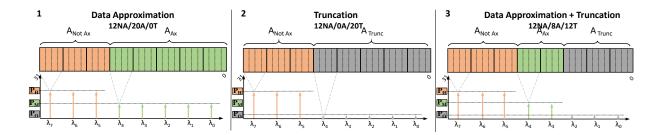

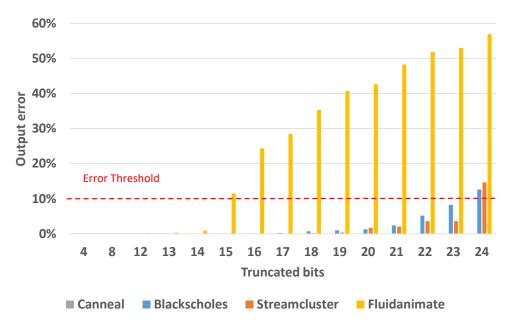

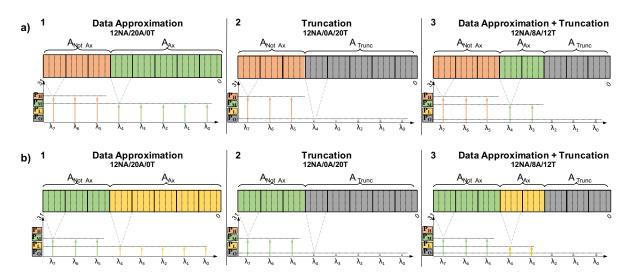

Les approximations proposées sont de deux types, soit il est proposé de réduire la puissance laser (approximation), soit il est proposé d'éteindre le laser (troncation). L'extinction des laser n'étant finalement que le cas extrême de l'approximation. Nous définissons alors un mixte d'approximation et de troncation des bits de poids faibles pour atteindre une bonne efficacité énergétique. Le positionnement des seuils d'approximation et de troncation est étudié afin de juger des gains énergétiques potentiels. Afin de réduire la complexité de notre proposition, les approximations et troncations sont réalisées par ensemble de bits, et non par bit à bit.

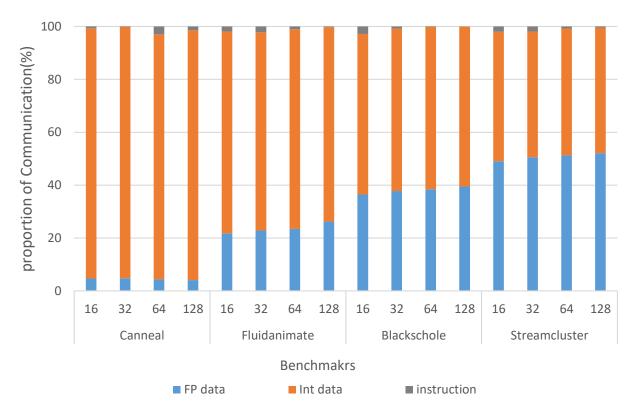

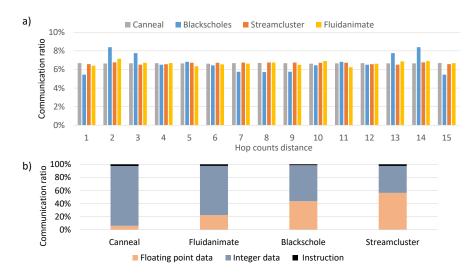

Pour démontrer l'intérêt de notre proposition, nous avons produit un certain nombre de résultats à partir des benchmarks (ApproxBench). Sur cet ensemble d'applications, nous analysons les flux réseaux et nous calculons les proportions de données dites approximables (données flottantes) et de données dites sensibles (données entières ou instructions d'un programme). Nous montrons que les applications ne sont pas toutes adaptées au concept de communications approximatives, puisqu'il existe une grande disparité de ces proportions (variation entre 4% et 50% de données approximables).

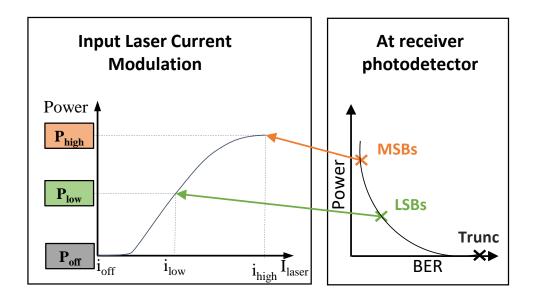

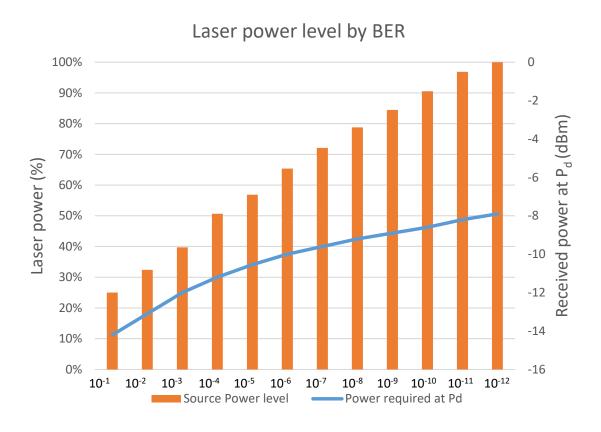

Nous montrons ensuite que, suivant le niveau de qualité de communication requis, exprimé par le taux d'erreur binaire (Bit Error Rate, BER), la puissance laser épargnée peut être plus ou moins importante, variant de 75% à 15% pour des BER respectivement de  $10^{-1}$  à  $10^{-9}$ . Cette étude montre que le gain qui peut être obtenu sera très dépendant de l'application et de son niveau de résilience.

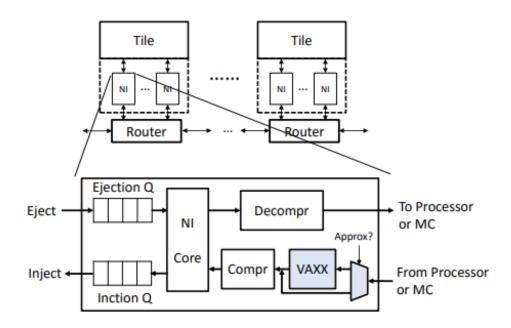

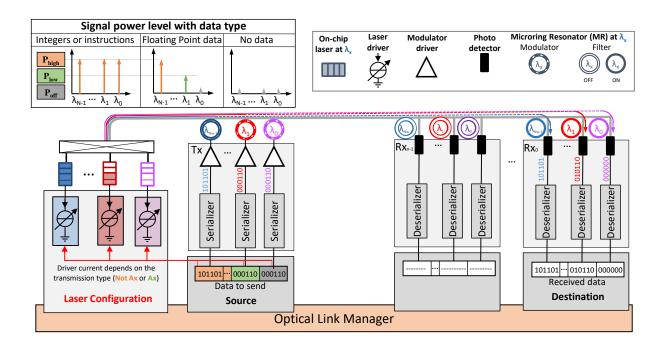

Pour compléter cette étude, l'interface réseau est alors adaptée de façon à pouvoir identifier les types des données à envoyer dans le réseau. L'identification du type est basée sur l'hypothèse d'un stockage différentié des données approximables et critiques dans des zones mémoires différentes, permettant de se baser sur une comparaison de l'adresse pour appliquer ou non le concept d'approximation. Cette solution à l'avantage d'être peu coûteuse à mettre en œuvre.

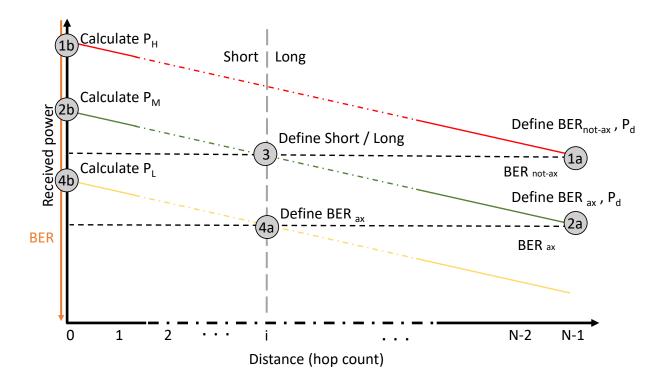

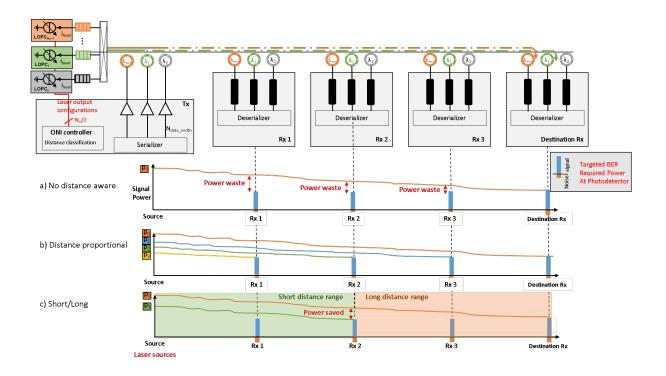

Le chapitre 3 adresse quant à lui la gestion de la distance de communication entre la source et la destination d'un message. Nous proposons une gestion plus fine de la puissance des lasers en tenant compte des pertes qui seront subits par le signal optique dans le guide d'ondes. Connaissant la puissance nécessaire à al destination pour que les photodé-

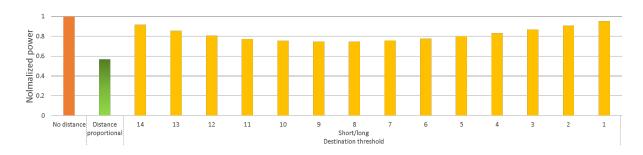

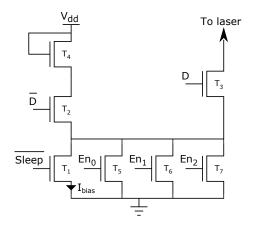

tecteurs soient en mesure de produire le courant électrique représentatif du signal optique, nous montrons qu'il est possible de remonter jusqu'à la source laser en identifiant toutes les pertes. À partir de ce modèle paramétrique, nous montrons qu'il existe un compromis dans la définition du nombre de niveaux de puissance des lasers, et nous démontrons que si l'on s'intéresse au compromis efficacité énergétique - complexité du *driver* du laser, deux niveaux lasers sont suffisants.

Pour illustrer l'intérêt de cette proposition, nous utilisons les mêmes benchmarks que précédemment et nous analysons dans un premier temps la répartition des distances de communications. Cette analyse permet d'exhiber l'intérêt d'une gestion de la distance puisque les résultats montrent qu'il existe une proportion assez homogène des communications courtes et longues distances. Nous montrons ensuite les gains obtenus avec notre proposition et nous les comparons à la solution Lorax.

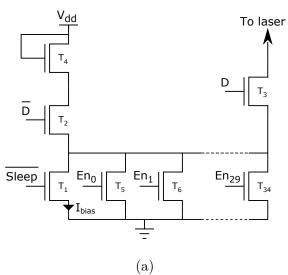

Ce chapitre traite également du *driver* laser qui permet de piloter le courant traversant la diode émettrice du signal optique. Ce *driver* se base sur une mise en parallèle de transistors qui, lorsqu'ils sont activés, permettent d'augmenter le courant dans la diode laser et ainsi de produire un signal optique plus puissant. Le contrôleur du *driver* est également abordé afin d'avoir une évaluation complète de l'ensemble des éléments constituant notre proposition. Des synthèses matérielles, de notre solution et de la solution Lorax, sont réalisées à des fins de comparaisons complètes incluant performance et complexité d'implémentation.

Le dernier chapitre présente les conclusions du document en reprécisant les contributions et les résultats obtenus, puis propose quelques perpectives à ce travail.

## **TABLE OF CONTENTS**

| In | trod | uction  |                                                               | 1  |

|----|------|---------|---------------------------------------------------------------|----|

| 1  | Rel  | ated w  | ork                                                           | ç  |

|    | 1.1  | Silicon | Photonic interconnect NoC                                     | Ć  |

|    |      | 1.1.1   | History and introduction of optical interconnects             | Ĉ  |

|    |      | 1.1.2   | Components of silicon photonic interconnect                   | 10 |

|    |      | 1.1.3   | Physical property of optical components                       | 14 |

|    |      | 1.1.4   | Crosstalk noise in WDM                                        | 18 |

|    |      | 1.1.5   | Optical link and ONoC architecture                            | 20 |

|    |      | 1.1.6   | Energy efficient challenges in optical interconnect           | 23 |

|    | 1.2  | Approx  | ximate computing                                              | 25 |

|    |      | 1.2.1   | Introduction                                                  | 25 |

|    |      | 1.2.2   | Floating-point Data representation                            | 27 |

|    |      | 1.2.3   | Approximate techniques                                        | 28 |

|    |      | 1.2.4   | Floating-point Data approximation                             | 30 |

|    |      | 1.2.5   | Quality balance                                               | 32 |

|    |      | 1.2.6   | Approximate interconnect                                      | 34 |

|    | 1.3  | Summ    | ary                                                           | 36 |

| 2  | App  | proxim  | ate communication in Optical Interconnects                    | 39 |

|    | 2.1  | Idea O  | verview                                                       | 36 |

|    | 2.2  | Approx  | ximate communication in optical link                          | 40 |

|    |      | 2.2.1   | Proposed approximate techniques and approximate level control | 40 |

|    | 2.3  | Propos  | sed communication link                                        | 42 |

|    |      | 2.3.1   | SWMR Channel Design                                           | 44 |

|    |      | 2.3.2   | Floating-point data scheme                                    | 45 |

|    |      | 2.3.3   | Power level definition                                        | 46 |

|    |      | 2.3.4   | Power saving model                                            | 48 |

|    | 2.4  | Experi  | mental setup                                                  | 49 |

#### TABLE OF CONTENTS

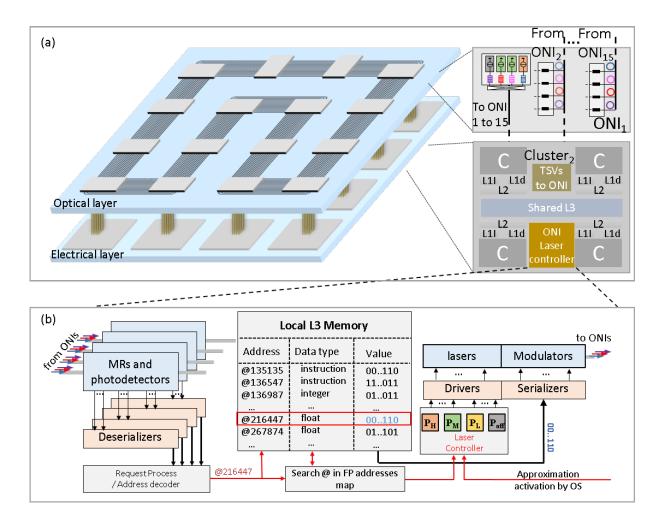

|   |      | 2.4.1   | Considered 3D architecture                                                                                               | 49 |

|---|------|---------|--------------------------------------------------------------------------------------------------------------------------|----|

|   |      | 2.4.2   | Approximation under cache coherence traffic                                                                              | 51 |

|   |      | 2.4.3   | Simulation setup and application                                                                                         | 51 |

|   |      | 2.4.4   | Benchmark traffic analysis                                                                                               | 52 |

|   |      | 2.4.5   | Optical link loss parameter                                                                                              | 54 |

|   |      | 2.4.6   | Input laser power vs BER                                                                                                 | 54 |

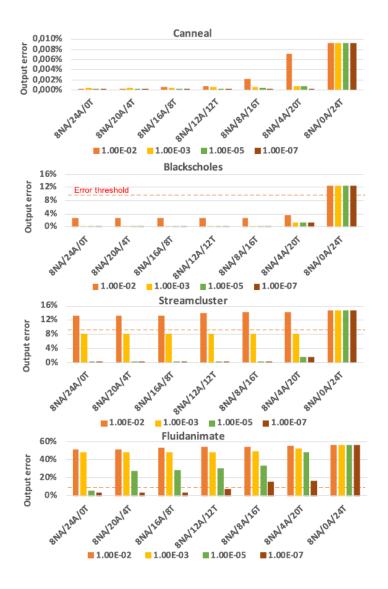

|   | 2.5  | Qualit  | by degradation case study of Benchmark applications                                                                      | 56 |

|   |      | 2.5.1   | Truncation impact on QoR                                                                                                 | 56 |

|   |      | 2.5.2   | Bit approximation impact on QoR                                                                                          | 58 |

|   |      | 2.5.3   | Mix of approximated bit and Truncation                                                                                   | 59 |

|   | 2.6  | Result  | s Power Saving                                                                                                           | 63 |

|   |      | 2.6.1   | Power saving                                                                                                             | 63 |

|   | 2.7  | Conclu  | usion                                                                                                                    | 65 |

| 3 | Dist | tance-a | aware approximate optical interconnect                                                                                   | 67 |

|   | 3.1  | Idea C  | Overview                                                                                                                 | 67 |

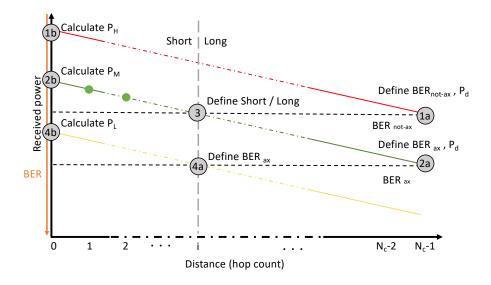

|   | 3.2  | Distan  | nce aware optical interconnect                                                                                           | 69 |

|   |      | 3.2.1   | Distance aware communication                                                                                             | 69 |

|   |      | 3.2.2   | Power consumption of Distance aware optical communication                                                                | 71 |

|   | 3.3  | Appro   | eximate distance aware optical communication                                                                             | 71 |

|   |      | 3.3.1   | Distance aware threshold definition on approximate interconnect $.$ .                                                    | 72 |

|   |      | 3.3.2   | Distance aware approximate interconnect data schemes                                                                     | 73 |

|   |      | 3.3.3   | Distance aware approximate interconnect power saving                                                                     | 74 |

|   | 3.4  | Laser   | design complexity                                                                                                        | 75 |

|   |      | 3.4.1   | Laser design complexity by number of controllers                                                                         | 75 |

|   |      | 3.4.2   | Laser design complexity according to number of transistors                                                               | 77 |

|   |      | 3.4.3   | Laser design complexity on power leakage and footprint constrain $% \left( 1\right) =\left( 1\right) \left( 1\right) $ . | 78 |

|   | 3.5  | Exper   | imental setup                                                                                                            | 81 |

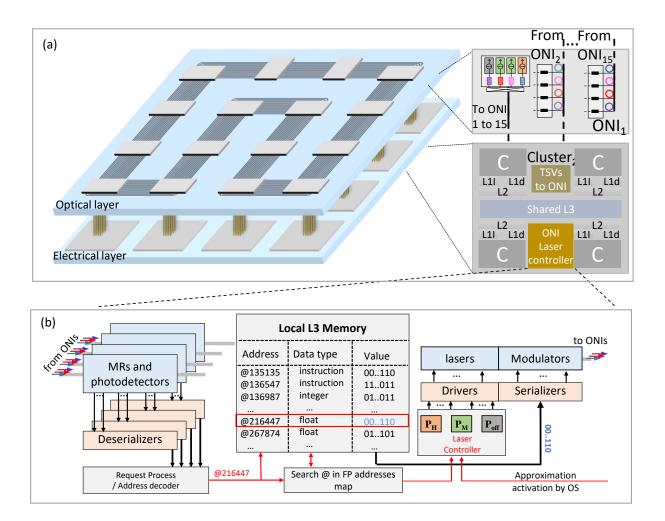

|   |      | 3.5.1   | Hardware implementation and communication model                                                                          | 82 |

|   |      | 3.5.2   | ONI specification                                                                                                        | 83 |

|   |      | 3.5.3   | Distance aware communication                                                                                             | 85 |

|   | 3.6  | Power   | Consumption Vs QoR                                                                                                       | 87 |

|   |      | 3.6.1   | Power saving analysis                                                                                                    | 87 |

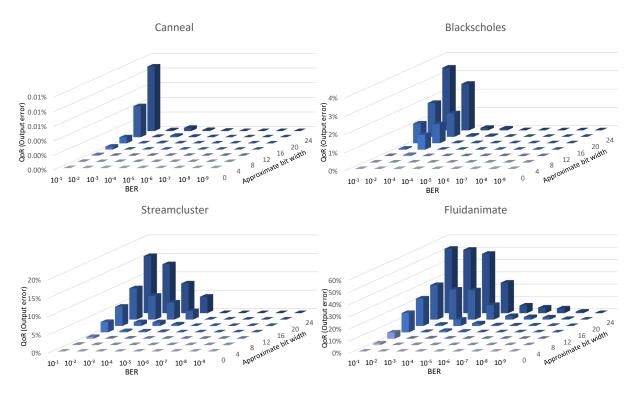

|   |      | 3.6.2   | Power saving vs. Quality of Results Trade-offs                                                                           | 89 |

|    | 3.7                    | Conclu | ısion                         | 92  |

|----|------------------------|--------|-------------------------------|-----|

| 4  | Con                    | clusio | n and Perspectives            | 95  |

| C  | onclu                  | sion   |                               | 95  |

|    | 4.1                    | Overv  | iew                           | 95  |

|    | 4.2                    | Perspe | ectives                       | 96  |

|    |                        | 4.2.1  | Optical network interface     | 96  |

|    |                        | 4.2.2  | Smart ONI                     | 97  |

|    |                        | 4.2.3  | Truncation and data insertion | 97  |

| Bi | bliog                  | graphy |                               | 99  |

| Li | $\operatorname{st}$ of | figure | S                             | 115 |

| Li | st of                  | tables |                               | 116 |

## INTRODUCTION

## Multi core era and System-on-chip

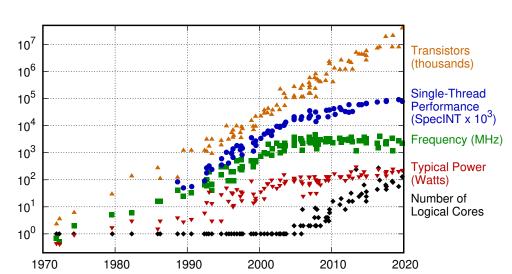

In computer history, the evolution has been swift: indeed, for several decades, the number of transistors in an Integrated Circuit (IC) is continuously doubled according to Moore's law [1]. Figure 1 presents this evolution over the years since 1970. In this graph, two interesting factors that indicate the evolution trend can be highlighted. First, we can see a steady increase in transistor density in the chip, which led to a successful results in single thread performance. It was possible thanks to engineers' efforts that increased the efficiency with nanotechnology systems whereby transistors sizes went from being millimeters to nanometers. This trend and effort allowed computer systems and chip engineering to continuously develop and, as a result, advance several technologies domains such as mobile, smart and innovative technologies, cloud computing, and robust computing. However, as the chip size is getting smaller and denser, it reacts to a high frequency more sensitively. This excessive frequency in the chip results in more power consumption, which leads to lowering the performance [2]. This significant power consumption in microprocessors becomes a real challenge to increase performance. Therefore, engineers had to find other solutions to keep following Moore's law further, in the end, to advance computer performance. For this reason, the strategy for improving performance changed, and designers started to increase the number of cores in the chips, as we can observe in Figure 1 since 2005.

This evolution is possible due to the continuous grow of transistor counts in the chips, allowing to increase the core number without modification of the frequency, leading to improve the global chips performance. Ultimately, this new trend led to Multiprocessor System-on-Chip (MPSoC) era to improve Single thread performance.

The recent studies show that SoC includes a large number of Intellectual Properties (IPs) such as cores, memories and hardware accelerators. However, the increase in number of IPs provoked a large amount of data transfers due to pipeline and multi parallelization. As a result, conventional communication links, such as buses and point to-point links, cannot ensure efficient communications. To address this problem, Network-on-Chip (NoC)

was suggested as a scalable solution to manage multi core communications.

Figure 1 – 48 years of Microprocessor Trend data based on [3].

Year

## Network on chip

Nowadays, MPSoCs are evolving towards the integration of hundreds of cores on a single chip [4]. More cores in the chip enables to the parallel execution of applications but increases the needs of communications between Intellectual Property (IPs). The early MPSoCs interconnects were designed in a bus or crossbar-based communication architecture [5]. The traditional bus architecture was built with dedicated point-to-point connections, with one wire dedicated to each Intellectual Property (IPs). The bus architecture could be employed, at first, due to its straightforward architecture allowing cost-effective and simple communication system. However, bus architecture performs effectively only when the number of cores in an MPSoC is low [6]. With an increase in SoC complexity dealing with the increasing number of cores, bus communication becomes a performance bottleneck, leading to problems like scalability, increased power consumption, wire delay, and increased verification cost. These constraints motivated engineers to define alternative solutions that can provide a scalable architecture.

New concepts for interconnects came from existing networking solutions, specifically the internet. In the internet, vast number of computers are connects and communicate to share information. Instead of connecting IPs in a link of bus or point-to-point connection,

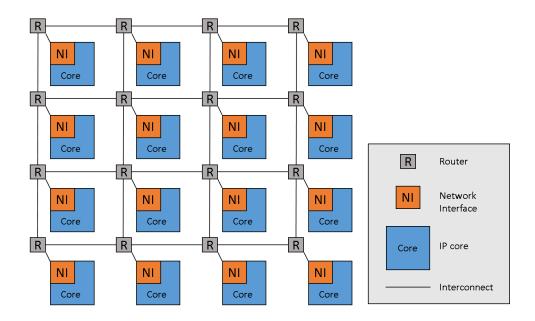

Figure 2 – NoC architecture.

IPs are connected and communicate throught network. This new paradigm is defined as networks on-chip (NoC) architecture. This solution can be seen as a miniature internet, and several existing network features and technology has been employed, such as routers, packet switching, and topologies. Therefore, more specific network techniques have migrated to NoC architecture, such as routing protocols, flow control, switching, arbitration and buffering [7, 8, 9, 10, 11].

Figure 2 illustrates very simple NoC architecture with its 4 main components: i) Routers, ii) Network Interface (NI), iii) Intellectual Property (IP), iv) interconnections. First, to handle the messages (packets) in the network, the router acts in the main role and supports network protocols and flow control. The routers are connected to each other with interconnects. The IPs in NoC can be various units such as memories, cores, accelerators, etc. Moreover, these IPs are connected through Network Interface (NI) to reach out to the network and send their messages/packets to other IPs.

Thanks to this simple implementation and management of several IPs in the network, NoC could be rapidly studied and could cope with increasing architecture size: scalability, resource reuse, performance, reduced costs, and design risk. Therefore, NoC became one of the praised solutions for the complex and large-scale SoCs that required a scalable interconnection architecture and communication system.

#### Importance of interconnect

As we could see in the previous section, current research and technology trends show that future MPSoC will embed hundreds or even thousands of processing elements. Moreover, as well as hardware system progresses, nowadays, applications like High-performance computing (HPC), Artificial intelligence (AI), scientific computing, video/image processing, data mining, and Big data applications are becoming more complex and sophisticated. This results in new workloads, such as pattern recognition, speech, video and text processing, speech and facial recognition, deep learning, and machine learning. These large-scale applications require high performance on a hardware system with a large amount of computation cpability and data exchange communications. To handle this a large amount of data and computation, communication models in multi-core architectures have been evolved by task parallelization and pipelining. These led to tremendous data packets movement in NoC by data aggregation, communication-intensive operations, and distributed computing. These communication overheads lead to overall system design concern for high-performance interconnects for high bandwidth communication.

This evolution leads to significant challenges for the design of efficient interconnect due to the ever-growing data exchange between processors [12]. The application requirement on hardware performance can only be achieved when architecture and technology developments provide sufficient chip-to-chip and on-chip communication performance to these massively parallel algorithms. In this context, the importance of on-chip interconnect design has become very important in terms of energy efficiency and link bandwidth [13]. However, conventional NoCs utilizing electrical interconnects are now facing challenges related to the end of the CMOS scaling, as it already costs more energy to move data than to compute them [13]. As the number of core increases in ENoC, the challenges of power consumption trend shift from computation bounding to data transfer bounding. This significant increase in the power dissipation of electrical interconnect becomes critical and leads to a power-hungry communication link. This power overhead requires alternate future interconnect solutions that can grant high bandwidth, low latency, scalability, and energy efficiency [14, 15].

The recent studies promote Optical interconnect is an attractive solution to address scalability issues in on-chip communication. The optical interconnect can offer low-power consumption, low latency, and high data rate and bandwidth compare to conventional electrical interconnect.

## Optical interconnect NoC

Nanophotonic interconnects, also called Optical NoC (ONoC), are based on optical signals for communications in NoC. Optical signals can propagate near speed-of-light in waveguides, and this feature can be a promising alternative solution to replace ENoC by providing large bandwidth and reduced latency.

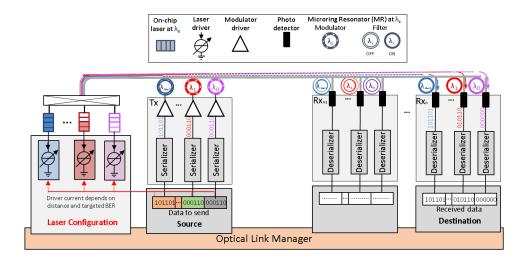

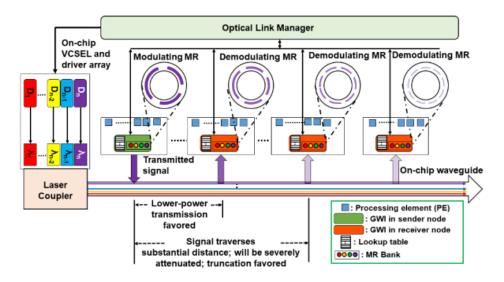

Figure 3 – Nanophotonic interconnect NoC Optical (ONoC)

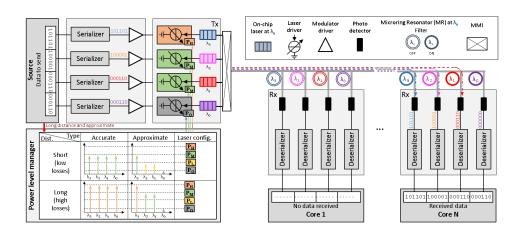

Figure 3 illustrates general ONoC architecture, which implements several photonic devices such as photonic waveguides, multi-wavelength laser sources, along with microring resonators (MRRs) as modulators and photodetectors. The laser sources (either off-chip or on-chip) generate light signals at specific wavelengths at the transmission side. The optical signals are modulated through wavelength-specific Microring modulators by on-off keying (OOK) modulation to encode the information from the electrical source node. The electrical signal is generally provided as parallel bits which are serialized as a sequence of 1 and 0 to control the OOK modulation. The signals can be modulated into one or several wavelengths to reduce the transfer time. The modulated signals propagate in a shared transmission medium waveguide through multiple wavelengths with wavelength-division-multiplexed (WDM). The WDM technique enables the transmission of several signals in parallel. The transmission of each wavelength serves as a carrier for a data signal. Then, the optical signal propagates in the waveguide until the destination. When they reache the destination, the optical signals are filtered out via a serie of microring (MR) filters, which extract the targeted wavelengths of light and drive them toward

photodetectors. The photodetectors allow to convert optical signals intop electrical ones to forward them to the associated nodes (e.g., processing cores) on the chip. Each node in the ONoC communicates to multiple other nodes through Signal Writer and Multiple Reader (SWMR) communication model with WDM-enabled photonic waveguides.

## Challenges of ONoC

Silicon photonics interconnection can offer advantages such as low transmission latency and high bandwidth. However, their implementations remain challenging due to several reasons;

- First, the lasers, which are key device in ONoC, suffer of low efficiency. Indeed, the laser power consumption is mainly due to the low optical gain, which needs to high electrical current. Therefore, the laser power dominates overall power in optical interconnect.

- The emitted optical signals suffer losses as they propagate through waveguides. To ensure that the optical signal at destination has sufficient power for error free transmission, it requires a high laser power to compensate such losses, so that the signal can be received at the destination node with sufficient power to enable error-free recovery of the transmitted data.

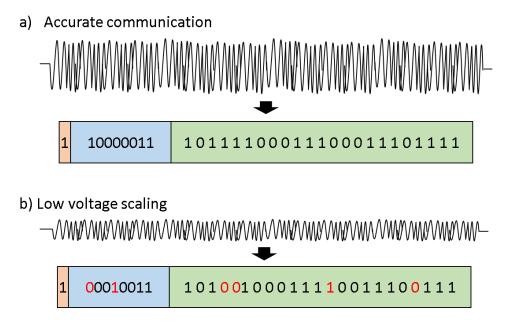

Therefore, in this thesis we focus on improving the energy efficiency of the photonic interconnection by adapting approximate computing in optical interconnect to improve efficiency of the laser power consumption, taking into account the distance losses and the targeted bit error rate (BER) for the communications. In addition, the trade-off between energy efficiency and performance communication is also explored.

### Contributions

This work improves the optical interconnect based on realistic and scalable laser power management. First, we propose improved approximate communication, and we investigate bit approximation and bit truncation to reduce the NoC power consumption. We also propose to associate of these two techniques for each data communication to yet improve the

global system performance. This allows further design exploration and achieving a point closest to the optimal one in terms of power consumption. Thus our proposal provides more power saving with tunable output error. This optimization of approximate configuration makes optical communication more robust and energy-efficient while adapting the error tolerance of the application. Secondly, we propose laser power management based on a technique taking into account the communication distance. Our proposal is based on the communications classification by their distances between source and destination cores. However, unlike [16], only two distances are considered: short and long-distance ranges. This allows laser power configuration to be more suitable and realistic for various architectures in terms of design effort and energy efficiency.

### Approximate communication in ONoC

We propose an approximate nanophotonics interconnect. Our proposal is applied to transmit Floating-Point (FP) numbers in Single Writer Multiple Reader (SWMR) optical channels. It relies on the transmission of the least significant bits (LSB) using low-power optical signals, at the cost of higher error rate. These approximate optical signals allow a drastic reduction in the laser power consumption. In parallel, to ensure the communication accuracy on most significant bits (MSBs), the laser power levels are remained using high power signals. Moreover, this transmission model allows estimating the laser power according to the targeted BER and a micro-architecture allows configuring at run-time, the number of approximated bits and the laser output powers. This homogeneous multi level transmission allows exploring robustness and energy efficiency trade-offs for on-chip optical interconnects. Simulations results demonstrate that, compared to an interconnect involving only robust communications, approximations in the optical transmission lead to up to 42% laser power reduction for Streamcluster application with a limited degradation at the application level.

#### Distance-aware in ONoC

We propose a distance aware approximate nanophotonic interconnect to reduce power consumption of the NoC supporting the on-chip communications. As fine-grain distance-aware management of communications is too costly, we propose a low overhead distance-aware technique based on 2 distance classes defined through a threshold. Instead of analyzing each source and destination losses to configure input laser power level, our proposal

considers only two distances of communication: short and long-distance ranges. The laser power level for long distance is defined with farthest destination from source to target a given BER. The short distance is defined with one of the intermediate destination. Based on this classification, laser power levels are adapted according to the distance and targeted BER that application requires for error tolerance. short/long distance configuration might not be a most optimum in terms of power consumption, however, it is realistic design for laser power level configuration and laser driver complexity. The results of evaluation for the proposal show drastic laser power reduction of 53% for example for Streamcluster application at the cost of less than 8% of errors. Finally, we show that our solution is scalable and outperforms state of the art solution as follows: 10% reduction in the total energy consumption, 35x reduction in the laser driver size and 10x reduction in the laser controller size.

## Thesis outline

The rest of the manuscript is organized as follows:

- Chapter 1: Related work presents state of art of the Silicon photonics interconnect in NoC with detail of its components. In the following, the concept of approximate computing is also introduced to understand error tolerant applications and various techniques of approximate computing. For the last, state-of-art of approximate interconnects is presented.

- Chapter 2: Approximate communication in Optical Interconnects the idea of our first proposal in detailed with optical link hardware setup that we have utilized. It also contains simulation setup like benchmark applications and study of each application characteristic. For the last, the results of quality impact and power saving are stated.

- Chapter 3: Distance-aware approximate optical interconnect This chapter includes the study of laser driver complexity to compare with state-of-art and introduces multi laser power levels to increase the energy efficiency in NoC. Then, the results of our proposal are presented with comparison of state-of-art.

- Chapter 4: Conclusion & perspectives This chapter abstracts our contributions and presents a set of perspectives for future works.

## RELATED WORK

In this chapter, an overview of two domains is presented. First is introducing silicon photonics and its implementation as an NoC interconnect. Then, we address fundamental of optical interconnect with a simple link model and illustrate how it operates and its limitations, in particular, cross talk problem coming from the WDM technique. Secondly, we present the concept of approximate computing, and we explain how this concept has been extended into approximate communications.

## 1.1 Silicon Photonic interconnect NoC

Optical interconnect enabled by silicon photonics is praised as a promising solution for the communication bottleneck in NoC. This communication phenomenon in the data-centric era emphasizes the prominence of interconnects due to the rapid expansion of the data volume of communication. In this section, the background and property of optical interconnects are briefly introduced, and we identify several challenges to motivate our work and the scope of this dissertation.

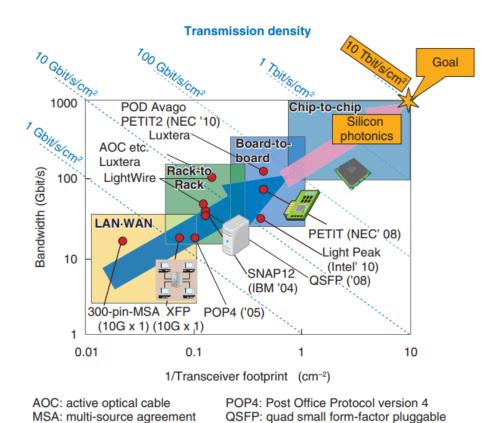

## 1.1.1 History and introduction of optical interconnects

As Optical interconnects utilize optical signals as an signal carrier, it brings several benefits, such as higher bandwidth capacity, low propagation delay, and greater tolerance of electromagnetic interference compared to conventional electrical interconnects [17, 18]. Therefore, optical links are broadly explored as a substitution for electrical links. Over the past decades, this type of optical interconnect has evolved from long-distance communication to short-distance communication, as illustrated in Figure 1.1. It shows bandwidth and the footprint of interconnect modules. In this figure, the bandwidth and footprint of optical solutions are highlighted and express the opportunity of this technology for different application domains.

Conventionally, Optical interconnect modules were used for applications like LANs (local area networks), WANs (wide area networks), inter-rack, and on-board interconnects. As we can see in Figure 1.1, in LAN and WAN networks have  $1Gbit/s/cm^2$  for long distance. When this optical communication comes to board-to-board communication, it can offer  $100Gbit/s/cm^2$ . These interconnect are based on discrete photonic devices made of compound semiconductors and photonic technology which has utilized large components. Therefore, the optical interconnect technologies could not directly be used for photonic integration within chip-to-chip communication.

The chip-to-chip interconnects evolve with Complementary metal-oxide-semiconductor (CMOS) circuits, and it requires very high-end technology due to its device size, design scheme, and materials. To solve these problems, silicon photonics technology was proposed through close electronic-photonic integration for high bandwidth communication and high energy efficiency. The silicon photonic system can achieve high-density photonic device integration and compatibility with CMOS electronic technology that targets  $10Tbit/s/cm^2$  and even higher bandwidth.

#### 1.1.2 Components of silicon photonic interconnect

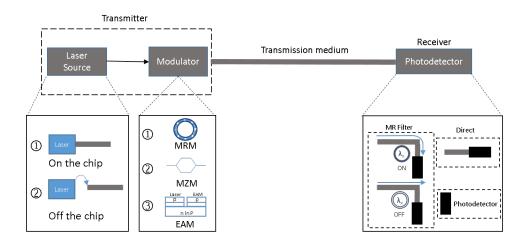

Silicon photonic utilized the nano size technology that enables to be compatible with CMOS technology. In silicon photonic interconnect, there are various scenarii of component options that are possible. Figure 1.2 presents a very elementary and high level optical link with optical components blocks in a very general point of view.

For a communication system, the communication link contains three essential block parts: **A transmitter block** that gets information from upper layer and converts this information into physical signal, **a transmission medium block** that conveys the signal, and **a receiver block** that receives the signal and converts into information for upper layer.

**Transmitter block** it contains components like i) laser, which is source carrier of optical signal as light wave, and ii) modulator, which encodes the information data from electrical domain into bits ("1" or "0").

— **Laser source**: The main role of the laser is to generate light signal. In order to have optimum optical link, we need to have right amount of laser power, so we do not waste the power or have bad communication quality. By injecting and adjusting the

Figure 1.1 – Evolution of optical interconnect [19].

Figure 1.2 – Optical communication Block.

laser power, we can configure the power just necessary on laser. Two main locations can be found for the optical signal generation: on chip and off chip laser. Previously there are several studies that compare these two solutions with comprehensive analysis and discussed the merits and flaw of these two lasers [20, 21, 22, 23]. Compared to on-chip laser, an off-chip laser provides higher efficiency on light emitting and better temperature tolerance but it suffers from a large coupling loss, a large area and packaging cost. On the other hand, on-chip laser offers better integration in terms of area and design constrain. Therefore, when it goes to large scale NoC, on-chip laser performs better in scalability and flexibility for implementation of optical link. Therefore, considering these advantages, we consider on-chip laser implementation as an hypothesis for our works.

— Modulator: there are several modulation methods for the light signals: microring modulator (MRM) [24], Mach-Zehnder modulator (MZM) [25, 26] and electroabsorption modulator (EAM) [27]. Compare to other modulation model, Microring modulator provides more energy efficient due to its compact size property and easy control on optical signal. Moreover, microring modulator offers the inherent wavelength selectivity and allows wavelength division multiplexing (WDM) which can be evolve to higher dense wavelength division multiplexing (DWDM). In this thesis, we utilize MRM as the primary device for our high-speed communication link due to its energy efficiency and wavelength selectivity. The detail role of MR will be stated in section 1.1.3.

After modulation, the signal is injected into the transmission medium block to send the information.

In the block of **transmission medium**, the optical signal propagates from transmitter to receiver. Optical interconnects utilize the waveguides for signal propagation. Unlike electrical copper wire from electrical interconnect, in optical interconnect, it is possible to transmit several optical signals in a single waveguide by applying wavelength division multiplexing (WDM). WDM allows multiple signaling by simultaneously transmits signals in one transmission medium. Furthermore, several wavelength-specific lasers are allocated to support the multiple wavelengths emissions. In WDM, several wavelength-specific MRMs are placed on a shared waveguide, which allows to modulate wavelengths

individually. Moreover, the WDM signals at specific wavelengths can be extracted independently from the waveguide at receiver side. In order to avoid interference and crosstalk noise with another wavelength channel, MR should have a small ring diameter to create a large FSR, offering important wavelength spacing [28, 29]. WDM can effectively improve throughput to Gb/s and Tb/s for link bandwidth, and ease area overhead compared to single wavelength channel. However, several optical signals in one waveguide can provoke crosstalk noise that can critically distort the information in signals. The detail of crosstalk noise in WDM is detailed in 1.1.4

At the end of transmission medium, receiver block wait for the optical signal to be arrived and extract the optical signal.

At receiver block, several components and scenarii are possible, such as a photodetector and/or microring filters to convert optical into electrical one and extract the signals from waveguide. In the case of using array of mirroring filters, mirroring can extract the light signals selectively at specific wavelength. Utilizing MR filters allows to have several receivers (destination cores) in single waveguide. To reach a given destination, all the intermediate IPs set their MR in OFF-states, so optical signal continue to propagate until the right destination. When transmitted signals arrive at destination, MR filters are set to ON-state and extract the signals to drop port waveguide. At the end of drop port, photodetector is integrated to convert optical signals into electrical ones. In MR filter receiver can have multiple receiver but as MRs are arrayed at the receiver side, we also have to consider other loss which are introduced by several MRs, such as MR through loss and crosstalk noise between the wavelengths at the drop of microring filters.

In case of direct receiver which uses photodetector at the end of waveguide can have only one destination in one waveguide. This direct receiver offers simple implementation and control on network interface as it does not require MR filter controls.

For both cases, photodetector is used. Typically photodetector perform with a photodiode to sense the received optical signal and produce an input current. This current which is induced by the optical signal, is called photocurrent. In photodiode, photocurrent is converted to voltage and amplified sufficiently for data resolution. The photodetector performance is determined by its sensitivity, which is associated with the maximum data rate and amount of tolerable channel loss.

#### 1.1.3 Physical property of optical components

In previous subsection, we saw several components of optical link. In this subsection, we detail the component's physical properties and how it operates. When a light signal propagates into the waveguide, there are several intrinsic and indirect loss from optical components. To design optimum and efficient optical link, there is a need to understand the devices.

At the beginning of optical link, the laser is located. It emits the light signal into the waveguide and acts as main role of light source. Our study is based on utilization of **on-chip laser** which provides flexibility and straightforward power level configuration accessibility. In particular, vertical Cavity Surface Emitting Laser (VCSEL) is an attractive on-chip optical laser source for short-distance optical interconnects. It offers compact size, the short rise time of VCSEL current, and high switching frequency [30, 31]. VCSEL laser emits an optical signal from its surface to the wafer. Additionally, multiple VCSEL lasers can be positioned in an array due to their direct emission into a wafer. Moreover, VCSEL is able to target several different wavelengths, which is suitable for WDM [32]. In the study of [33], devices can emit at around 850nm at large substrate with high speed-optimized VCSEL technology. In [34], the proposed VCSEL can support the variation and thermal analyses and emit optical light at BER under 10<sup>-9</sup> with laser efficiency equal to 33%.

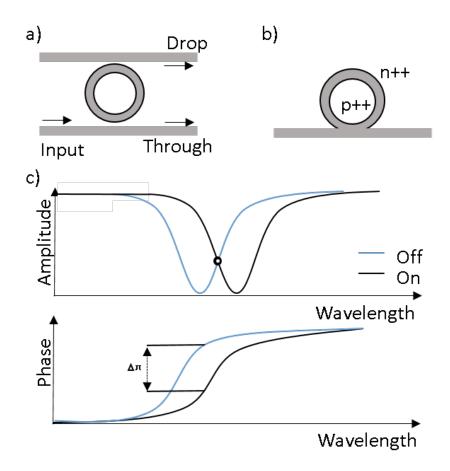

- Microring Resonator: MR can be used in several place in optical link i) as a modulator at transmission part and ii) as MR filter at receiver part. MR can offer the inherent wavelength selectivity and allows wavelength division multiplexing (WDM) which can be evolve to higher dense wavelength division multiplexing (DWDM). Therefore, in this thesis, we utilize MR as the primary device for our high-speed link due to its energy efficiency and wavelength selectivity. Figure 1.3 presents MR in NoC in very general high level point of view. Figure 1.3 a) illustrates MR with an input and a drop waveguide. There are two possible scenarii; first, when MR is activated, the light signal from the input waveguide is redirected to the drop waveguide through MR. Secondly, when MR is deactivated, the light signal continue to propagates to through port waveguide from input port. Figure 1.3 b) presents p and n doping on MR to understand electro-optic MR for on-off keying (OOK) modulation. When MR is activated the current is induced at MR to p and n doping and it extracts optical signal from the waveguide then the waveguide silicon index changes. This leads to resonance wavelength shift, achieving on-off keying

modulation. Figure 1.3 c) shows wavelength shift at targeted resonant wavelength  $\lambda$ . When MR is activated, there is not only wavelength shift, but also there is the phase response of MR.

Figure 1.3 – Microring modulator a) General implementation of MRM; b) P and N doping in MRM c) states of MRM considering the drop out and pass through mode.

Now let's take look how MR actually operates.

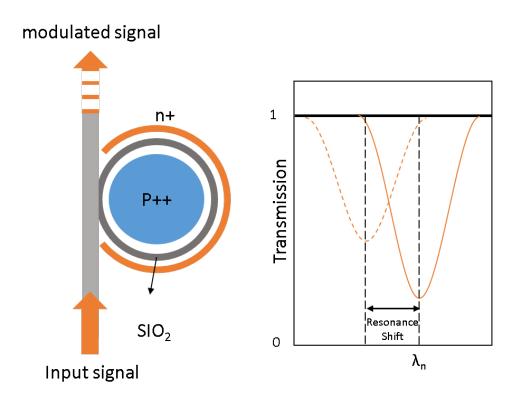

First, as a modulator: in our study Microring based modulator is used for optical signal modulation [35]. Figure 1.4 presents the MR modulator that consists of a microring resonator coupled with a waveguide. By tuning the MR index properly the resonance in wavelength is shifted, which induces a strong modulation of the transmitted signal. The MR index is modulated electrically by injecting electrons and holes using a p-i-n junction embedded in the microring resonator. By turning on MR, the refractive index is adjusted by applying the bias voltage on the modulator. The equation 1.1 describes the optical

Figure 1.4 – Microring modulator.

response of a microring, where L is the optical length of the microring,  $\alpha$  is the loss in the cavity, and t is the transmission coefficient.

$$\frac{E_{out}}{E_{in}} = \frac{-\alpha + te^{-2\pi Li/\lambda}}{-\alpha t + te^{-2\pi Li/\lambda}}$$

(1.1)

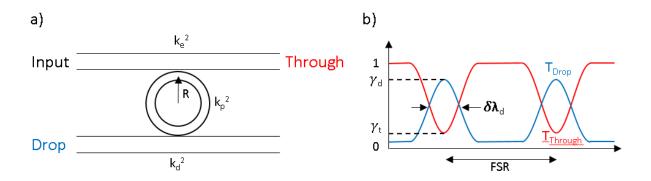

Second, MR at receiver: MR also can be used at the receiver side as a drop filter by targeting specific wavelength. Depending on the communication channel model, the bank of MRs can used to extract specific wavelengths. It extracts the light signal from waveguide at targeted wavelength and redirects the signal to drop port which leads optical signals to photodetector. Figure 1.5 a) presents microring resonator (MR) with an input and a drop waveguide. Figure 1.5 b) illustrates power transmission responses of waveguides. When MR filter is activated, input light power at through port is redirected to drop port transmission power. To understand the power rate between input power from waveguide and drop port, Figure 1.5 a) illustrates MR resonator with its coefficient. Figure 1.5 a)

Figure 1.5 – Microring modulator.

can be presented in equation 1.2, with the coefficient of each fraction of the input optical power, fraction of light filtered in drop port and intrinsic power loss in MR respectively  $k_e^2$ ,  $k_d^2$  and  $k_p^2$ . FSR is the free spectral range (in wavelength span) in the resonator.  $\delta$  is  $\lambda_M R/2Q$

$$\frac{P_{drop}^{\lambda i}}{P_{in}^{\lambda i}} = \left[\frac{2k_e k_d}{k_e^2 + k_d^2 + k_p^2}\right]^2 \frac{\delta^2}{(\lambda_i - \lambda_{MR}) + \delta^2} \tag{1.2}$$

Figure 1.5 b) presents the transmission power between drop port and throughput waveguide. The minimum power transmission in the through port is  $\gamma_t$  at the resonance wavelength  $\lambda_0$ . On the other hand, at resonance wavelength  $\lambda_0$ , drop port waveguide transmission power reaches at high power  $\gamma_d$ . This leads to add-drop crosstalk  $-10 \times log 10(\delta \lambda_d / \delta_t)$  in dB.

- Waveguide: Like copper wire in electrical interconnect, when light signal propagates through the transmission medium, the propagation loss occurs. The loss in the waveguide can be caused by several attribute factors like light scattering, absorption, radiation loss from waveguide bending. Waveguide propagation loss is mainly due to surface scattering from the etched sidewalls. When optical signal propagates, it suffers attenuation from each reflection on the waveguide wall. The free-carrier effect can cause the absorption loss by electrons or holes in the waveguide. Furthermore, the temperature of the waveguide can increase this loss. These losses are intrinsic loss which is a physical characteristic of a waveguide. Minimizing the optical signals and the frequency that signals touches the etched interfaces can effectively reduce the waveguide propagation loss.

In [36], the authors propose to increase the waveguide width and decrease etch depth. In [36], loss shallow-ridge silicon waveguides are demonstrated with an average propagation loss of 0.274dB/cm.

Photodetector: the photodetector receives the optical signals which redirected from MR filters. The photodetector converts light photons into electrical current. The absorbed photons make electron—hole pairs in the depletion region. Photodetectors often contain Ge or SiGe due to their compatibility with CMOS process [37, 38]. SiGe photodetector performs with better sensitivity for shorter wavelengths than Ge photodetectors. SiGe is developed for standard CMOS processes as a strain-engineering material to improve the carrier mobility, enabling monolithic integration of silicon photonics without any requirements at CMOS process. The sensitivity of photodetector is the main factor to consider for optical link budget. The sensitivity refers to the least optical power at the destination to achieve targeted BER [39].

#### 1.1.4 Crosstalk noise in WDM

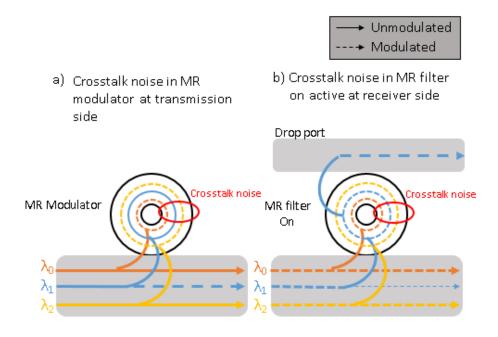

We saw MRs that are used at both transmission and receiver side to realize modulation and multiplexing/demultiplexing of optical signal at designed optical wavelength. Moreover, the optical signals in MR can have multiple channels through out wavelength division multiplexing (WDM) which allows high bandwidth communication. However, in WDM links, channels tend to correlate and imprint negative effects on each other, such as spectral overlap of adjacent channels and polarization modes. These crosstalk effects can be found prominently where multiple MRs are employed to add or drop individual channels to or from a WDM signals (Inter-channel crosstalk) and when frequent switches appear between several channels of the same wavelength (intra-channel crosstalk). These significant signal distortion might lead to misinterpretation and affect link quality performance for high BER. Figure 1.6 presents crosstalk noise at MR in SWMR communication link using WDM. In this Figure three different wavelengths ( $\lambda_0$ ,  $\lambda_1$  and  $\lambda_2$ ) are used in one shared waveguide medium. We assume the wavelength  $\lambda_1$  as a selected communication channel for both modulation and receiving signal. Figure 1.6 a) presents crosstalk noise in MR modulator. When MR modulates at specific wavelength ( $\lambda_1$  in Figure 1.6) the other wavelengths  $\lambda_0$  and  $\lambda_2$  are also drained into the MR and these signals provoke the crosstalk noise. Figure 1.6 b) illustrates crosstalk noise in MR filters in active mode. The MR filter out the  $\lambda_1$  to drop port, but small partial optical power leaks into MR and induces crosstalk noise. If the channel space between the wavelength is large enough, in drop port, the crosstalk noise which introduced by signals in different wavelengths is very low and can be negligible.

Figure 1.6 – Crosstalk noise in SWMR.

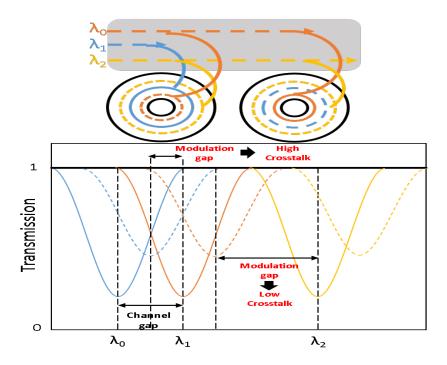

Even though MRs can selectively modulates signal using WDM, the signals that have different wavelength can be affected by MR and provoke crosstalk noise. Moreover, in WDM MR modulators are located in an array, the neighbor MRs provoke the crosstalk noise and suppress the signal power. The power of this distortion can be increased by number of different wavelength in shared medium and the channel space between them. Figure 1.7 illustrates transmission spectrum of bank of receiver resonance wavelengths of MRs with three different wavelengths ( $\lambda_0$ ,  $\lambda_1$  and  $\lambda_2$ ). In this Figure, we can see the channel gap and modulation gap for all the wavelengths. The Figure shows two MRs which drop the optical signal at each wavelength  $\lambda_0$  and  $\lambda_1$ . In the transmission spectrum figure we can see that  $\lambda_0$  and  $\lambda_1$  are neighboring wavelength which means the channel gap between them are very close. This near wavelength modulation can lead to high crosstalk noise. To reduce the crosstalk, designing larger channel spacing between the wavelengths are essential. For example, in the figure we can see that wavelength  $\lambda_2$  has less impact on  $\lambda_0$  which lead to less crosstalk noise. Indeed, the dense WDM can provide high bandwidth

with multiple channels. However, it can also contain large amount of crosstalk noise and might interfere the signals and distort information.

Figure 1.7 – Crosstalk noise between MR modulators.

Figure 1.8 shows crosstalk noise by the number of wavelength in same spectrum range. The first and last nodes (MR) have very low crosstalk noise due to 1 less adjacent neighbor on side. Other intermediate nodes have more MR modulator crosstalk noise. Moreover, as the number of wavelengths  $\lambda$  increases in the same spectrum range, the crosstalk noise increases due to shorter channel gap. Therefore, in WMD, the channel spacing is one of the main design concern to avoid high crosstalk noise. In our work, we set the FSR and channel spacing at 8nm and 1nm (120 GHz) respectively with 8 channels (wavelengths) to avoid crosstalk noise [41].

## 1.1.5 Optical link and ONoC architecture

As we saw from previous subsections, there are many options to define an optical link configuration. Based on our study, we choose the specific implementation of the optical link model as Figure 1.9.

Without lack of generality, as presented in Figure 1.9, conceptual diagram of optical

Figure 1.8 – Crosstalk noise by number of wavelengths [40].

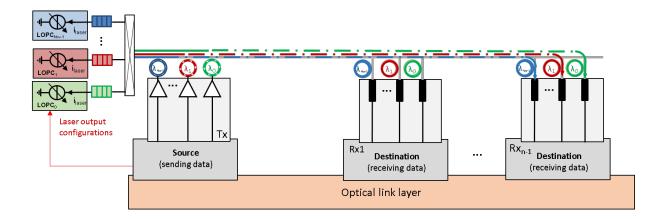

link communication to show how information is transmitted. In Figure 1.9, three IPs connected with silicon photonic interconnect, which is consists of i) on-chip laser and MR modulator at the transmitter side, ii) SiGe Waveguide as transmission medium iii) at the receiver side, microring filter and photodetector are located. When the transmitter side receives information from IP, the laser controller turns on the laser at each wavelength  $\lambda_{N-1}$  by WDM communication, at moderate input power. Then, MR modulator encodes the incoming light signal with on-off-keying (OOK) at selected laser wavelength  $\lambda_{N-1}$ . The modulated optical signal propagates through the waveguide and there might be the another passing IPs in SWMR (Rx1 in Figure 1.9). The signals propagate in waveguide and reach at the destination. At the receiver, the bank of microring filters placed to filter out the received optical signal at a specific wavelength. The drop port of the optical filter is connected to a photodetector to convert optical signals into electrical signals. Moreover,

besides the optical component model, we also have to consider the communication link model to connect several IPs in one shared transmission medium [42]. There are several possibilities that have different pros and cons. A very simple communication model is the Single Writer and Single Reader (SWSR), which links just one transmitter (writer) and one receiver (reader). This communication model connects each IP at a point-to-point connection, just like copper wire. It performs the best in terms of latency and energy

Figure 1.9 – Modeled Optical interconnect Noc (ONoC).

Figure 1.10 – Communication link models a) SWMR b) MWSR c) MWMR.

consumption, as it does not consider link contention and provides direct communication link. However, this communication model is not scalable due to area constrain and density.

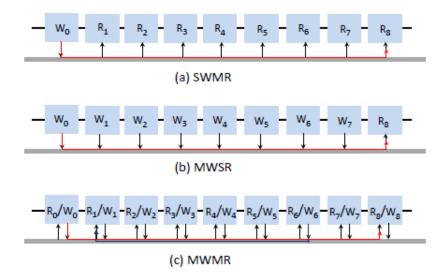

Therefore, there are communication models that utilize multiple signaling in shared optical links to increase the efficiency of area constrain through WDM. These models are the Single Writer and Multiple Reader (SWMR), Multiple Writer and Single Reader (MWSR), and Multiple Writer and Multiple Reader (MWMR). MWSR communication model employs a local arbitration at the writer side before sending data to reserve the link to a single reader as proposed in Corona [43]. The Corona offers a high bandwidth DWDM crossbar, enabling a cache coherent design with near-uniform on-stack and memory communication latency. MWMR model optimizes the link utilization and scalability in terms of area constrain by fully sharing the channel with all the connected IPs as both writers and readers. The link contention between writers and readers is regulated by arbitration strategy [44]. However, in MWMR, the optical signal undergoes many optical devices, which leads to high optical losses. These losses from various optical devices result in high optical input laser power to meat targeted BER and suffer from power efficiency. Moreover, there are more complex model, like Dragonfly [45, 46] which combine communications models. Dragonfly architecture supports multicast and broadcast traffic in a simple and efficient way with its low diameter. The proposed architecture uses group of high-radix routers as a virtual router to increase the effective radix of the network. However, by creating groups, it relies on indirect adaptive routing and multiple global channel traversals, leading to additional complexity and increased hop count.

In this thesis, we consider SWMR as communication model as it avoids global arbitration between writers and minimizes the complexity of communication control [47, 48]. This model might not be a most energy efficient and scalable model, but it provides low-latency and high-bandwidth.

## 1.1.6 Energy efficient challenges in optical interconnect

Even though optical interconnect can offer several benefits like high bandwidth and low latency to NoC, it suffers from high power overhead related to low-efficiency lasers at its integration. Therefore, to overcome this problem, several attempts have been proposed to improve optical interconnect power efficiency. The energy efficiency of ONoC is addressed in several aspects. At the circuit level, in [49], the authors proposed to reduce the power loss, which comes from components such as by reducing the number of Micro Ring resonators (MR) and waveguide crossings. At the communications level, communi-

cation scheduling can improve energy efficiency thanks to less parallel communications leading to crosstalk and energy penalties [50, 51].

In [49, 52], an all optic interconnect topology suitable for managing optical communications is proposed. It is based on routers that reduce number of wavelengths and other optical components to reduce power consumption. In [53], the authors propose photonic on-chip network architecture composed of several sub-nets. This allows high performance and low latency by sharing optical channel between sub-nets and by dynamically schedule them without degrading throughput. Error correction code (ECC) is introduced in Optical NoC to reduce the power consumption [54]. The transmitter includes an ECC and the receiver detects faulty bits and can then correct them. Since additional faulty bits are acceptable using ECC, the optical power emitted by the laser source can be significantly reduced. In [55], the authors propose crosstalk aware wavelength scheduling. The correlation of application execution time and the energy consumption overhead is strategically analyzed to reduce the crosstalk induced by WDM (Wavelengths Division Multiplexing). In [50], the contribution focuses on dynamic bandwidth scaling based on network traffic prediction. It dynamically tunes optical channel link according to the needs of bandwidth. By turning off the unused network link, it optimizes channel utilization and reduces optical power. The technique consists on configuring the optical light intensity based on the number of paths used in a tree based optical NoC. In [56, 57, 58], based on network load of required by applications, the authors propose a network management. In [56], the authors propose to increase the laser power efficiency through the management of online activating and deactivating of L2 cache and the associated optical links. In [57], the off-chip laser power is dynamically managed at runtime to adapt the network to application characteristics, hence reducing laser power consumption. the work published in [59] proposes heterogeneous multicore architecture based on CPU-GPU cores. It reduces static optical power by predicting network load with link reservation. In [60], the authors propose to runtime power management using token based time division multiplexing. It switches ON/OFF laser source according to NoC bandwidth needs. In [61], the authors propose to balance the power consumption of lasers and the average packet latency on the ONoC. This is done by optimization of the photonic link parameters at design time, and by on-line trade-off management of power consumption and performances by limiting the cross-talk effects involved by the Microring Resonators.

#### 1.2 Approximate computing

#### 1.2.1 Introduction

Since the beginning of the computing system history, accuracy and reliability have been a fundamental concern for computer performance and hardware design. The computer user expects that the computer system is reliable for accurate computing and no error in communication and data management. Therefore, to prevent error in the computing system, several works are considered, such as the error detection and error correction techniques are proposed: checksum, forward error correction, and parity bit [62, 63, 64]. However, this desire for perfection might be abstract and the cost of these additional techniques is too high and sometimes not affordable.

Meanwhile, many applications do not intrinsically require perfectly accurate computation and are tolerant to errors. For example, applications like computer vision, media processing, machine learning, and sensor data analysis can cope with inaccurate information in their design [65, 66]. There are several reasons behind this tolerance with imprecision: in computer vision and image media-processing applications, sometimes the quality of output results might not be defined and vary depending on users. The output of these applications is observed by human eyes that contain perceptual limitations. There might not be an exact solution in the machine learning domain and no output result that the program is looking for. The purpose of the application is often just a suggestion to users for the best match, or it might not need to guarantee finding one unique solution. The output result can be good enough to satisfy the users. In an applications that use censored data, the input data already contains the noisy elements, which means the input data are robust to noisy and application can produce approximated output.

Nowadays, large-scale applications such as scientific computing, social media, high-performance computing, and big data applications demand modern systems with significantly high computational and storage. The capacity of hardware systems has far exceeded the available resources to fulfill the application demands. The promising solution for this dilemma is Approximate Computing (AC), which bases on exploiting the system's inherent error resiliency and tolerance to achieve energy efficiency. Instead of performing an exact computation or maintaining accurate quality, Approximate Computing allows prudent approximation or partial offenses in specification to advantage in several aspects like; efficient computation, communication power consumption, memory architecture, and better throughput by drastically reducing the computation or data accuracy quality.

Figure 1.11 – Approximate computing applications.

Depending on where approximate computing is employed, it offers different benefits to the system. Well-known domains that adapt approximate computing are approximate arithmetic circuits:

- Approximate adder and multipliers

- Energy-efficient memory

- Embedded sensors for IoT applications

- An accelerator of Neural Network

For instance, approximation allows reducing the hardware complexity of arithmetic circuits such as adder and multiplier [67, 68, 69]. An approximate circuit contributes to the improvement of power consumption and operating speed. It also provides efficient power consumption and more effective memory management [70, 71, 72, 73]. Approximate memory architecture offers data storage with a predefined accuracy level to offer compact data storage and read/write power efficiency of memory. The work of [74, 75, 76] proposes to apply approximate computing on the Internet of Things (IoT) and sensors domains. In IoTs, sensors already contain sensing noise and inherent error-resilience in signal processing and based on redundancy in the input data. These lead in degradation of result quality and inefficient power consumption. Hence, the proposed approximate sensor leverages the approximate computing in digital sensing through low-power approximate circuits and data aggregation algorithm to provide energy efficiency. In [75], the authors propose approximate sensor which leverages the approximate computing in the real-time encoding

scheme that performs iterative threshold and approximation of wavelet coefficients for sparse encoding, thereby reducing the energy and bandwidth. Approximate computing can be applied in Neural Network by considering approximation data for both in computation and memory accesses, thereby achieving more energy savings [77, 78, 79]. The work presented in [78] proposes data pattern matching to reuse approximatly similar data in Neural Networks. It performs approximate computation reuse with relaxed precision at input patterns and designs a reconfigurable architecture to support the approximate computation reuse. It could reduce energy by 30-58% with accuracy degradation of 1-2.5%. In [80], 19-bit approximate floating-point mantissa bits are utilized with an approximate adder to achieve power saving. It not only speed up the computation, but also save the power consumption on memory and communication link.

#### 1.2.2 Floating-point Data representation

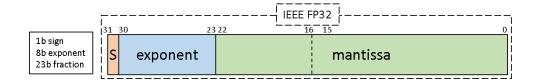

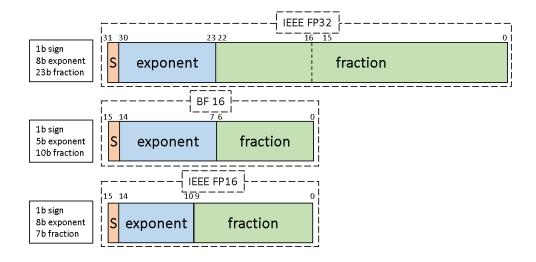

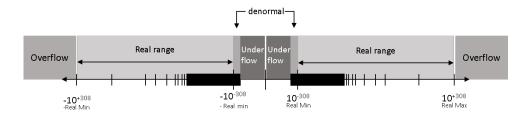

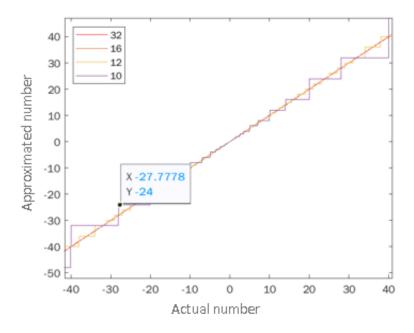

In computer arithmetic, the representation of real numbers is one of the major concerns due to their accuracy, reliability, and stability. However, in arithmetic computing, an infinite accuracy and number representation are impossible since the numbers consist of finite bit width. Therefore, the numbers are formed in various ways: singed/unsigned integer, fixed-point and floating-point. This thesis explores the floating-point data presentation, its approximation, and the impact of number representation. To have a number representation as accurate as possible for all the numbers ranging from very small to large numbers is significantly important. To address this problem, the IEEE 754 standard defined [81] floating-point number form and it can normalized in the common base 10 (decimal) by following equation 1.3. The standard floating-point definition consists of three parts: sign, exponent, and mantissa. Moreover, the number range of floating-point can be defined in several binary formats with different bit widths of 32, 64, and 128 bits by varying the mantissa and the exponent bit width. The table 1.1 contains the bit width of various precision of floating-point number and its component bit width; mantissa, bias, exponent bias and max decimal exponent.

$$X = (-1)^S \times (1 + Mantissa) \times 2^{Exponent-Bias}$$

(1.3)

As we can see in Figure 1.12, the floating-point number has three components: sign  $\pm$  s, exponent e, and mantissa m. The first bit of floating-point is sign s, and this indicates

Figure 1.12 – IEEE 754 Single precision Floating-point representation.

Table 1.1 – Various precision of IEEE 754 normalized Floating-point representation

| Precision           | Mantissa | Exponent | Max decimal | Exponent |  |

|---------------------|----------|----------|-------------|----------|--|

| 1 Tecision          | width    | width    | exponent    | bias     |  |

| Single precision    | 24       | 8        | 38.23       | 127      |  |

| Double precision    | 53       | 11       | 307.95      | 1023     |  |

| Quadruple precision | 53       | 11       | 307.95      | 1023     |  |

the negative or positive of the value with '1' and '0' respectively. The following bits introduce exponent e and this represent both positive and negative exponents. These bits are designed as  $2^{e-bias}$ : excess number of bias binary integer added. To normalized these bits, the bias is added to the actual exponent in order to obtained the stored exponent. For example, IEEE single precision floats has bias 127. Thus, to express an exponent of zero, 127 is stored in the exponent field. A stored value of 200 indicates an exponent of (200-127), or 73. For these reasons, exponents of -127 (all 0s) and +128 (all 1s) are reserved for special numbers indicated in table 1.2. The rest of bits are set up for Mantissa m, also known as the significant bits, and it is designed for precision bits of number. It is treated as fractional fixed point binary number. Unlike fix point binary number, it is composed of an implicit bit ('1') and the fraction bits, so that a 32-bit floating-point value effectively has 24 bits of mantissa: 23 explicit fraction bits plus one implicit bit of 1.

#### 1.2.3 Approximate techniques

From recent studies, approximate computing has been broadly employed in several domains and offered a successful solution that eases design constraints with various techniques; precision scaling, loop perforation, and voltage scaling [82, 83, 84, 85]. First, in Precision scaling, it propose different level of precision on data to gain memory and energy efficiency. For example, it proposes decreased data bit-width that scale down the data precision but gain memory density which allows save more data in memory. Secondly, loop

| Sign | Exponent e   | Mantissa     | Value                         |

|------|--------------|--------------|-------------------------------|

| 0    | 0000         | 0000         | +0                            |

| 0    | 0000         | 0001 to 1111 | Positive denormalized real    |

| 0    | 0001 to 1111 | XXXX         | Positive normalized real      |

| 0    | 1111         | 0000         | $+\infty$                     |

| 0    | 1111         | 0001 to 1111 | Signalling Not a Number(SNaN) |

| 0    | 1111         | 1XXX         | Quit Not a Number (QNaN)      |

| 1    | 0000         | 0000         | -0                            |

| 1    | 0000         | 0001 to 1111 | Negative denormalized real    |

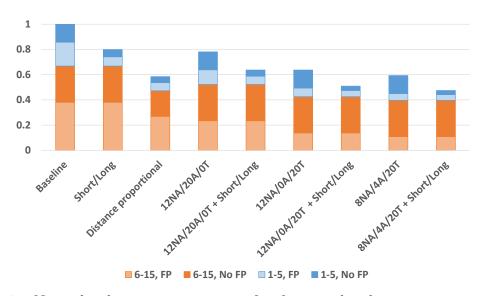

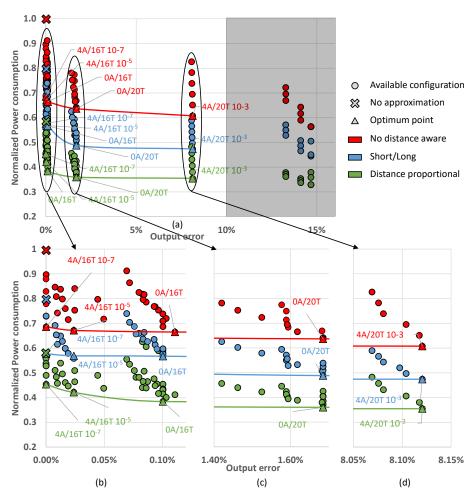

| 1    | 0001 to 1111 | XXXX         | Negative normalized real      |