# (Aix\*Marseille Université Initiative d'excellence UNIVERSITE D'AIX-MARSEILLE IM2NP

ECOLE DOCTORALE 353

CEA-Leti Advanced Memory Lab

A Thesis submitted in fulfillment of the requirements for the Degree of Doctor of Philosophy

Discipline: Electrical Engineering Specialization: Micro and Nano electronics

## Marios Barlas

# Development and characterization of innovative nonvolatile OxRAM memory cells compatible with advanced nodes

Soutenue le JJ/MM/AAAA devant le jury :

Daniele Ielmini Politecnico di Milano Université de Bordeau Nathalie Malbert Jean-Michel Sallese EPFL Simon Jeannot **STMicroelectronics** Gérard Ghibaudo Université de Grenoble-Alpes Damien Deleruyelle INSA Lyon Laurent Grenouillet CEA-Leti Elisa Vianello CEA-Leti Jean-Michel Portal Aix-Marseille Université

Rapporteur Rapporteur Examinateur Examinateur Examinateur Invité Invité Directeur de thèse

Numéro national de thèse/suffixe local : 2017AIXM0001/001ED62

To all the people who made me who I am today

The journey of a thousand miles begins with one step.

-Lao Tzu

# SOMMAIRE

Les mémoires resistives a base d'oxydes de transition organométalliques (OTM) sont fortement étudiés comme un candidat pour des applications mémoires non volatiles. Il y a trois moteurs derrière la forte activité R&D sur les mémoires non volatiles : Tout d'abord, la demande sans cesse croissante de plus en plus de puissance de calcul pour les applications haut de gamme (HPC). C'est le moteur principal des semi-conducteurs « classiques », à savoir les mémoires CMOS, DRAM et NAND; mais à un rythme plus ralenti en raison de la mort de la loi de Moore. Deuxièmement, le passage de l'ère PC / mobile du début des années 2000 à l'ère de l'Internet des objets (IoT) conduisant à un matériel spécifique à l'application et à une éventuelle diversification des technologies possibles en fonction de l'application. L'IoT impose des exigences matérielles que les applications de mémoire classiques ne sont pas en mesure de fournir dans certaines applications, surtout si le coût est pris en compte. Troisièmement, la nécessité identifiée d'un changement perturbateur du paradigme informatique avec des domaines tels que l'intelligence artificielle (IA) et l'informatique neuromorphique, entraînant le besoin d'un nouveau matériel pour les synapses à neurones, auquel les ReRAM pourraient apporter une solution avec leur comportement de commutation analogique.

Dans le cadre de cette travail on examine d'une facon systematique

Mots clés :

# Abstract

Transition Metal Oxide ReRAM is a class of non-volatile memory technologies where the switching between memory states is enabled by the reversible breakdown of the oxide by means of the creation and dissolution of a percolation path (filament). The main advantages of the technology lie in the scalability of the memory cell –mainly owed to the sub 10nm dimension of the filament, its low power consumption (< 300 pJ/ switch) and material compatibility to advanced CMOS. Nevertheless, there are two major roadblocks that have prevented so far the implementation of ReRAM in large arrays: First, the requirement for an initial breakdown happening voltages significantly higher than the operating voltage range and second, the intrinsic and extrinsic variability components arising from material interaction to its environment as well as the fundamental stochastic nature of percolative conduction.

This work, is focused on HfO<sub>2</sub> based ReRAM technology. In the first part, we investigate different dopants to engineer the conductive properties of HfO<sub>2</sub> by combining a first-principles approach and in-depth material characterization techniques. In the second part, the proposed HfSiOx alloy is integrated in the BEOL of a 130nm process and the impact of the integration of the switching zone in forming, switching, error rate evolution and data retention is investigated. In the last part, a HfO<sub>2</sub> based integration in the early MOL of an advanced FDSOI 300mm CMOS process is demonstrated investigating standard HfO<sub>2</sub> ReRAM performances and limitations.

Keywords : ReRAM, semiconductor process integration, CMOS, FDSOI, HfO<sub>2</sub>, doping, Si, Al, defect engineering, endurance, data retention

# Acknowledgements

Working in technology and device physics is certainly teamwork. It requires a great deal of patience for wafers to go through hundreds of physico-chemical steps a process that lasts for months and it's a great exercise for patience. And all that, after the initial idea has been theorized and you've tried your best to cover all bases. As a consequence, no work showing results on the level of a chip demonstrator is the work of a single person. My role in this has been to provide some guidelines and connect the dots between theory, device integration, intrinsic and extrinsic device physics. As a result, there's probably tens of people taking part in a smaller or larger degree to this journey.

First things first then, I should thank Elisa and Laurent for giving me the opportunity. I hope it's been a good 3-year long journey. In particular, I should thank them both for challenging my ideas and thoughts on the ReRAM that pushed me a step further every time. I'll thank Laurent in particular for his presence on an almost daily basis in my time in Leti be it to either encourage, question, or disapprove of my ideas and actions. To be horribly specific I particularly loved the "I x % agree with you" with x varying between 0 and 100 for every different case.

Then, there's Philippe Blaise. Through interacting with him, I got a good microscopic understanding of the material with a level of precision and exactness that I will try to translate in all of my following steps. At the same time, I should also thank boubacar Traoré for laying the first foundation in my work. His initial reflections on the HfO<sub>2</sub>:Si system laid the groundwork for what we did next. I only think it's a bit of a pity that we didn't get the chance to work together really owed to the non-overlap of our time in Leti.

From a material aspect, I should really thank Emmanuel Nolot for providing me with a fearsome amount of measurements in XPS and XRR and also for training me on the spectral analysis techniques and letting me free to find my way around the data from that point. Moreover, all the clean room process engineers that worked in developing steps of my projects deserve their merit as well.

Getting closer to the end, I'll thank my friend and great colleague, Alessandro Grossi for being a super fun partner in all that was analyzing data on the ReRAM arrays and pinging ideas over lunch for the better part of a year! In the same basket go the friends I made through my time in Leti like Thilo, Julia and Giuseppe that made the three years I spent there a good amount of fun. It's truly hard to find colleagues that can also be good friends in life as well, in my opinion anyways.

# An Introduction of Sorts

« La semplicità è l'ultima sofisticazione ». Simplicity is the ultimate form of sophistication -according to Leonardo da Vinci. This is maybe the most fitting place to start when it comes to ReRAMs. It is impressive that a concept so simple as breaking down a dielectric "sandwitch" could lead to so many possible applications: Over the years, the nanoionics community and designers have theorized -and even more so demonstrated on the product level- around the possible applications of ReRAMs: memory, neuromorphics, security, are just some of the applications that come to mind; there might be others that people haven't even thought of yet. Now the issue with geniuses, such as Da Vinci and genius ideas such as ReRAMs, is that usually there's a rabbit hole. It does not mean that if something is simple it is also simplistic. And this is where, albeit a great amount of research has been conducted in ReRAMs and nanoionics everyone is still yearning for that singularity that will allow the technology to soar. At the core of ReRAM lies dielectric breakdown, and breakdown is a whimsical physical process that remains elusive to this day despite all our best efforts to control it. After all, you cannot blame gravity for falling in love, as uncle Albert once said.

And so, back when I started working on ReRAMs in 2015 in the context of a master thesis, I wasn't really expecting that I was setting of in an almost four-year long journey that would essentially lead to a pursuit of restricting a percolation path. But now, I know that the journey of a thousand miles starts with a single step (Lao Tzu). And by now I'm pretty sure dear reader that you're getting tired of me quoting famous people. This work is all about pursuing something elaborate in something that is simple. We essentially tried to play billiards with atoms in a deterministic way to try and limit the possible path of dielectric breakdown that is, by nature, stochastic. In short, this research work is organized in five chapters.

In the first chapter, starting from the current semiconductor economic landscape I try to identify the current motors for ReRAM R&D are. The, I make an effort to summarize the work that I consider the most interesting so far in the field: In a bottom up approach, the types of ReRAM and different kinds of switching materials and their behavior are identified. A detailed review of the dielectric breakdown process from the microscopic level to the statistical laws governing the phenomenon. Key aspects of the physics of

the device in terms of material dependence and switching characteristics such as endurance and data retention are presented. From then on peripheral aspects of the technology such as architecture, selector devices and state of the art are briefly reviewed.

In chapter two, we move on to describe our material system of choice,  $HfO_2$  and how doping in general, and the ion implantation process in particular, can change the system properties in a significant fashion; provided the right dopant is used. Notably the Al and Si implants are studied in detail. We combine material analysis with ab-initio calculation to link local molecular microstructure to the electronic properties of the doped material matrix and its impact on the ReRAM device.

Chapter three picks up the idea of doping and explores the impact of device geometry and confinement of the implanted volume in different device characteristics: From forming, to ReRAM operation to endurance and data retention. We exploit relatively large (for academic prototyping capacities) statistical ensembles of the devices fabricated, to understand not only the intrinsic device characteristics but also the behavior and control of extreme individuals of the population while trying to identify the eventual trade-offs and limitations of the approach. In all this, we try to combine material and device geometry to not only modulate ReRAM conduction but also control to an extent the extreme most events of the resistive memory population by dissociating the switching zone from the device environment.

Chapter four falls back into the standard HfO<sub>2</sub> technology, exploring a more elaborate integration strategy to essentially try and achieve similar effects: Stronger control of the extreme-most events. Even if this chapter has been fun from the technology point of view, it basically serves to demonstrate that the fundamental roadblock of ReRAM is not necessarily technology maturity, but the profound proneness to variability of not just the percolation path, but also of the materials involved in the ReRAM stack itself. As a byproduct, we also demonstrated compatibility of the ReRAM stack to GO1 (sub 1.5nm gate stack oxide) FDSOI gate-first nodes. Finally, we conclude this work by a general summary of results and some ideas for pushing the limits for the ReRAM device beyond the standard MIM capacitor and towards the front end of CMOS in chapter 5.

In a more personal aspect, this work is more my desire to build something that tries to bring something into the equation of the ReRAM and to convince myself even more than others that it works in a consistent, systematic and repeatable fashion –more to be able to sleep at night without being haunted by the phantoms of physics. There were times I had a good deal of fun during this process and others that things were on the highway to hell. Now that the deed is done, even though I didn't achieve Da Vinci's intended sophistication, I feel like I start to understand why you cannot blame gravity for falling in love.

## **TABLE OF CONTENTS**

| CHAPTER 1. From oxide breakdown to OXRAM – a short overview                                              | 1         |  |  |  |

|----------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| 1.1 Introduction: The Memory Landscape                                                                   | 1         |  |  |  |

| 1.2 Some Basic notions of NVM and ReRAM                                                                  | 6         |  |  |  |

| 1.3 Materials in the ReRAM Cell and the impact in resistive switching                                    | 7         |  |  |  |

| 1.4 The current understanding of the Physics of the OxRAM Cell                                           | 8         |  |  |  |

| 1.4.1 Electronic Conduction Mechanisms in oxides                                                         | 8         |  |  |  |

| 1.4.2 A short overview of dielectric breakdown in oxides                                                 | 11        |  |  |  |

| 1.4.3 Forming process                                                                                    | 14        |  |  |  |

| 1.4.4 Switching Mechanism                                                                                | 19        |  |  |  |

| 1.5 ReRAM Architectures                                                                                  | 21        |  |  |  |

| 1.6 Variability of the ReRAM States                                                                      | 24        |  |  |  |

| 1.7 Endurance Mechanisms of TMO ReRAM                                                                    | 26        |  |  |  |

| 1.8 Retention Mechanisms of TMO ReRAM                                                                    | 27        |  |  |  |

| 1.9 The place of ReRAM in the CMOS integration                                                           | 29        |  |  |  |

| gggg                                                                                                     |           |  |  |  |

| CHAPTER 2. Material engineering for HfO2 based ReRAM by Si/Al ion                                        |           |  |  |  |

| implantation 31                                                                                          |           |  |  |  |

| 2.1 Introduction                                                                                         | 31        |  |  |  |

| 2.2 Ion Implantation in HfO <sub>2</sub> : The case of Si and Al doping                                  | 34        |  |  |  |

| 2.3 Alloying of Al and Si dopants in HfO <sub>2</sub> : Electronic Properties                            | 37        |  |  |  |

| 2.4 Pristine device electrical characteristics of Si/Al implanted HfO <sub>2</sub> based                 |           |  |  |  |

| RRAM                                                                                                     | 42        |  |  |  |

| 2.4.1 Device Fabrication                                                                                 | 42        |  |  |  |

| 2.4.2 Electrical Characteristics of the Devices in Pristine State                                        | 42        |  |  |  |

| 2.4.3 Dependence of the RRAM forming voltage on dopant concentration and                                 |           |  |  |  |

| temperature                                                                                              | 46        |  |  |  |

| 2.5 Material Properties of the HfO <sub>2</sub> :Si and HfO <sub>2</sub> :Al systems alloyed by ion      |           |  |  |  |

| implantation                                                                                             | 47        |  |  |  |

| 2.5.1 Physico-chemical signatures of the alloying mechanism                                              | 47        |  |  |  |

| 2.5.2 Sample Preparation                                                                                 | 48        |  |  |  |

| 2.6 Impact of Si, Al implantation on the mass density of HfO <sub>2</sub>                                | <b>49</b> |  |  |  |

| 2.7 Binding state of Al and Si in the HfO <sub>2</sub> matrix as a function of the dopan                 | t         |  |  |  |

| concentration                                                                                            | 53        |  |  |  |

| 2.7.1 XPS Measurement Principle                                                                          | 53        |  |  |  |

| 2.7.2 Binding State of implanted Al, Si in HfO <sub>2</sub> as a function of the dopant                  |           |  |  |  |

| concentration.                                                                                           | 54        |  |  |  |

| 2.7.3 ALD – HfO <sub>2</sub> and impact of Si implantation on Crystallinity                              | 58        |  |  |  |

| 2.7.4 Si implant thermal stability in HfO <sub>2</sub>                                                   | 58        |  |  |  |

| 2.8 A microscopic understanding of the alloying mechanism in HfO <sub>2</sub>                            | 60        |  |  |  |

| <b>2.9</b> Charge Generation in HfO <sub>2</sub> as a function of Si incorporation                       | 63        |  |  |  |

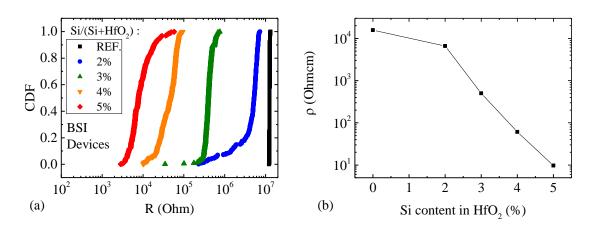

| 2.9.1 Oxide charging dynamics                                                                            | 63        |  |  |  |

| 2.9.2 Estimation of oxide-trapped charge as a function of Si incorporation                               | 66        |  |  |  |

| 2.10 Discussion: On the origin of conductive states in HfO <sub>2</sub> and associated                   |           |  |  |  |

| doping strategy for ReRAM applications7                                                                  |           |  |  |  |

|                                                                                                          |           |  |  |  |

| <b>CHAPTER 3.</b> Si implanted HfO <sub>2</sub> reram: the impact of local defect engineerin in ReRAM 74 | ng        |  |  |  |

| 3.1 | The concept of switching zone localization | 74 |

|-----|--------------------------------------------|----|

| J.1 | The concept of switching zone localization | /- |

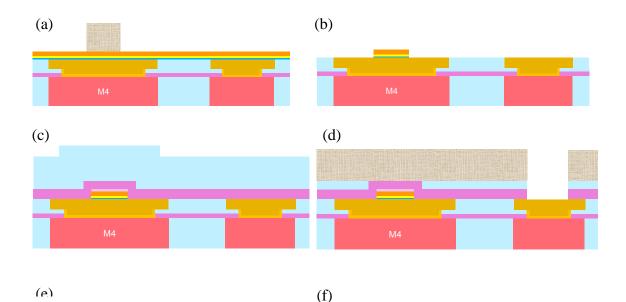

| 3.2 Integr                | ation of a Localized Switching ReRAM Cell in the BEOL                | 75         |

|---------------------------|----------------------------------------------------------------------|------------|

| 3.2.1 Des                 | cription of the test vehicle                                         | 75         |

|                           | gration of a ReRAM cell in the BEOL                                  | 75         |

| 3.3 Impac                 | t of local Si implantation on Pristine Devices and the Forming       |            |

| Operation                 |                                                                      | 79         |

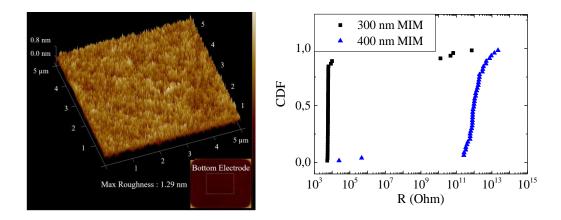

|                           | ine Resistance evolution with Si implant concentration               | 79         |

|                           | ning voltage evolution with Si implant concentration                 | 81         |

| -                         | act of Si doping on the diffusivity of O vacancies                   | 83         |

|                           | ostatics of ReRAM Devices with cylindrical geometry                  | 88         |

| -                         | t of LSI on the DC SET and RESET voltages of HfO <sub>2</sub> ReRAM  |            |

| devices                   |                                                                      | 96         |

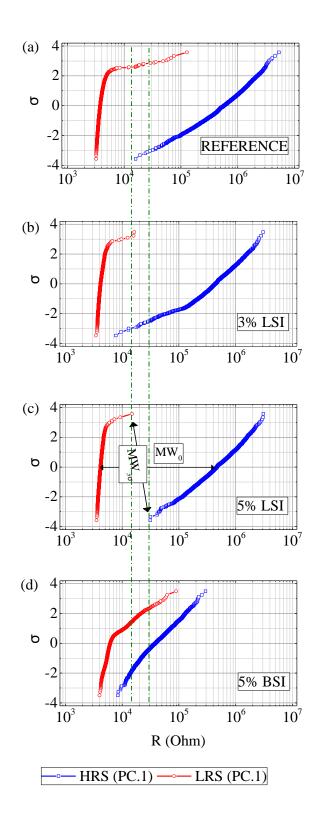

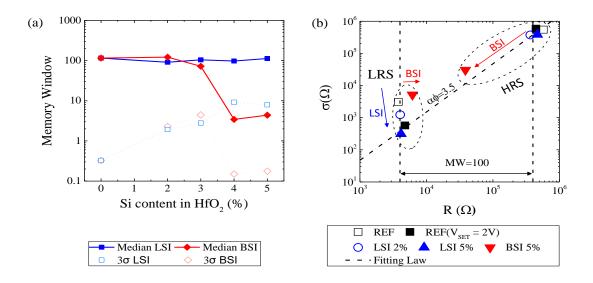

| -                         | t of filament localization on the statistical properties of LRS and  | d          |

| HRS 97                    |                                                                      |            |

|                           | ry Array programming optimization strategy                           | 104        |

|                           | oduction                                                             | 104        |

| •                         | gramming Conditions optimization on LSI devices: Qualitative         |            |

| Characteris               |                                                                      | 105        |

|                           | ramming Conditions optimization on LSI devices: Quantitative         |            |

| Characteris               |                                                                      | 108        |

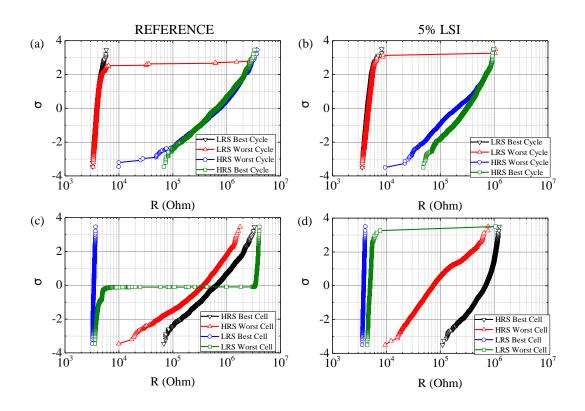

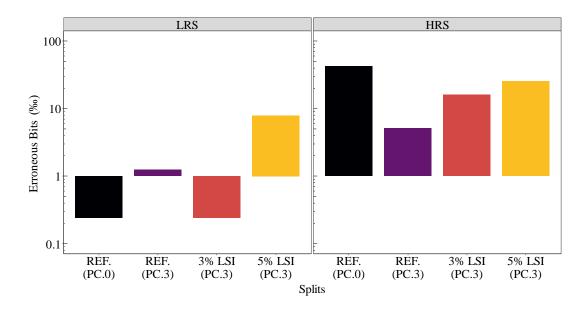

|                           | eliability: Endurance and Error Analysis                             | 111        |

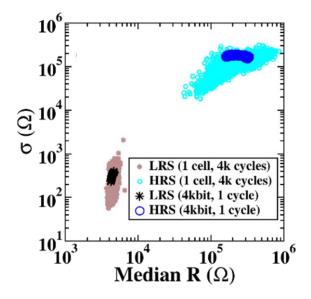

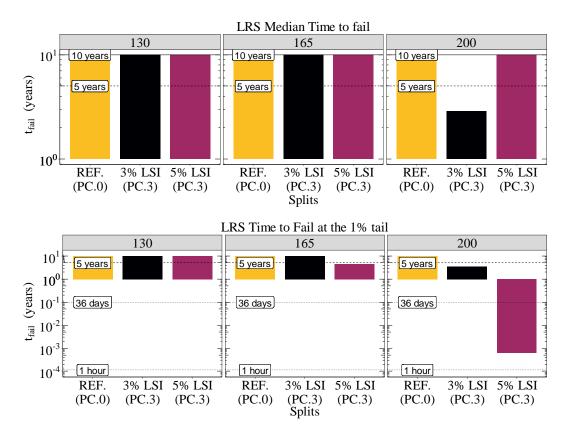

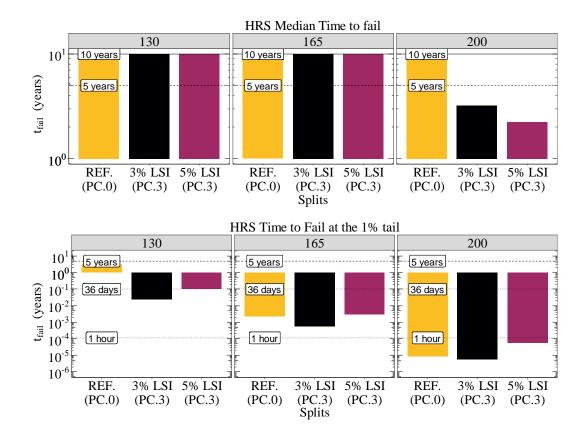

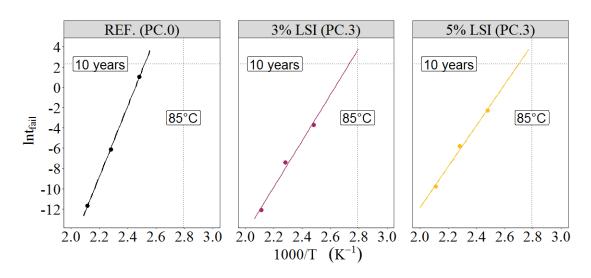

|                           | Retention assessment on large populations                            | 113        |

| 3.9.1 Intro               |                                                                      | 113        |

|                           | gn of Experiment for Data Retention                                  | 114        |

|                           | Retention at High Current Compliance: Qualitative Characteristics    |            |

| -                         | act of the programming current and Si implantation on the BER of     |            |

| kbit arrays               | inizal madel for register on drift                                   | 117        |

|                           | birical model for resistance drift<br>ler Reflow Tolerance           | 123<br>127 |

| 3.9.0 Sold                |                                                                      | 127        |

| <b>3.10 Concl</b>         |                                                                      | 120<br>129 |

| 5.10 Coller               | 1810118                                                              | 129        |

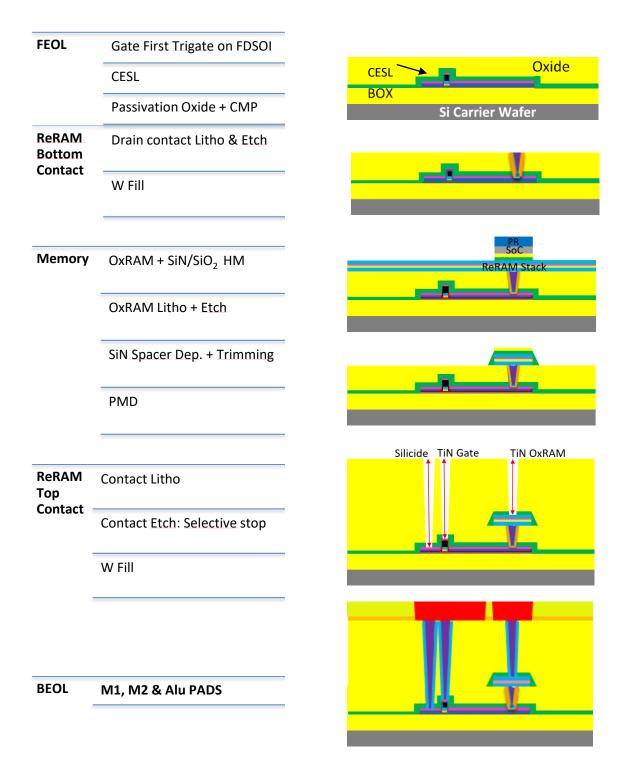

| CHAPTER 4<br>technology 1 | 8 8                                                                  |            |

| 4.1 Introd                |                                                                      | 131        |

|                           | egration of HfO <sub>2</sub> based ReRAM in FDSOI gate-first process | 151        |

| flow 132                  | egration of 11102 based Renative in 1 D501 gate 111st process        |            |

|                           | gration concept and process flow                                     | 132        |

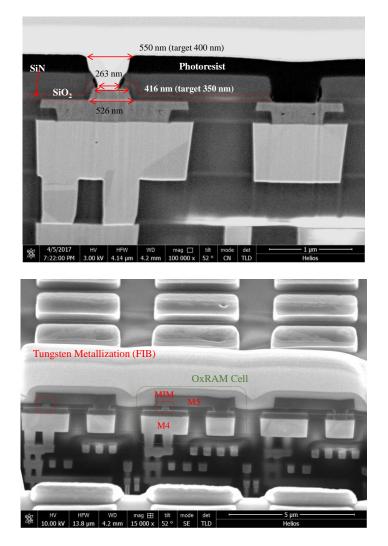

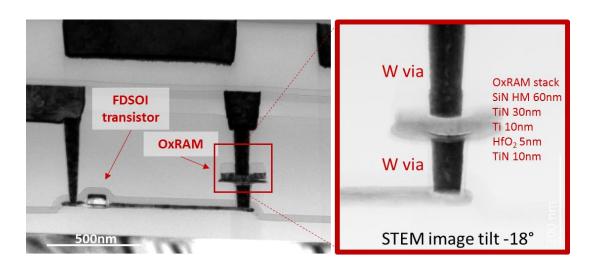

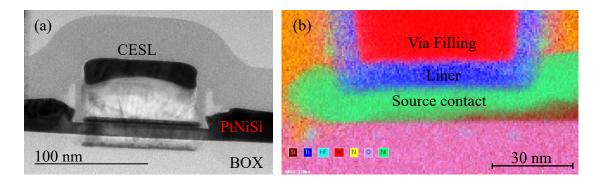

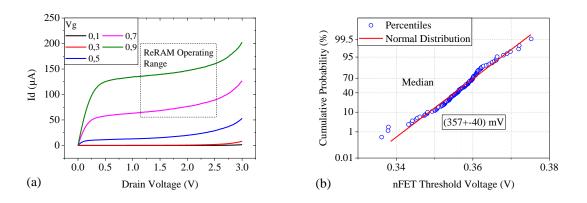

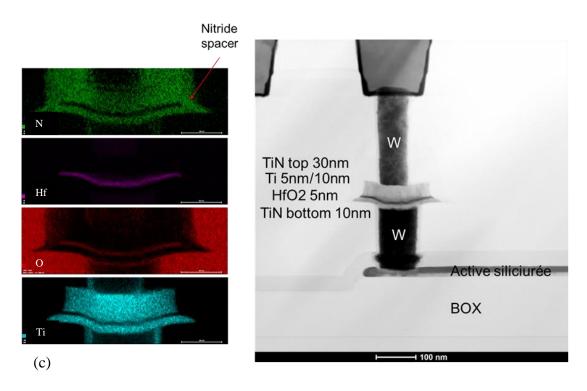

|                           | DL and MOL technology characteristics                                | 135        |

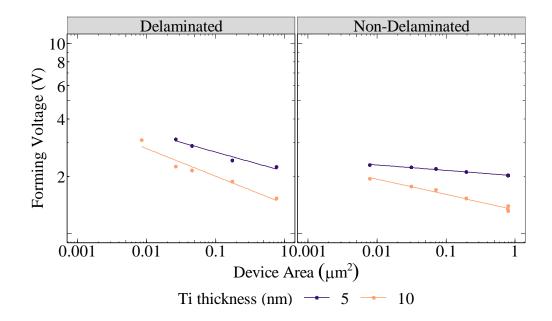

|                           | L ReRAM integration: Impact of Structural Integrity of the Memory    |            |

|                           | rical characteristics                                                | 138        |

|                           | phological Characteristics of the memory node                        | 140        |

|                           | e considerations for interface mechanical failure                    | 142        |

|                           | ss-robust Scaled ReRAM process: Morphological Characteristics        | 145        |

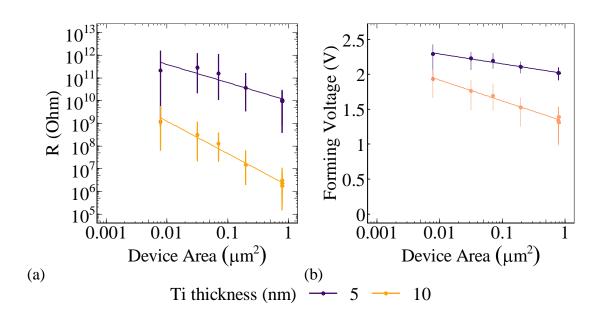

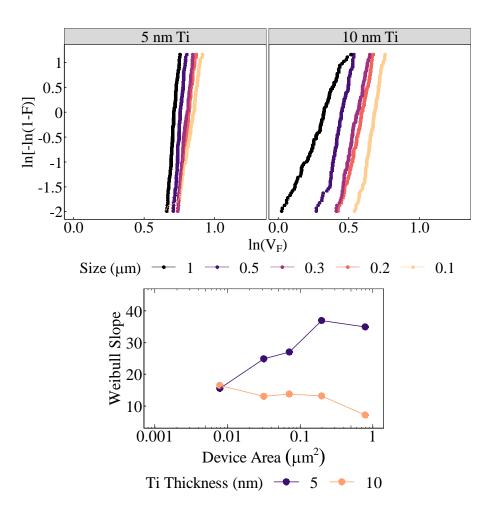

|                           | act of scaling and Ti thickness in ReRAM devices integrated on FD    |            |

| technology                |                                                                      | 147        |

| 4.3 Conclu                | isions                                                               | 157        |

|                           | e Prospects                                                          | 158        |

| CHAPTER 5                 | -                                                                    | 160        |

xi

| Bibliography        | 167 |

|---------------------|-----|

| List of Tables      | Ι   |

| List of Figures     | П   |

| List of Disclosures | X   |

## CHAPTER 1. FROM OXIDE BREAKDOWN TO OXRAM – A SHORT OVERVIEW

## **1.1 Introduction: The Memory Landscape**

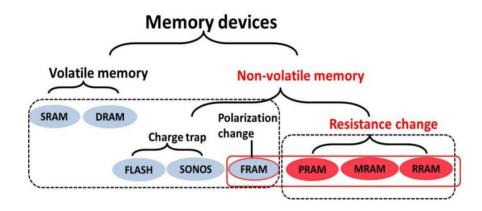

Figure 1-1 Classification of emerging NVM technologies

For the last 30 years when Moore's Law was the main drive in the field of microelectronics almost all high-speed, high-density memory applications were addressed through CMOS transistor derivatives based on a charge-trapping physical mechanism. SRAM remains the predominant choice for embedded high speed applications where non-volatility is not required. DRAM (volatility in the ~ms range) provide high memory bandwidth (> 100 GB/s) and low latency. Ever since it was invented in 1987 [1] FLASH has allowed virtually the only CMOS compatible non-volatile memory cell providing significant boosts in power reduction and density owed to Moore's law at every node giving birth to solid state storage class memory, constituting 43% of the semiconductor memory market in 2016 [2].

Nevertheless, 30 years of continuous scaling have inevitably led to approaching fundamental physical limitations. And while breakthroughs in 3D integration continue to drive DRAM and V-NAND in the sub 20nm nodes, they come at a steep price in process complexity, that has heavy impact in fabrication cost. This trend means that soon the manufacturing cost might render the use of advanced NAND prohibitive to certain classes of applications. As a result, the industry has started to explore different kinds of non-volatile memory based on completely different physical principles, known as resistive memories (Figure 1-1), where the memory state is associated to a resistance level in the cell.

# Vertice of the second s

## **Evolution of Computing Landscape**

Figure 1-2 Applications driving computing roadmap [Short Course, IEDM 2018]

A number of different physical systems exhibit resistive switching behaviour. Phasechange memory (PCM) base their operation on the change of phase of the active material as a function applied voltage owed to Joule/electronic heating. Magnetic tunnel junctions (MTJ / STT-MRAM) resistance state changes with voltage are associated to the parallel and anti-parallel configuration of electronic spin between the active layers of the device [3]. The ReRAM switching mechanism is thought to be mainly owed to modulation of conductivity owed to the reversible dissolution of ion species transitioning to and from given oxidation states. Historically the latter have been differentiated between CB-RAM or Electrochemical Metallization Cell (ECM) and OxRAM or Valence change (VCM) if the conductive centres are attributed to metallic ion species or oxygen vacancies, respectively [4], [5].

All these classes are significantly different with respect to standard flash both in terms of operation principle and architecture. Contrary to charge-trapping NVMs the above *emerging* NVM technologies are two terminal devices based on Metal Insulator Metal (MIM) stacks. This comes with the distinct advantage of highly simplified integration schemes as will be discussed in further detail in the following sections. Even though NAND and DRAM are still the dominant technologies, emerging NVMs are starting to pick up momentum owed to the diversification of computing in the modern era.

Three key factors driving computing can be identified for the near and mid future: First, the ever-growing demand for more and more computational power for high-end applications (HPC). This is the main drive behind "classical" semiconductors namely

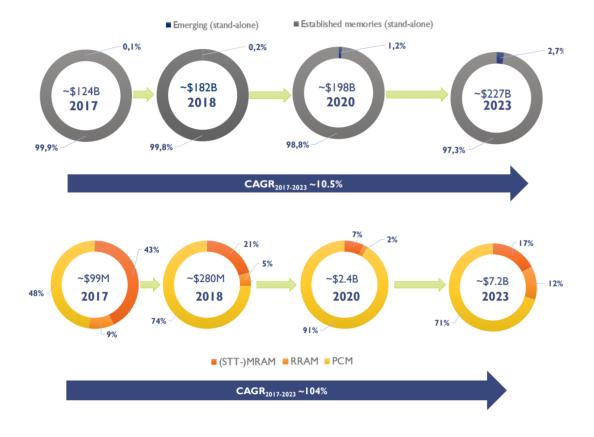

Figure 1-3 Predicted Memory Market Growth – Yole Development Group, reprinted with permission (CAGR for chiffre d' affaires growth)

CMOS, DRAM and NAND flash; albeit at a decelerating pace owed to the death of Moore's Law and the end of transistor scaling. Second, the passage from the PC/mobile era of the early 2000s to the era of the Internet of Things (IoT) (Figure 1-2) leading to application-specific hardware and an eventual diversification of the possible technologies according to the application. IoT imposes hardware requirements that classical memory applications are not able to deliver in some applications, especially if cost is taken into account. Third, the identified need for a disruptive change in the computing paradigm with fields like Artificial Intelligence (AI) and neuromorphic computing, giving rise to the need for new hardware for the neuron synapses, to which ReRAMs with their analog switching behaviour could be a solution [6]–[9].

All of these factors give rise to a growing market for new memory technologies. At present, the stand-alone memory market is projected to grow from a 124B in 2017 to ~227B in 2023. Interestingly, even though the memory sector is will still be dominated by traditional technologies, notably NAND flash and DRAM, it starts to slowly but surely give ground to resistive switching memories that, even though take less than 0.1% of the

market share nowadays, are projected to reach 2.7% in the next five years, generating a new market worth more than 7B \$ by 2023 (Figure 1-3).

Out of the different competing resistive switching technologies three are leading the emerging NVM market evolution, namely PCM, STT-MRAM and ReRAM. Between the three, PCM is considered the current leader with more than 15 years of R&D, driven by major players like Intel & Micron with 3D X-Point technology in Optane chips for mainstream applications, but also by STMicroelectronics oriented more towards the microcontroller market [10], and are based on GST (Ge-Se-Te) compounds.

STT-MRAM starts to appear as a PCM contender promoted mainly by players like TSMC and Globalfoundries and promising high switching speed and almost unlimited endurance [11]. Nevertheless, its sensitivity to temperature has proven to be much stronger of a challenge than initially expected, with Samsung reporting early product-ready maturity only at the beginning of 2019 [12].

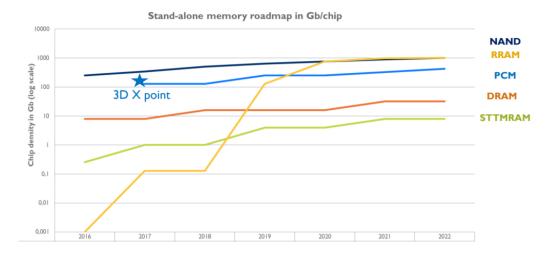

Resistive memory devices based on transition metal oxides (OxRAM) base their prospect insertion into the emerging NVM market owed to three main drivers: First, their physical principle allows for the NVM memory window to be either insensitive to scaling or even be expected to augment as the cell dimension is reduced (such is the case of nonfilamentary switching mechanism) (Figure 1-4). As a result, it might be the only NVM type amongst the emerging technologies that can match density large enough to contend its more mature NAND and DRAM candidates. Second, the simplicity of the cell which promises to deliver high density at low cost. Third, their analog switching behaviour and memristive properties [13]–[16] that has recently attracted a lot of attention as a potential element to implement neuromorphic chips. The main roadblocks for ReRAM are their requirement for forming operation that increases chip design complexity for large scale implementations, their limited endurance as well as their sensitivity to intrinsic and extrinsic variability. Nevertheless, it is worth noting that, variability, albeit imposing problems for memory applications could be a benefit in disguise for neuromorphic chips. To date only Panasonic[17] and Fujitsu[18] have announced small-scale ReRAM chips in the market.

It is nowadays generally understood that the future of microelectronics will be diversified and application specific. Especially for NVM, there is no technology to solve all problems.

Figure 1-4 Predicted Stand-alone cell density evolution – Yole Development Group

As a result, ReRAM –which is the main focus of this work- faces the challenge and the opportunity to become the best candidate for some applications. Nevertheless, ionic manipulation, which lies at the heart of the ReRAM switching mechanism, proves a challenge bigger than the scientific community have expected as has been recently observed [19].

This work aspires to provide some solutions to key aspects towards industrialization of ReRAM. In this brief introduction, an effort was made to provide some context into the undercurrents influencing the development of the technology from an economic and application prospective. In the following section, we move to describe ReRAM in more detail. I strongly believe that, to understand ReRAM it is required to first understand the key aspects of conduction of oxides and dielectric breakdown; that after all lie at the heart of the ReRAM switching mechanism. For this reason, the next two sections detail conduction mechanisms in oxides and dielectric breakdown from a more general prospective. Then, the current theories about the physicochemical processes involved in the TMO ReRAM technology are detailed along with materials of interest and current cell and device architectures.

### 1.2 Some Basic notions of NVM and ReRAM

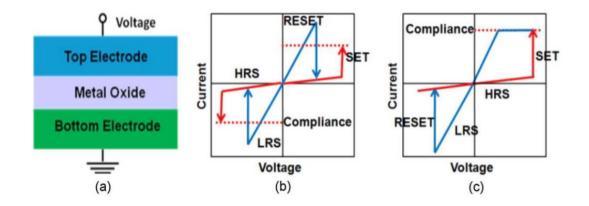

Figure 1-5 (a) MIM structure based ReRAM cell (b) Unipolar device and (c) bipolar device switching regimes respectively [4]

NVM cells can have two or more resistive states, namely a low (LRS) and a high (HRS) resistance states. Binary cells can oscillate between only two resistance levels while multilevel cells can have more than two stable resistive states, according to the programming conditions applied on the cell. In ReRAM, the as-fabricated material cell typically requires a first preliminary operation of controllable soft dielectric breakdown, commonly referred to as electroforming or forming process. Forming occurs by either applying a pulse ramp or a constant voltage pulse on one of the device electrodes until the device experiences a breakdown event.

After forming, the cell state can be reversed by applying appropriate programming conditions. The transition from HRS to LRS is referred to as the SET operation while the transition from LRS to HRS as the RESET operation. While the set voltage corresponds to the voltage at which the SET switch occurs, the reset voltage is not defined in the same straightforward manner. In most cases, the (dc) reset voltage term refers to the maximum voltage that is used during the reset phase. This discrepancy is mainly owed to the difficulty to correlate an easy-to-detect characteristic of the I-V curve to the reset operation, owed to the high variability associated to the reset phase.

ReRAM cells can exhibit either *unipolar* or *bipolar* switching. Unipolar switching occurs when the cell's resistance state can be reversed from LRS to HRS by applying a voltage of the same polarization configuration as the one used to induce the LRS state (Figure 1-5b). If the polarization in the device terminals needs to be reversed in order for the

transition from LRS to HRS to occur then the cell is characterized as bipolar (Figure 1-5c). Cell polarity is strongly dependent not just on the oxide used, but more specifically in the oxide/metal electrode combination, and will be discussed in further detail in the sections 1.3 and 1.4.

ReRAM cells can exhibit both surface-dependent and surface independent (filamentary) switching, depending on the material system and choice of electrodes. This work focuses on the TiN/HfO2/Ti system that demonstrates purely filamentary behaviour.

## 1.3 Materials in the ReRAM Cell and the impact in resistive switching

A very wide range of materials have been studied for resistive switching applications, including both oxides, chalcogenides as well as nitrides [20], [21]. Both binary and complex oxides such as SiO<sub>2</sub> [22], [23], TiO<sub>2</sub> [24]–[26], [27], NiO [28] and SrTiO<sub>3</sub> [29], [30] can show resistive switching characteristics. An rather complete review of the different materials exhibiting resistive switching characteristics can be found in [31]. Nevertheless, out of the wide range of possible candidates studied over the years, the most promising in terms of memory performance have proven to be Al<sub>2</sub>O<sub>3</sub>[32], Ta<sub>2</sub>O<sub>5</sub> and HfO<sub>2</sub> for which a large range of works can be found in the literature [4], [33]. The latter oxides (Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub>) are particularly important for ReRAM because even more than their promising switching behavior are all widely used in CMOS technology and are thus easy to integrate in a semiconductor fabrication process.

At this point it is important to stress the sensitivity of the ReRAM switching behavior to the nature of the metallic electrodes. Both inactive and reactive metals have been used as ReRAM electrodes. For instance, the Pt/HfO<sub>2</sub>/Pt system has been shown to exhibit unipolar switching behavior [34] while the Pt/HfO<sub>2</sub>/TiN can be both unipolar and bipolar [35]. Using a reactive metal of column IV of the periodic table as a ReRAM electrode, such as Ti or Hf favors bipolar switching while at the same time, increasing the thickness of the scavenging layer acts to reduce the forming voltage of the cell [36], [37]. Nevertheless, this comes at the expense of impacting the data retention characteristics.

From the early stages of ReRAM, it has been understood that in order to tune ReRAM cell characteristics a systematic approach needs to be adopted in terms of material stack engineering as simple thickness scaling of either the oxide or the metallic electrode does not provide enough margin to tailor cell switching with enough liberty in order to accommodate the needs of storage class memory. Engineering at the level of the top electrode has made it clear that the level of stoichiometry in the metal/oxide interface can add another degree of freedom in ReRAM technology design.

Bilayers or alternating nano-laminate stacks of binary oxides have been used to engineer stacks with preferential switching characteristics. The  $Ta_2O_5/TiO_2$  system has been shown to exhibit superior endurance and resistance state uniformity characteristics [38] while  $HfO_2/Al_2O_3$  have been shown to improve the data retention of the  $HfO_2$  based ReRAM cell [39]–[41].

Doping TMOs to achieve improved switching characteristics has thus been heavily investigated; especially for  $HfO_2$  [42]–[45] and  $Ta_2O_5$  [46]. A wide variety of dopants has been proposed such as Ti, N, H, Si, Al, Mg and Ru targeting to modulate oxygen vacancy concentration and migration energies in the oxide matrix. Experimental results remain somewhat controversial however (see Al/Si doping in  $HfO_2$  by implantation [45] or nanolaminates ). Recently, Duncan et al. have proposed some theoretical guidelines for the behavior of dopants in  $HfO_2$  [47]. Nevertheless, the creation of an alloy that can not only tailor forming and switching voltages but also allow to act in-situ in key aspects such as endurance, retention and variability is still a topic of open research in the ReRAM field.

### 1.4 The current understanding of the Physics of the OxRAM Cell

#### 1.4.1 Electronic Conduction Mechanisms in oxides

From a band diagram prospective, oxides can be considered an extreme case of semiconductors. In both classes of materials, the valence and conduction bands are separated with a band gap, spanning from a few eV in classical semiconductors (Ge – 0.58 eV, Si 1.1 eV, SiC – 2.36 eV) to several eV in oxides (> 5 eV) [48].

It is important to notice that for any meaningful measurement of conduction a test structure is required, typically either an MIS (Metal Insulator Semiconductor) or a MIM (Metal Insulator Metal) contact. As material properties from one material to another differ, when different materials are brought in contact the energy bands are *bent* to satisfy thermodynamic equilibrium. The rate of band bending is dependent on the work function difference between the different materials in contact, which in turns affects the quantum mechanical barrier shape.

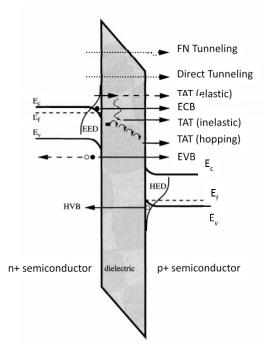

Figure 1-6 Schematic representation of an oxide as a potential barrier and the different types of electronic conduction as a function of field, temperature and presence of defects in the material and interfaces

In the absence of electrically active defects (perfect insulator) and considering the shape of the quantum-mechanical barrier alone, conduction is governed by the transmission probability of an electron through the volume of the oxide, known as *direct tunnelling*. This is owed purely to the penetration of the electron wave function into the volume of the oxide, and is therefore dependent on the barrier shape which is in turns defined by oxide band gap and oxide thickness and the rate of *band bending*.

If a semiconductor/oxide contact is considered tunnelling can be more rigorously classified in ECB (electrons from conduction band), EVB (electrons from valence band) and HVB (holes from valence band) (Figure 1-6). Such is the case of the MIS or MS (Metal semiconductor or shottky contact). In the MIM structure however, which is of interest in this work, further distinctions are not necessary owed to the absence of a band gap in the metal. A detailed review of direct tunnelling models can be found in [49].

The application of an electric field in the terminals of the test structure leads to further band bending and enhances electron transmission probability, leading to a strong increase in the observed current. At the limiting case where the barrier shape is degenerated to a triangular shape the conduction regime is known as Fowler-Nordheim (F-N). Presently, for state of the art oxides where defectivity level is very low, the complete direct tunnelling effect becomes dominant for ultra-thin oxides (typically < 2nm) whereas F-N becomes dominant at high fields or strongly bent bands [50]. Finally, a transition can also occur by excitation of an electron in an energy range sufficient for it to surpass the energy barrier of the oxide/s or m/oxide interface and find itself in the conduction band of the metallic electrode, more widely known as thermionic or Schottky emission. Contrary to direct tunnelling schemes temperature doesn't play a role, Schottky emission is enhanced by temperature. [50].

Charges in the oxide (space charge) arising from structural defects of the oxide or other contaminants can contribute in conduction. This is a fundamental property of charges and arises naturally using dimensional analysis on the Poisson equation, more widely known as the Mott-Gurney law for space charge limited conduction [50].

The presence of charged defects (typically associated with a charge state) in the oxide volume acts to lower the effective barrier height an electron feels in the vicinity of the trap. The case where an electron can be excited into the conduction band (either by means of temperature or field) through a trap site is called Poole-Frenkel emission [50]. Another scenario is 'hopping conduction', where electrons are trapped for ultra-short times in a site forming a quasi-hydrogen state. By means of temperature of field excitations the electron is momentarily excited free from the trap only to be captured by the energetically most favourable closest neighbour. Tunnelling is therefore conducted through a series of such "hops".

The latter mechanism is probably the most complete and general way to model conduction in oxides and amorphous semiconductors, although even semi-analytical solutions are limited to strict assumptions. Even though multiple groups contributed in the development of the theory involved, a comprehensive model linking macroscopic current properties to the evolution of tunnelling probability with temperature, field and the average distance between defects (localization parameter), J ~ P( $\alpha$ ,F,T) was proposed by Dr. Nevill Mott (Nobel prize 1977) [51]. Finally it is worth noting the works of Apsley & Hughes on the macroscopic current characteristics of hopping conduction as a function of defect density, temperature and field [52], [53].

The J-V relation evolution at different temperatures can give valuable information about the spatial density of defects through the values of the localization parameter and density of states, both of which can be linked to the slope and intercepts of the linearized logJ-logV diagram. A detailed treatment of the topic can be found in [53]. Current conduction is directly related to the generation rate of defects in the oxide which leads to dielectric breakdown phenomena. In the next section a short overview of the physics of dielectric breakdown in oxides is presented.

## 1.4.2 A short overview of dielectric breakdown in oxides

Dielectric breakdown phenomena were observed for the first time in solid insulators by the German physicist Georg Christoph Lichtenberg in the 17<sup>th</sup> century and constitute the only macroscopically observable image of dielectric breakdown in our disposal, capturing the chaotic (yet fractal in nature [54]) behavior of dielectric breakdown pathways formed in solids; more widely known as conductive filaments within the ReRAM community.

The development of microelectronics has caused a systematic study of breakdown phenomena in oxides, in particular SiO<sub>2</sub> and high-k dielectrics. The origin of dielectric breakdown is understood to be linked to the generation rate of defects (breaking of molecular or atomic bonds). The increase of conductive defect density relates in turn to an increase of current density hence facilitating the breaking of bonds in a cascade process. For thick or high barrier oxides current is mainly controlled by FN tunneling while for thin oxides, direct tunneling is more critical. As the defect density increases in the oxide interface / volume current is controlled by TAT or hopping mechanism. The random evolution of defects generates a percolation path resulting in the random evolution of the conductive pathways in the oxide [55].

The physical process of BD is argued to happen in two stages: First, a random generation of defects takes place in the oxide volume known as the nucleation phase. Once a critical defect density is reached at a given site, the local field and temperature perturbations act to propagate the direction of the defect growth from one electrode to the other, driven by the electric field. Once the percolation path is formed, further augmentation of local conductivity leads to lateral wear out and enlargement of the filament.

The point where the defect density becomes critical for a permanent change to be observed in the electrical behavior of the oxide is called *breakdown event* and it is mainly associated with two experimentally measurable parameters: time-to-breakdown  $T_{BD}$  (in a constant bias/current stress regime) or breakdown voltage  $V_{BD}$  (in a varying bias/current stress regime) both of which are shown to follow a power-law [56]. In the context of MOS technology the charge-to-breakdown ( $Q_{BD}$ ) is often used, that is the total charge injected into the oxide for a measurable breakdown even to be observed.

The power law dependence of  $T_{BD}$ ,  $Q_{BD}$  and  $V_{BD}$  parameters lies is the underlying reason for the weakest-link problem ([55], [57]) and the reign of Weibull statistics over DB [57].

$$F = 1 - \exp\left[-\left(\frac{x}{x_{63\%}}\right)^{\beta}\right] \xrightarrow{\text{yields}} \ln\left[-\ln(1-x)\right] = \beta \ln x - b \ln x_{63\%}$$

(1.1)

The Weibull distribution probability can be projected in the dual-log space where the Weibit "ordinal" variable can be linearly related to the log of the statistical breakdown variable. The slope (shape factor) of the Weibit distribution is a particularly important parameter giving a measure of the intrinsic variability of the Weibull process whereas the intercept is generally related to the device surface. From a physical standpoint, the two parameters are often linked to device macroscopic characteristics such as oxide thickness t<sub>ox</sub>, with the relations according to the models of Suñé [58] & Degraeve [59], [60]:

$$\beta = \left(\frac{a}{a_0}\right) t_{\text{ox}} , \qquad \eta \propto \exp\left(-\frac{1}{\beta} \ln(\frac{A}{a_0^2})\right)$$

(1.2)

where a<sub>0</sub> is the defect size and A, the cell surface. The slope dependence on oxide thickness is associated to the probability of presence of defects assuming defect distribution in the oxide volume is homogeneous [61] and is well supported by experimental results in CMOS technologies or in structures where reactive electrodes are not introduced [62]. Nevertheless, when applied to ReRAM the interface reactions between oxide and reactive electrode should be taken into account and can strongly affect the dependence of the parameters to their nominal "geometric" values.

Finally, it should be noted that the qualitative characteristics of breakdown events in the Weibit diagram can be used to detect different breakdown mechanisms in the same class of devices through the change in slope as a function of the region of values for the statistical variable. This is often used to differentiate between intrinsic and extrinsic events. As is usual with statistics though, care must be taken when trying to relate a

statistical property of the system to its physical parameters as the interpretation is often highly sensitive to the assumptions made.

Historically, three models have been proposed, relating microscopic physical mechanisms to the evolution of defects during BD. First, the thermochemical model proposed by McPherson, Mogul and Khamankar for SiO<sub>2</sub> [63] initially and later extended to high-k materials [64], [65]. In the thermochemical model the breakdown mechanism is associated to the formation of oxygen vacancies in the Si = O or in general the M = O bonds linked to the bond formation enthalpy as well as the oxide dielectric constant and is purely dependent on the applied electric field and a field acceleration factor coming from time dependent dielectric breakdown (TDDB) measurements. The thermochemical model is contested owed to two shortcomings: i) it does not does not accurately capture the polarity dependence of BD to gate biasing in NMOS transistors [66] neither the relation to carrier energy or current density.

This uncertainty, coupled with observation of hydrogen release during BD in SiO<sub>2</sub> have led to the proposal of the hydrogen release in which the breaking of the Si=H bridge leads to the augmentation of defects and eventually leads to BD [67], [68]. Nevertheless this mechanism has been only associated to SiO2:Si systems and to my knowledge, fails to explain the oxide breakdown mechanism observed in TMOs and high-k dielectrics. To the contrary, as far as high-k and specifically the HfO<sub>2</sub> system are concerned, recent works have associated the degradation of oxide gate current and eventual breakdown of the CMOS HKMG (high-k metal gate) oxide to the generation of oxygen vacancies in the oxide [69], [70] converging to the views of the ReRAM community for the forming and set processes in TMO ReRAM.

Even though dielectric breakdown was first studied mainly owed to CMOS applications, independent groups have reported studies in MIM structures as early as the late 1950s [71]–[74] where the term of *forming process* denoting oxide dielectric breakdown was first introduced. The observation that the forming process can be (partially) reversed [75] in certain material systems and could thus induce a non-volatile, field dependent hysteresis I-V curves could be considered as one of the earliest works in the field of ReRAM.

### 1.4.3 Forming process

### 1.4.3.1 Microscopic Description of Forming

As mentioned before, resistive switching has been investigated since the early 1960s. The image of conductive filament (CF) formation, that is a localized percolation of the material phase with increased conductivity, was first suggested by Dearnaley [76]. Generating such material phases can be induced either by fabrication or by electronic breakdown. At the heart of the process, lies the transition of a perfect or a quasi-perfect oxide to a locally defect rich material where hopping conduction is facilitated as discussed previously.

From an electrochemical standpoint conductive filament formation is seen as a series of local transitions to sub stoichiometric or a super stoichiometric phases with increases conductivity. Increased conductivity can be predicted for oxides owed to the nature of redox reactions associated with the formation of point defects of either positive or negative charge. If hypo-stoichiometric phases are thermodynamically stable, then the region of the metal organic oxide (MO<sub>x</sub>) with MO<sub>x-δ</sub>  $\mu$  δ>0 leads to a surplus of electrons. This can be either due to the formation of oxygen vacancies ( $V_0^{\circ}$ ) or to the generation of metallic cation sites ( $M_1^{\circ}$ ). Both cases lead to a positively-charged center with the subsequent generation of a surplus of electrons (and oxygen in gaseous form if no secondary reactions are considered) indicating a transition to an n-type semiconductor behavior. The processes are respectively described in Kröger–Vink notation in eq. (1.3) & (1.4), respectively:

$$0_0^{\times} \to V_0^{-} + 2e' + \frac{1}{2}O_2(g)$$

(1.3)

$$M_{\rm M}^{\times} + 0_{\rm o}^{\times} \to M_{\rm i}^{-} + 2e' + \frac{1}{2}O_2(g)$$

(1.4)

By analogy, hyper stoichiometry leads to a p-type semiconductor with surplus of holes. The point-defects that carry the negative charge in this case would be oxygen interstitials (Eq. 1.5) or cation vacancies (Eq. 1.6) both carrying negative charge states:

$$\frac{1}{2}O_2(g) \to O_i^{"} + 2h^{"}$$

(1.5)

$$\frac{1}{2}O_2(g) \to O_0^{\times} + V_M'' + 2h^{\cdot}$$

(1.6)

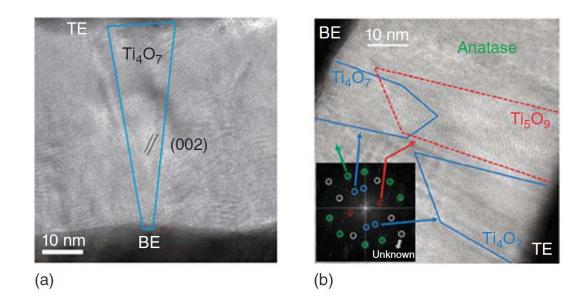

Figure 1-7 (a) Distribution gradient of sub-stoichiometric Magneli phases in  $TiO_2$  [70] (b) Magneli-phases identification through TEM diffraction pattern analysis [71]

The model of vacancy based CF was first proposed by Dearnaley and Greene [77] and involves the migration of vacancies from anode to cathode thus generating a CF connecting the two electrodes. It implicitly thus predicts the sensitivity of such a CF to both the nature of the electrode and the partial pressure of oxygen in the environment. The migration of oxygen vacancies from a vacancy rich anode through the oxide and towards the cathode was later detected in SrTiO<sub>3</sub> [78]. Furthermore, systems such as TiO<sub>2</sub> exhibit well known sub-stoichiometric regions after forming called Magneli phases where the same gradient of oxygen vacancies has been observed [79], [80]. Similar sub stoichiometric phase transitions have also been reported for Ta<sub>2</sub>O<sub>5</sub> [81].

It is also considered the dominant mechanism in HfO<sub>2</sub> based ReRAM as it explains the sensitivity of the devices to the top electrode and HfO<sub>2</sub> stoichiometry. Nevertheless, modified phases in HfO<sub>2</sub> devices have not been detected through any type of microscopic chemical analysis to date despite the strong activity in the topic. In all of the above cases, the vacancy region is considered to locally act as an n-type semiconductor. It is worth noting the case of NiO where the observed filament is attributed to Ni cation vacancies [82], [83] or the Al<sub>2</sub>O<sub>3</sub>:Cu system [84] as an example of a system where the CF is a cation vacancy and thus conduction is considered to be p-type.

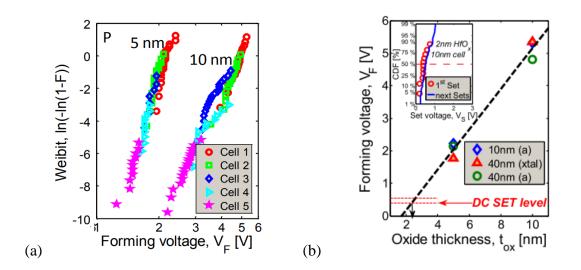

Figure 1-8 (a) Area-normalized Weibit plot of the system of HfO2(5nm)/Hf(5nm) for different oxide thicknesses and areas. (b) Impact of oxide thickness scaling o the forming voltage of  $HfO_2$ : Hf ReRAM. (Inset) Statistical range of set voltage, indicating that set is a limiting case of forming.[37]

It is interesting to note that even though clearly detectable sub-stoichiometric regions have not been detected in  $HfO_2$  (serving as a popular system for a counter- example) it has been theorized that the forming process can be seen as a local phase transition, owed to the fact that point defects are expected to quickly relax under the influence of diffusion processes as soon as the external force is stopped [85]. Hence long-term stability of the conductive properties can be justified through a transition of phase. Nevertheless, this is to date an open topic of active research. Accepting the existence of local phases in the CF is not necessarily incompatible to the image of the percolation path as described in the previous section. Indeed, the nano-sized phases observed in TiO<sub>2</sub> are of the order of 5-20 nm (Figure 1-7) or smaller in the case of systems such as the HfO<sub>2</sub>.

## 1.4.3.2 Impact of Oxide thickness and reactive electrode

Until now we have discussed the principle of the microscopic forming mechanism in TMOs. It is evident from the different reported results that the specificities of the filament nature, like its size, chemical composition and charge state of the conductive centers is heavily dependent not only in the material but also in the nature of the oxide/metal interfaces used. Whatever the specificities though, the macroscopic breakdown characteristics (exponential dependence to time and field, area and oxide thickness

*Figure 1-9 Impact of thickness scaling of the Hf reactive electrode in HfO*<sub>2</sub>:*Hf ReRAM* [37]

scaling) are well maintained denoting that the physics of the percolation path formation is predominant: The forming voltage scales with device area (Figure 1-8a, HfO<sub>2</sub>:Hf system) and follows very well the Weibull distribution for dielectric breakdown while it scales proportionately to the oxide thickness (Figure 1-8b). Interestingly though the sharpening of the Weibull slope expected for the case of the thicker oxide is not observed, contrary to the respective cases of CMOS systems (see 1.4.2). This suggests that the defects are not homogeneously distributed in the oxide.

Several works have demonstrated that inserting a reactive electrode in the cathode contact facilitates the forming process. In particular Ti, Hf, Zr (column IV elements of the periodic table) have all been shown to reduce the forming voltage of the native  $HfO_2$  sysstem or similarly Ta for the case of the  $Ta_2O_5$  system [86]. In all cases the process is facilitated and the forming voltage reduced as compared to the native system being in contact with an inert electrode such as Pt. The reactive metals are considered to have a lower migration barrier with their native binary oxides hence facilitating the oxygen exchange reaction in the metal/oxide interface. It is worth noting that oxygen segregation gradients near the cathode/oxide interface have been observed for the  $TiO_2/Pt$  system [87].

The specificities of the role of the electrodes in the microscopic mechanisms of defect

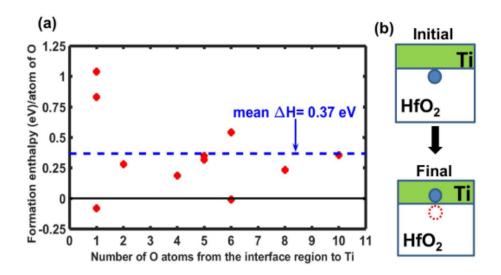

Figure 1-10 (a) Formation enthalpy of removing O from the interface region to top Ti layer. The enthalpy is divided by the number of removed O atoms for comparison (b) Pictorial model showing the process of O exchange across the interface used in studying the formation enthalpy of (a). [Traoré et al. T.ED 65(2), 2018]

generation are highly material dependent but in general it is understood that reactive metals have have a lower formation enthalpy of a sub oxide phase with an oxygen ion from the binary oxide and thus facilitate the migration of oxygen ions into the cathode electrode subsequently generating vacancies and a surplus of electrons. Traoré et. Al (amongst other groups) have studied the effect of oxygen exchange in the HfO<sub>2</sub>:Ti interface by means of density functional theory (DFT) calculation. Figure 1-10 shows the energy cost to extract O ions from the HfO<sub>2</sub>:Ti interface (formation enthalpy / atom O) as a function of the number of O ions migrating towards Ti calculated using DFT. The energy required to extract an oxygen ion is a function of the atoms extracted from the vicinity and the distance from the interface. In the graph, the highest energy values correspond in O atoms originating from layers a few atomic layers away from the interface while the zero or negative values correspond to O ions at the interface. Moreover the decreasing energy cost with increasing number of atoms can be interpreted as a lowering of the interface barrier as the oxide region near the interface becomes more substoichiometric. Given the highly local nature of DFT, this process can explain the initial stages of filament formation.

# 1.4.4 Switching Mechanism

# 1.4.4.1 Unipolar and Bipolar Switching

As briefly discussed in §1.3 post forming ReRAM devices can exhibit two modes of operation that being the bipolar or unipolar switching behavior depending on whether bias polarity needs to be reversed, respectively, in order for the device to successfully reset from LRS to HRS. Unipolar operation has been shown for several binary oxides amongst which TiO<sub>2</sub> [88][89] and HfO<sub>2</sub> [90][91]. Even though the microscopic mechanism can vary from material to material, the physical principles involved are attributed primarily to a competing behavior of drift and diffusion processes of the moving species. Moreover, systems such as HfO<sub>2</sub> can show both unipolar [34], [35] and bipolar switching [92] behavior depending on the nature of the electrodes. Finally, it is worth noting that even though filamentary switching has been reported for both unipolar and bipolar modes, there is no report of unipolar surface-dependent ReRAM system to the author's knowledge to date.

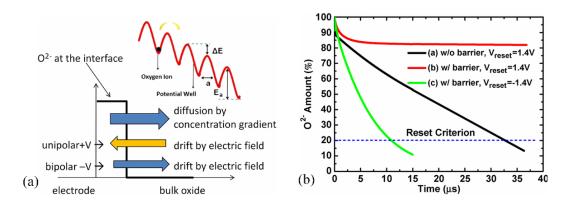

A unified semi-analytical model has been recently proposed by Yu *et al* to describe the unipolar and bipolar nature of ReRAM devices in terms of the moving species kinetics [93]. The main concept lies with modeling  $O^{2-}$  ion kinetics in terms of drift and diffusion processes. In that image the direction of the diffusion associated forces is dictated by the concentration gradient while drift forces will be mainly controlled by the field gradient. In bipolar switching drift and diffusion will act synergistically to break down the formed filaments causing ions to migrate back and either recombine with oxygen vacancies or oxidize metal precipitates. In unipolar devices however drift and diffusion will act antagonistically to each other. Lee et al. [94] have suggested that during the reset process in unipolar devices, filament dissociation is owed to a thermally activated oxidation process due to Joule self-heating, which in turn causes diffusion forces from the anode to overcome the drift forces.

Yu's model is based on the experimental observation that unipolarity is associated with noble metal interfaces whereas bipolarity with at least one reactive interface. With that in mind, it was assumed that the introduction of a reactive interface causes local oxidation in

Figure 1-11 Schematic representation of driving forces excreted on  $O^{(2-)}$  in Yu's model. Migration is assumed to occur due to  $O^{(2-)}$  hopping in subsequent potential wells in the oxide characterized by discrete energy states. In bipolar stacks drift and diffusion are assumed to act synergetically whereas in unipolar mode they act competitively to each other. (ii) Simulated  $O^{2-}$  concentration under 1.4V bias (discrete pulse) for three reset cases. Case (a): Without interfacial barrier and under positive bias, unipolar reset is successful. Case (b): With interfacial barrier and under positive bias, unipolar reset is successful. Case (c): With interfacial barrier and under negative bias, bipolar reset is successful. [94]

the reactive electrode/oxide introducing a potential barrier layer. In the absence of a barrier, oxygen ion diffusion is possible [Figure 1-11 ii-(a)] and unipolar switching is possible. The introduction of such barrier acts to block diffusion from the anode if a positive bias is applied and unipolar reset probability drops [Figure 1-11 ii-(b)]. On the other hand, under negative bias  $O^{2-}$  ions can overcome the barrier making bipolar mode possible [Figure 1-11 ii-(c)].

A diffusion process it is mainly controlled by local temperature rather than local field and is thus also known as a thermally controlled mechanism (TCM) ReRAM. It has been argued that using thinner electrodes[95] or electrodes with higher effective thermal resistance [96] could improve ReRAM characteristics (both bipolar and unipolar).

#### 1.4.4.2 Universal Switching Characteristics

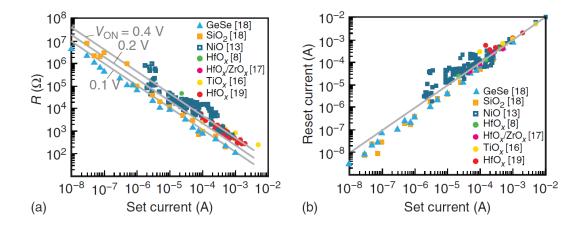

Closing this section, it is worth mentioning that no matter the material system, or its switching behavior, certain symmetries common to all resistive switching devices can be identified. Notably, it has been observed that for all VCM and ECM cells whether unipolar or bipolar, the LRS associated resistance is strongly correlated to the compliance current (maximum permitted current through the cell during set transition) (Figure 1-12a). and the maximum current during reset is also correlated to the set current (Figure 1-12b).

Figure 1-12 (a) LRS state resistance correlation (b) HRS resistance correlation to set compliance current. Switching Behavior from multiple material systems and switching mechanisms. [R. Waser, Nanoelectronics and Information technology, 2012]

Moreover, it has been reported that the switching time depends exponentially with applied voltage for both the forming process [97] and during switching [98] supporting the hypothesis of a gradual defect generation followed by a nucleation-propagation process or in equivalent terms the formation and dissolution process of the conductive filament.

Several models of varying detail have been proposed to describe the mechanism. From a compact model standpoint the variable gap or variable diameter models have been proposed; a comprehensive review can be found in [67]. It is also worth noting the approach of Nardi *et al.* in the microscopic modeling of forming and set/reset kinetics using Nerst-Planck equations for the oxygen vacancies [I had it somewhere, sandisk publication].

# 1.5 ReRAM Architectures

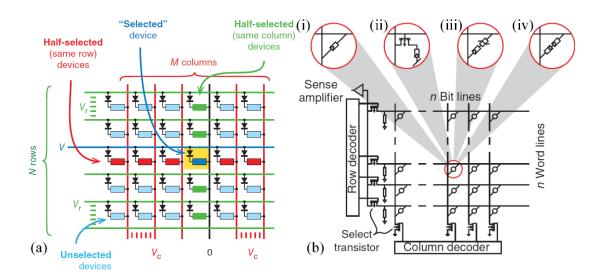

Integrating ReRAM cells in a functional large scale memory array imposes the use of an element in series with the MIM cell called a selector device. There are two reasons that impose the use of selectors in ReRAM memory array technology. From a fundamental physics prospective, the nigh-uncontrollable nature of the dielectric breakdown event occurring during the forming and set operations. If too many oxygen vacancies are generated during the forming/set process, it can lead to inability to reset and device failure. This can be especially critical for the forming operation where forming occurs at elevated voltages. As breakdown occurs, the resistance between the two terminals of the cell drops

*Figure 1-13 (a) Cross point memory array architecture and (b) different types of ReRAM cell architectures (i) 1R (ii) 1T1R (iii) 1D1R (iv) 1S1R [58]*

acutely resulting in an exponential enhancement of breakdown more commonly referred to as current overshoots [99].

From a memory array design prospective, the crosstalk between memory cells of large memory arrays, quickly becomes a limiting factor for both the size and array cell density. Figure 1-13a shows a typical configuration of a cross point memory array architecture where cells are arranged by columns and rows. There are many read and programming schemes that are being the scope of this short review. In general, a cell in the array is selected by combined biasing of its row and columns to an appropriate read or write voltage. This results in not just the selected cell to be biased but all the column and row cells as well. Even though the cells corresponding to non-intersecting biases are not optimally polarized, unwanted crosstalk can emerge: First, read and write disturb, where the applied biases not only affect the state of the selected cell, but also that of nearby cells in shared or non-shared columns and rows [100]. Second, inaccurate determination of the state of the selected or floating bias cells that collectively lower the readout resistance [101]–[103]. The latter becomes particularly limiting if an array sub-block is fully programmed in LRS, where the leakage current of each cell is the largest.

Hence, a control element (selector) is integrated in the memory cell in series to the device (1S1R) so as to both limit current overshoots and leakage current through the device as opposed to the 1R memory cell architecture (Figure 1-13i). The selector element can be

Figure 1-14 LRS and HRS device-to-device resistance cumulative distributions for different pulse heights during the SET and RESET pulsed operations.

active or passive in nature depending on if its conductive properties can be controlled independently from the memory cell by means of a bias other than the one applied on the memory cell. The active selectors to date include vertical BJTs [104], [105], or FETs [106] leading to a 1T-1R architecture approach (Figure 1-13ii). Passive selector technologies include MS Shottky diodes [107] and p-n junctions (Figure 1-13iii). Passive selectors include MIM switches whose conductive properties can be modified by means of an applied field of the same range as the memory such as oxide based nonlinear field-tunable tunnel barrier switches [108] or ovonic threshold switches (OTS) [109].

All different selector technologies come with their respective pros and cons. Notably, MOSFETs although excellent in terms of current controllability and parametrization (both by tuning transistor sizing and operating voltage) consume too much surface. On the other hand, diodes cannot be used with bipolar elements while the switching properties of passive selector elements need to be carefully engineered to fit the memory switching range. For this reason, in this work the selector of choice is the standard FET as its tunability gives enough margin to focus on the investigation of the memory cell engineering.

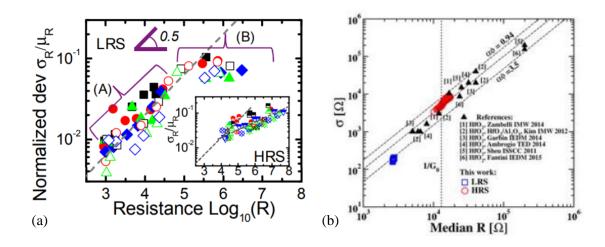

Figure 1-15 (a) Normalized relative spread of standard deviation over mean resistance for LRS and HRS as a function of the observed resistance[110] (b) Generalized sigma too median relation for both LRS and HRS from [111]

#### **1.6 Variability of the ReRAM States**

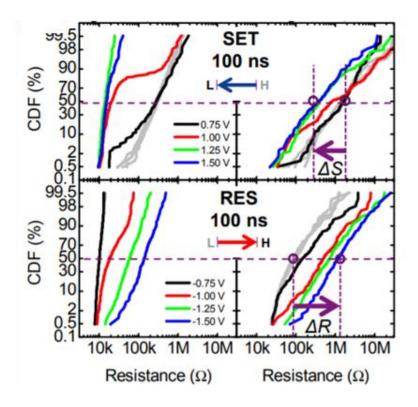

One of the major challenges for ReRAM is controlling variability of the states. Figure 1-14 shows the spread of both LRS and HRS for pulsed programming conditions; different set pulse height induces a bimodal distribution for the CDF of the LRS. The HRS is less sensitive to bimodality for varying programming conditions yet is shows a significant drift of the mean resistance with varying height of the reset voltage.

Variability in ReRAM can be traced in both intrinsic and extrinsic causes. One the one hand, the percolative nature of the filament entails that in every program-erase cycle the local inter-defect distance will be on average slightly different than the previous case. This is particularly true for HRS where the path is broken and conduction is volume-aware: After each reset, the inter-defect distance will slightly vary with respect to the previous cycle. As a result, and since conduction is controlled mainly by delocalized centers the random percolations of the initial defect configuration give rise to a large number of possible resistance states. In LRS intrinsic variability is less critical as the defect is more confined around the volume of the filament.

For filamentary ReRAM this behaviour has been modelled under the image of the quantum point contact model (QPC) attributing the totality of intrinsic variability to the different percolations of the filament near the anode [110]. In their approach, the stochastic nature of HRS and LRS is owed to the variation of number of atoms, in the "tip" of the filament to anode interface, the percolations of local distance as well as the local metal electrode

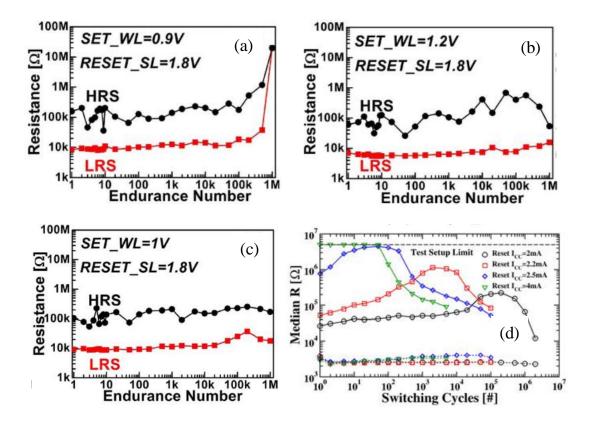

Figure 1-16 Impact of low (a), high (b) and balanced (c) set pulse height in the endurance characteristics of HfO<sub>2</sub> ReRAM cells. [112] low set voltage favors failure towards the HRS, while a high condition leads to failure towards LRS (b). (d) Impact of the Reset pulse voltage modulation through change of the series resistance of the transistor in a 1T1R 4kbit array of HfO<sub>2</sub>/Ti (10/10 nm) cells [111].

morphology. It is worth noting that such approaches do not take into account bulk material defects such as local phase transitions, interstitial impurities or local crystal dislocations that could influence the shape and conductive properties of the percolation path.

On the note of intrinsic variability, a fundamental relation between the standard deviation of the cycle-to-cycle (C2C) [Figure 1-15a] [110] or device-to-device (D2D) [Figure 1-15(b)] [111] distribution of either state has been demonstrated experimentally by separate groups. In both cases, the arbitrary potential barrier fluctuation in the anode/oxide interface has been used as the percolating parameter controlling the statistics of the resistance and its spread in the image of the QPC model. It is nevertheless important to note that the 2D QPC model fails to explain bimodality in the CDF, which is not surprising considering that a bimodal distribution is a typical property of two coexisting mechanisms in the devices, notably intrinsic and extrinsic variability. Extrinsic variability is particularly hard to model as it originates from a number of factors. Device-toenvironment interaction, such as reactive electrode or oxide to sidewall interaction locally modifying vacancy diffusivity circuit-device interactions and metal line voltage fluctuations are only some of the effects that can impact the LRS and HRS statistic. Finally, LRS seems to be more prone to bimodality and thus extrinsic variability while in HRS intrinsic variability is dominant. Unfortunately, to effectively study such fine effects populations larger than the Mbit range would be required, results for which, are not available in the literature to date.

#### 1.7 Endurance Mechanisms of TMO ReRAM

In Figure 1-16 (a)-(c) the median resistance of HRS and LRS is shown versus the accumulated programming operations in the device in pulsed operation [112]. The programming pulse width (duration) was fixed at 100ns and the pulse height during the set and reset operations was varied. The drift/diffusion effects of the active species in ReRAM and the inevitable local reconfiguration of material properties lie at the heart of the endurance / retention properties of the device. When the set voltage is too low or too high the resistance values of both states tend to drift towards those of the HRS or those of the LRS respectively. The trend is symmetrical when the reset voltage is varied for a given set condition (Figure 1-16d) or time is varied [111] [112].

This behaviour can be explained if the field controlled vacancy drift is taken into account: Each set/reset cycle will induce an ionic current of vacancies that generates the different filament percolations. If the set voltage or current compliance are higher more defects will be generated resulting in a stronger path that requires more energy to dissolve. It is interesting to note that all three parameters, notably the pulse height, pulse width and maximum current through the device, correspond to the energy transfer to generate and dissolve the percolation path ( $E_{cycle}=IVt$ ). Degradation towards HRS or LRS is inevitable as in every operation it is impossible to completely counterbalance all the defect sites generated in the previous operation. Hence, statistically, the fragile optimal equilibrium is broken: When vacancies are dominant the device is stuck to LRS while when vacancies are lost from the active zone resistance leans towards HRS. The failure towards LRS was simulated by MC by Yu et al. [113].

## 1.8 Retention Mechanisms of TMO ReRAM

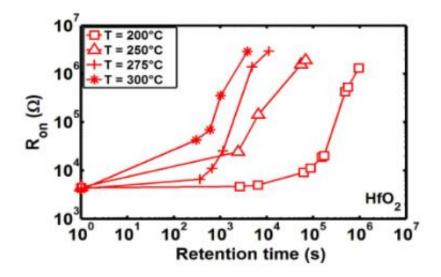

Figure 1-17 LRS media drift with time and temperature for HfO<sub>2</sub>/Ti based ReRAM [117]

Yu's work was one of the first kinetic Monte Carlo models reproducing the statistical behaviour of ReRAM in the image of the stochastic movement of oxygen ions and vacancies allowing to make predictions for both endurance and retention failure towards LRS. And while it is true that when a small number of devices are included into the statistic (like in earlier works in ReRAM) the LRS becomes the principal origin of failure [114]–[116][117] latter works in small kbit arrays point out that early HRS failures post programming are also non negligible [118].

The drift of resistance to higher values (LRS retention failure) has a monotonic behaviour and is activated with time and temperature (Figure 1-18a) -this is true for both the median values and upper quantiles suggesting one uniform mechanism at work- and can be explained by the diffusion of oxygen vacancies in the reactive electrode. On the other hand, the HRS can drift both towards higher and lower values as is usually observed between different quantiles in the HRS CDF, depending on the time the system is given to relax and ambient temperature. Lin et al. [118] have recently proposed a mechanism to explain the non-uniform evolution of the HRS drift.

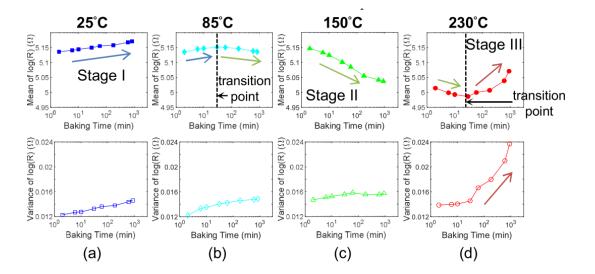

The HRS retention characteristics have been interpreted through a three stage mechanism involving two physical processes. The activation range of each stage is highly dependent

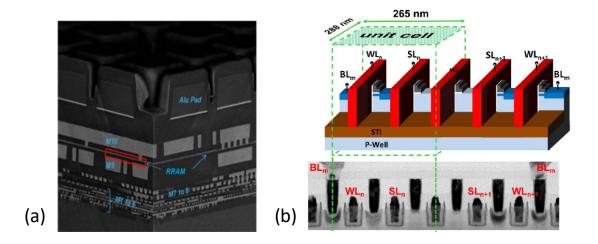

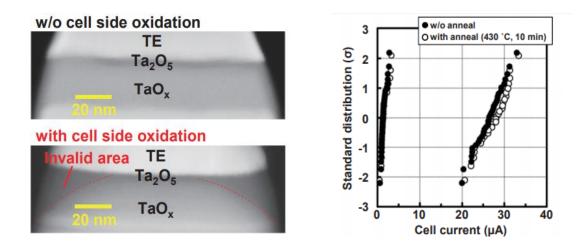

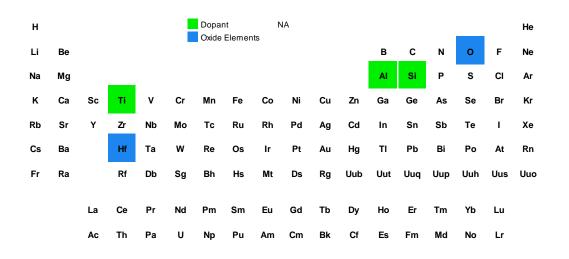

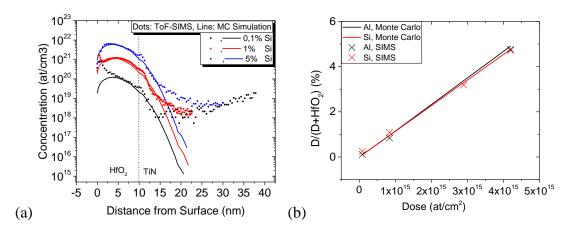

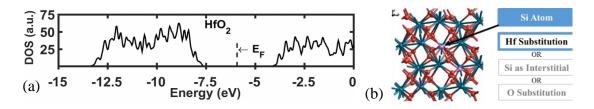

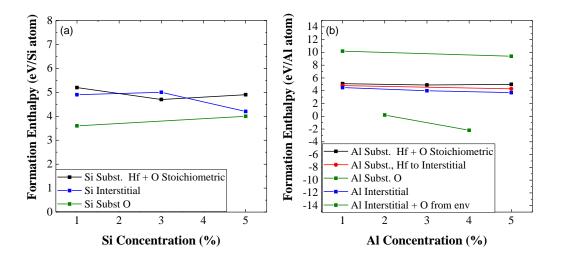

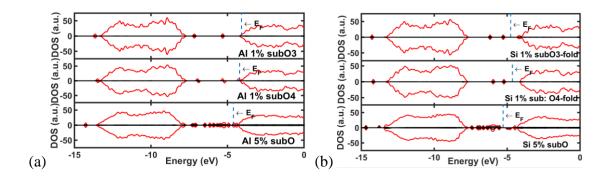

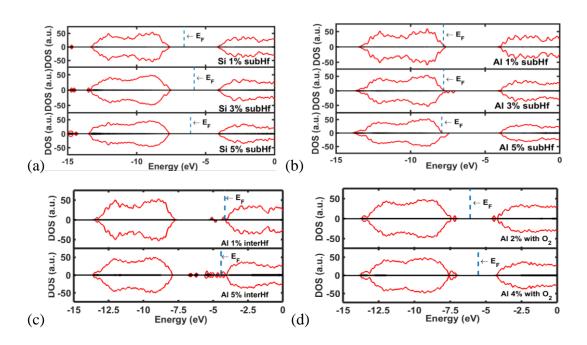

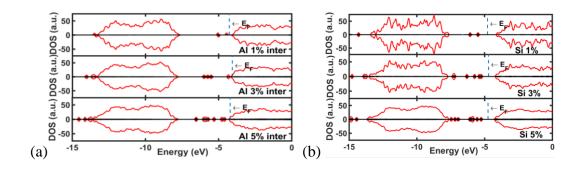

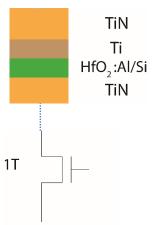

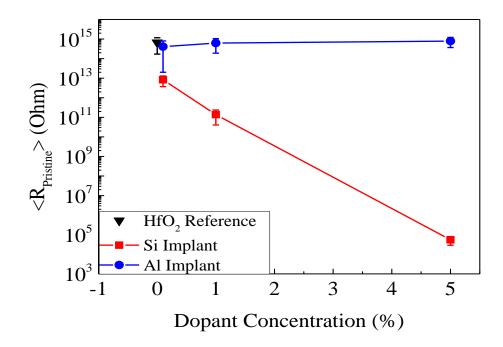

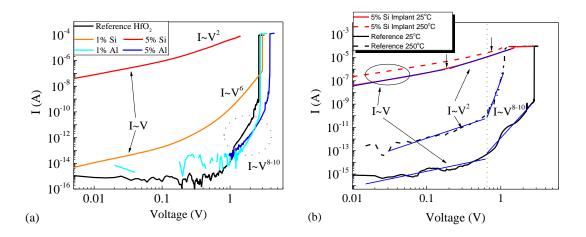

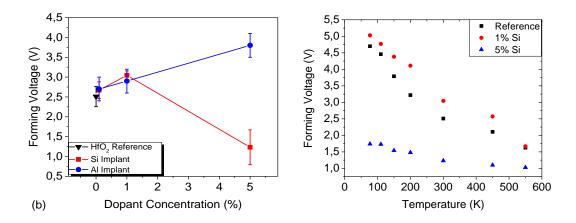

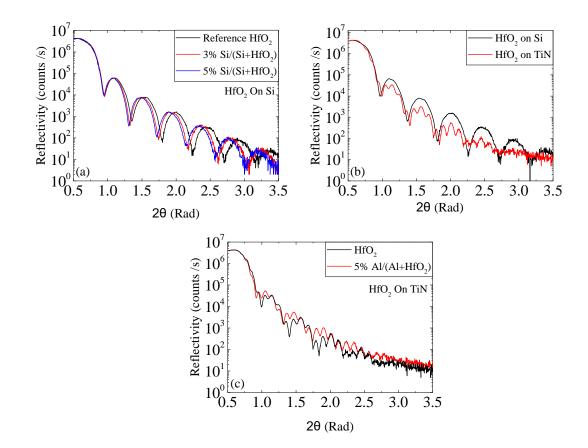

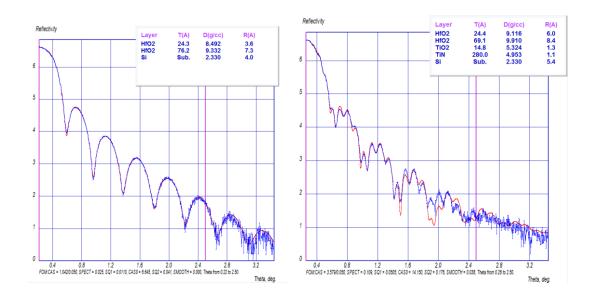

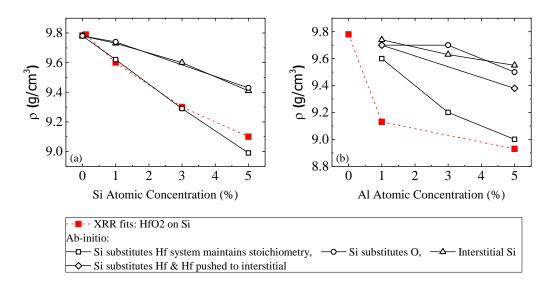

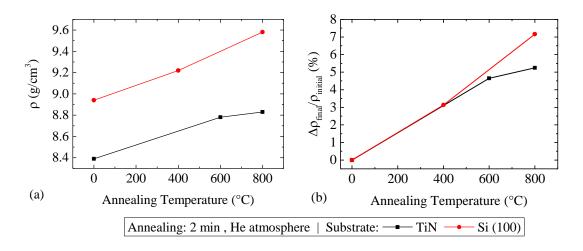

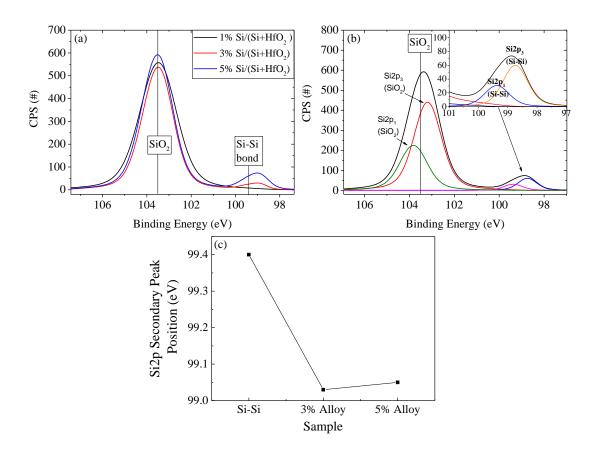

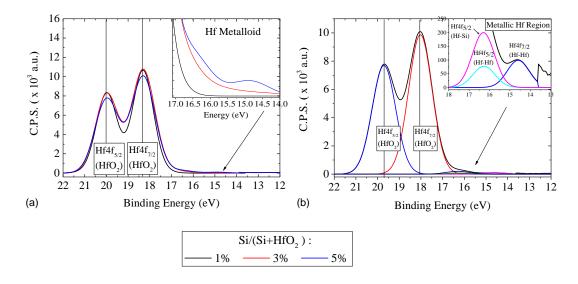

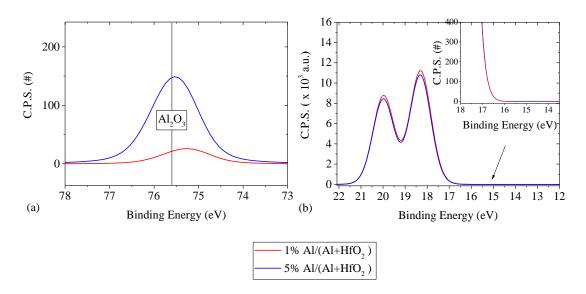

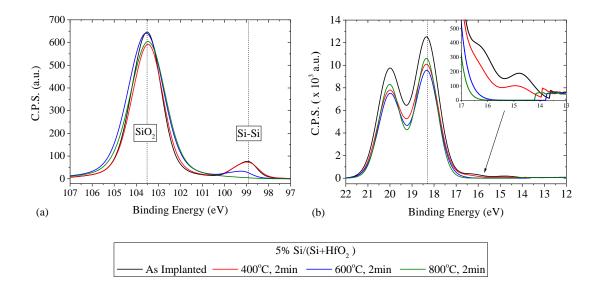

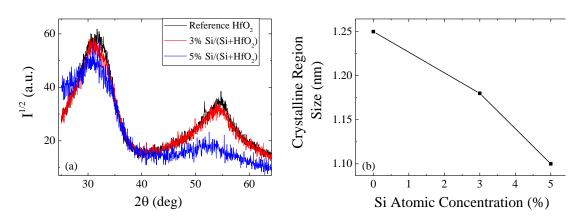

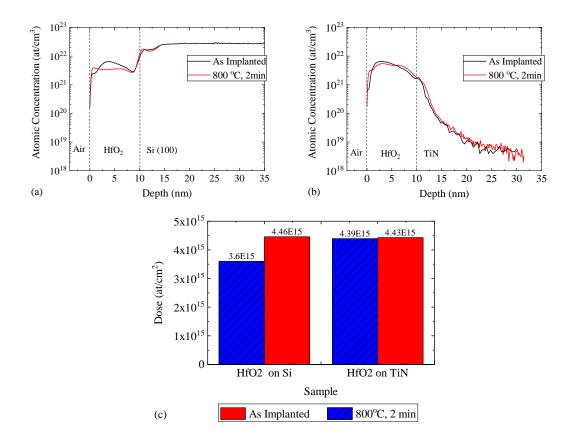

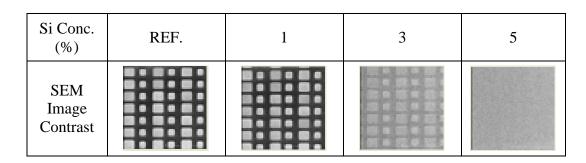

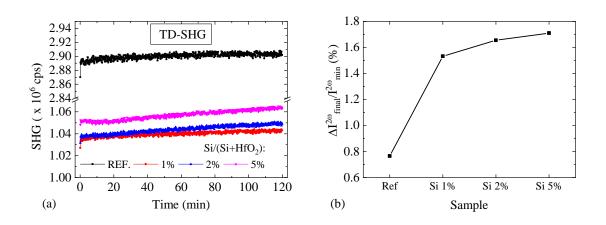

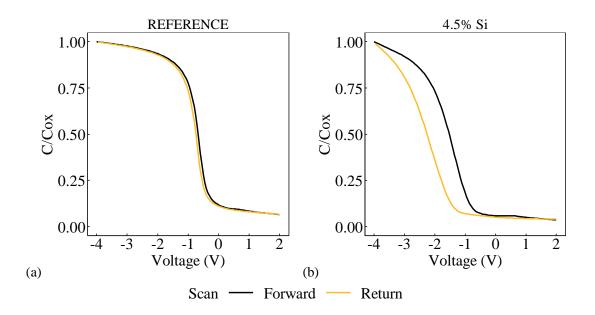

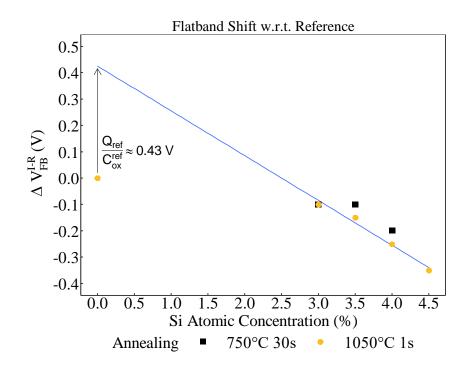

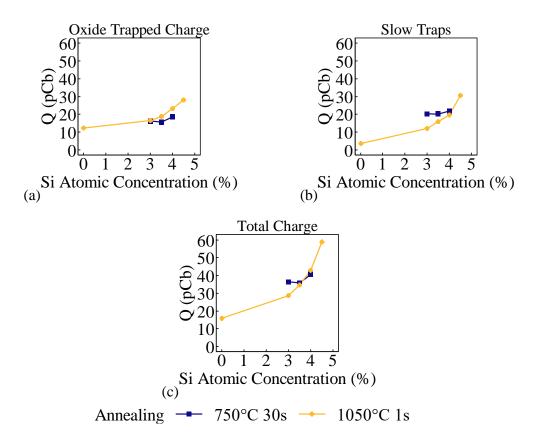

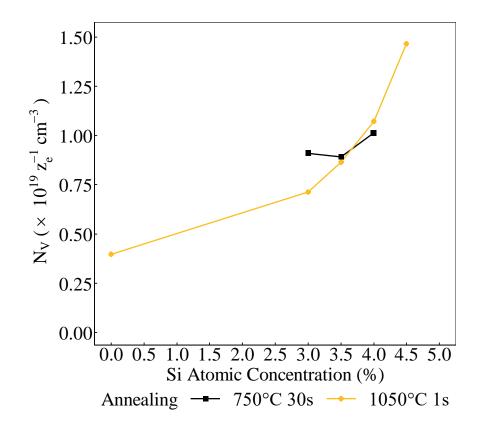

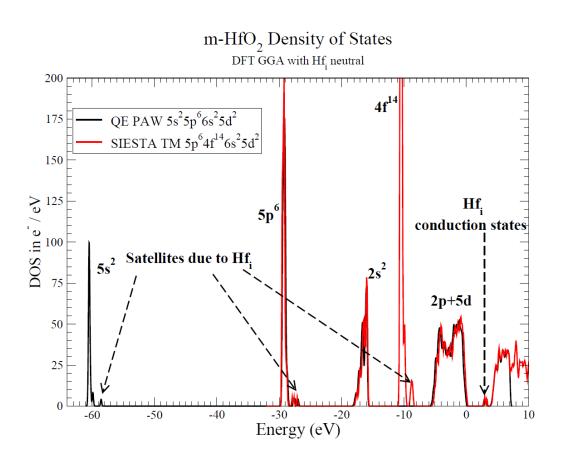

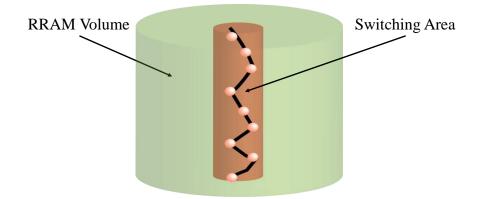

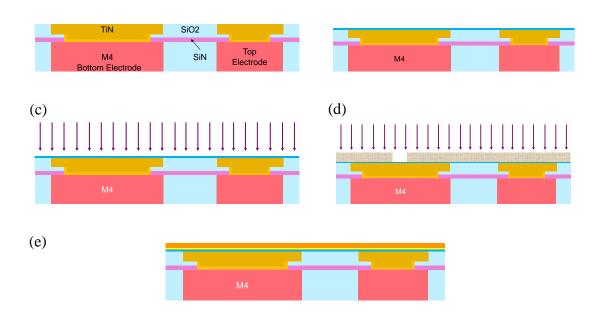

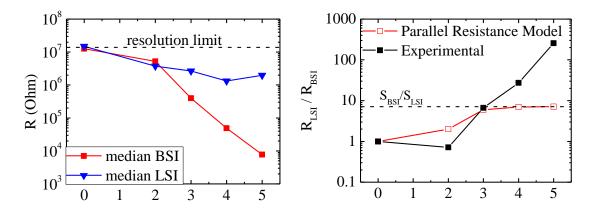

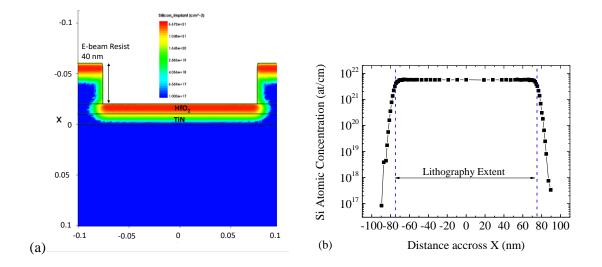

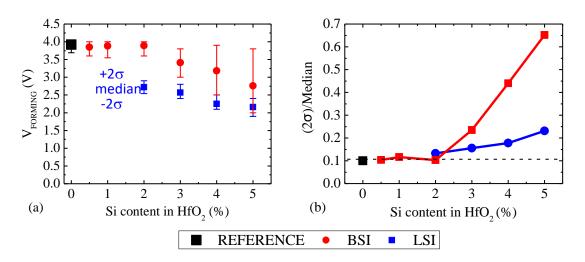

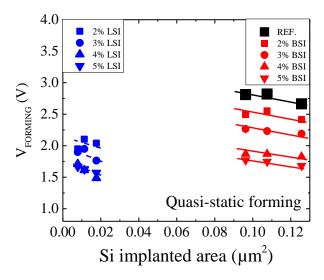

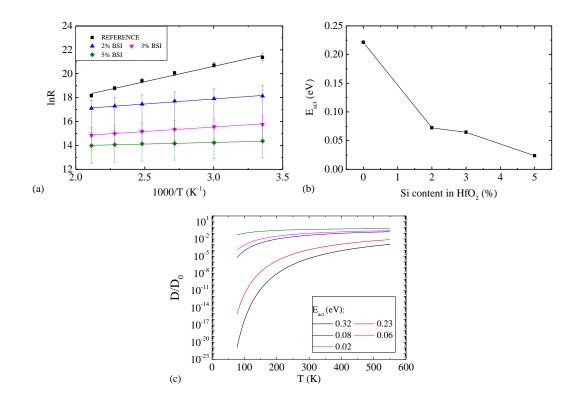

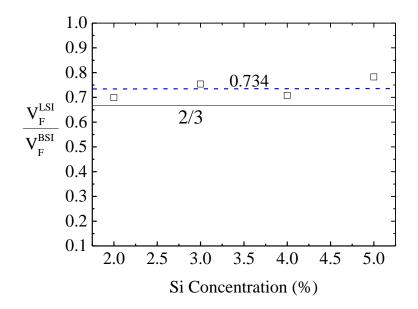

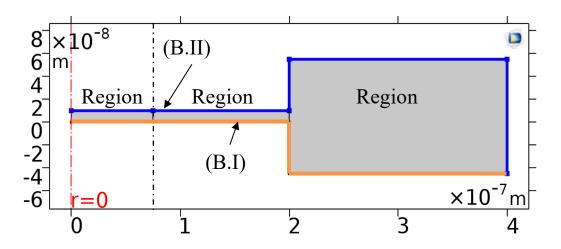

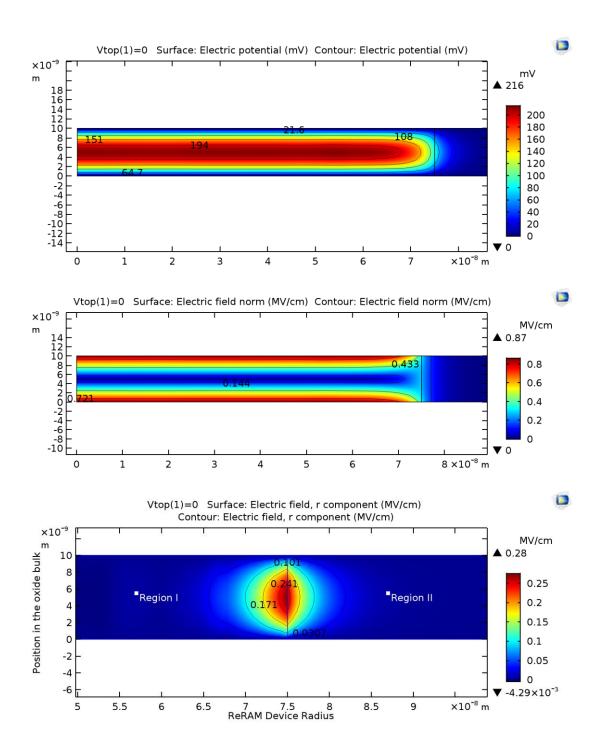

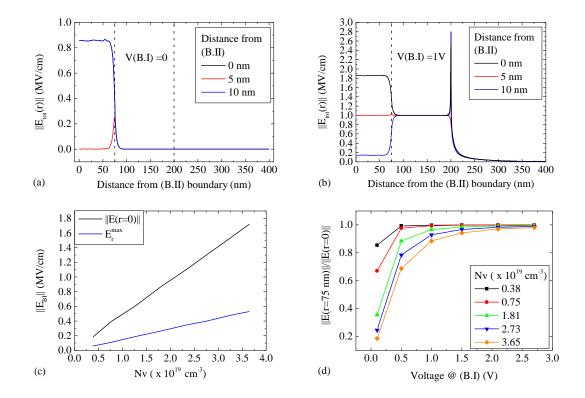

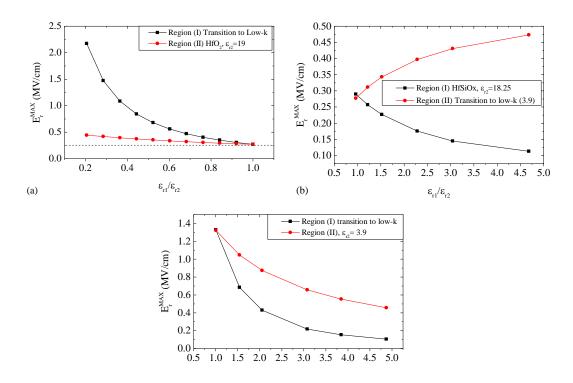

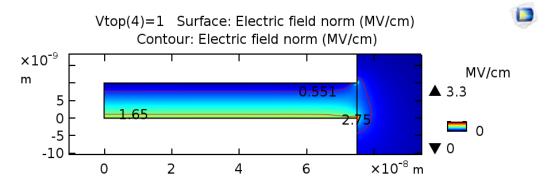

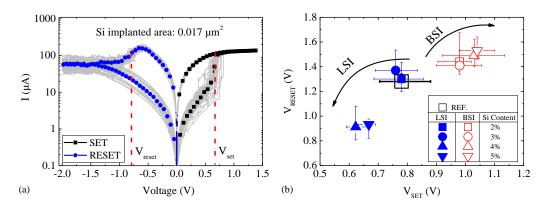

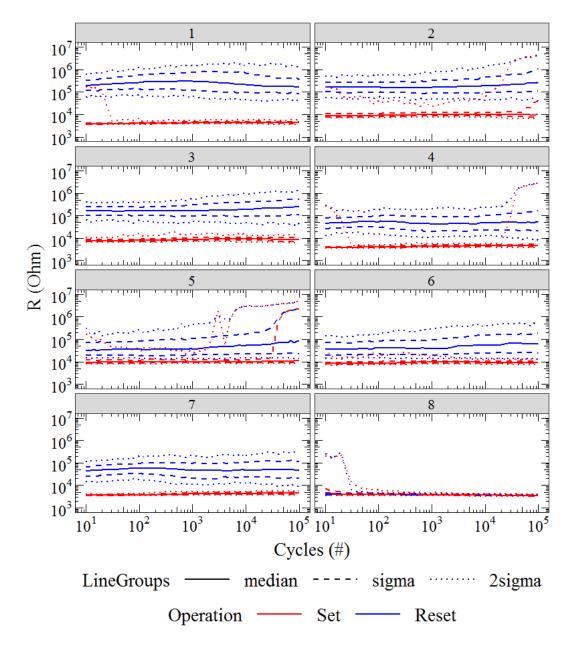

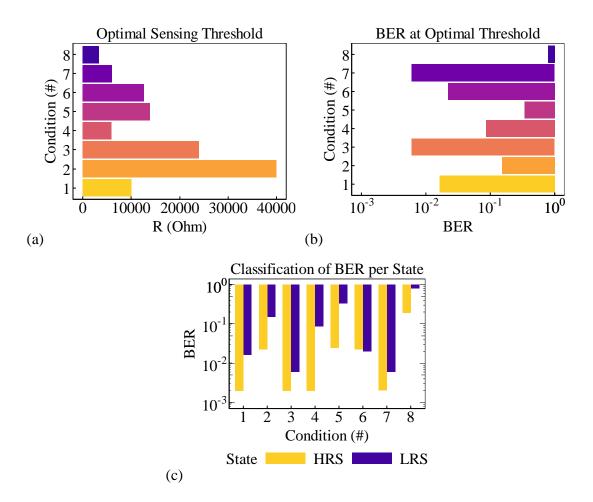

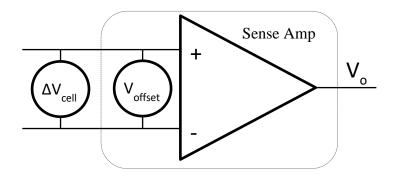

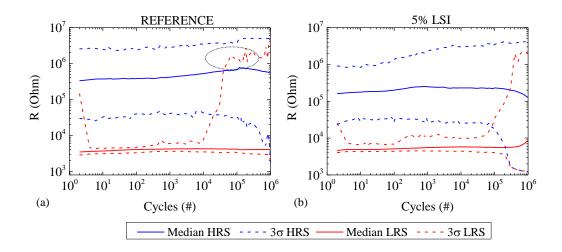

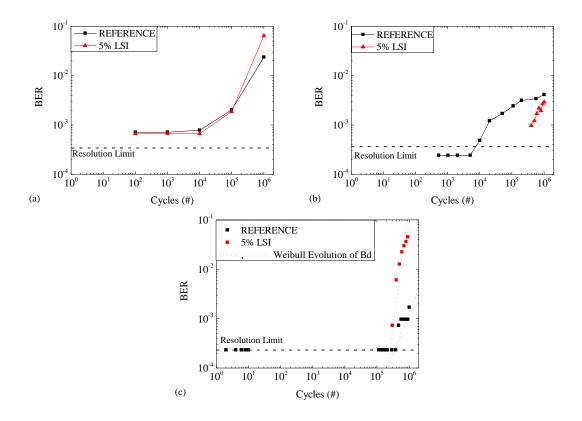

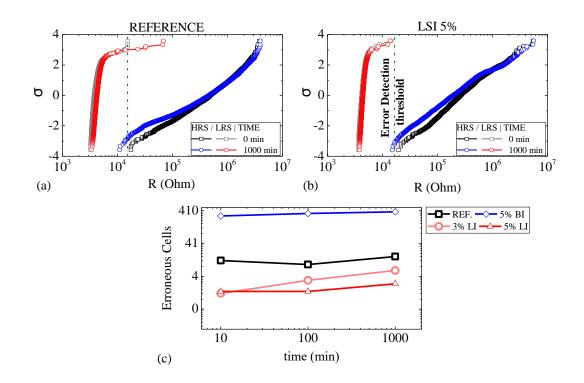

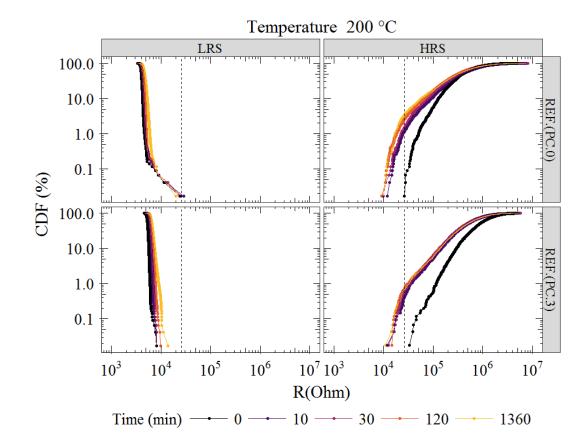

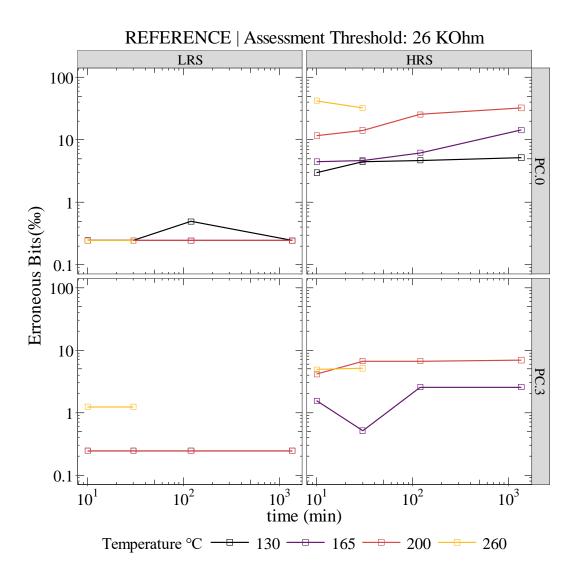

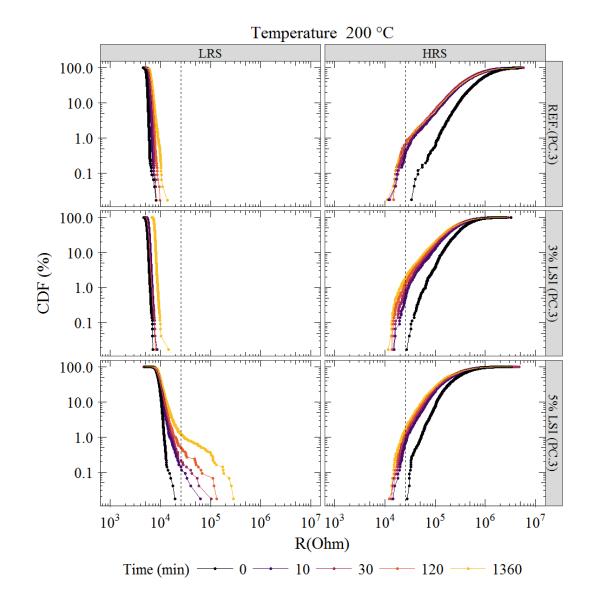

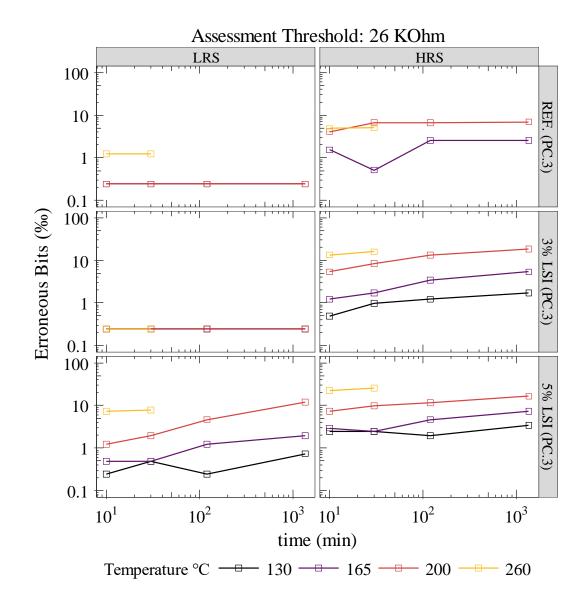

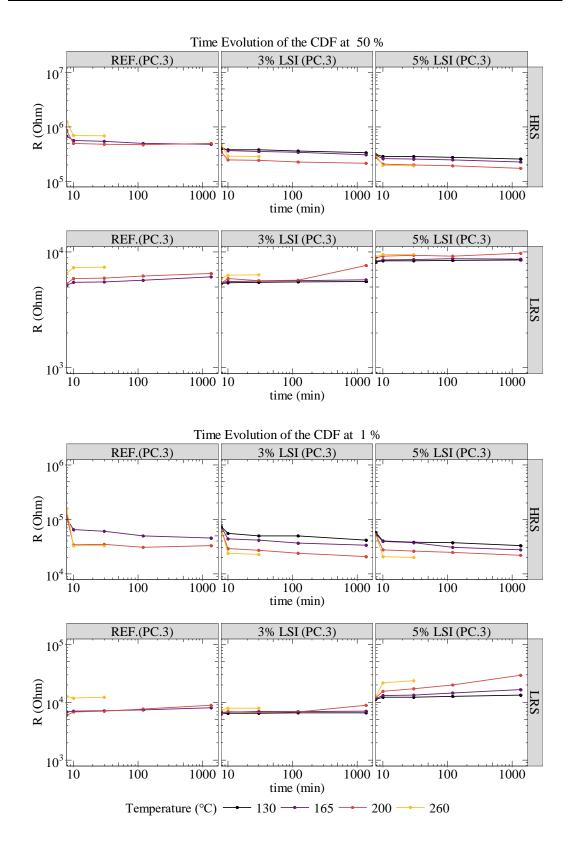

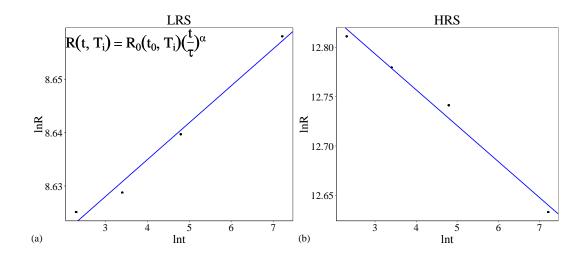

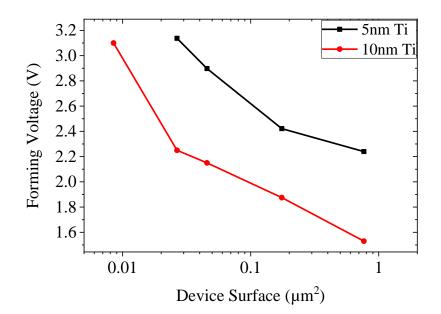

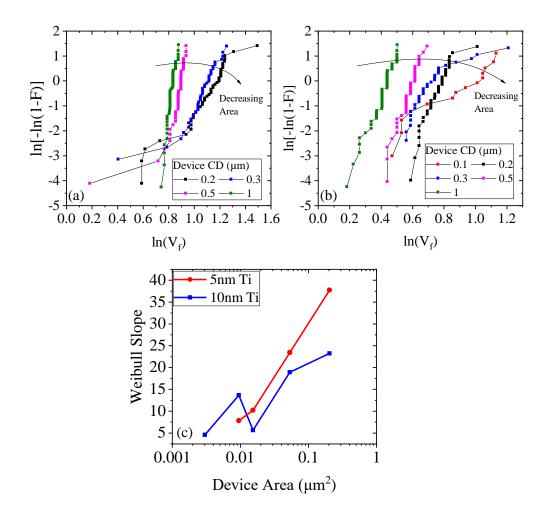

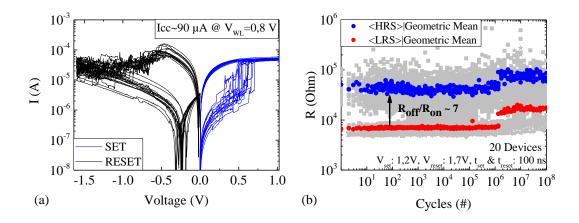

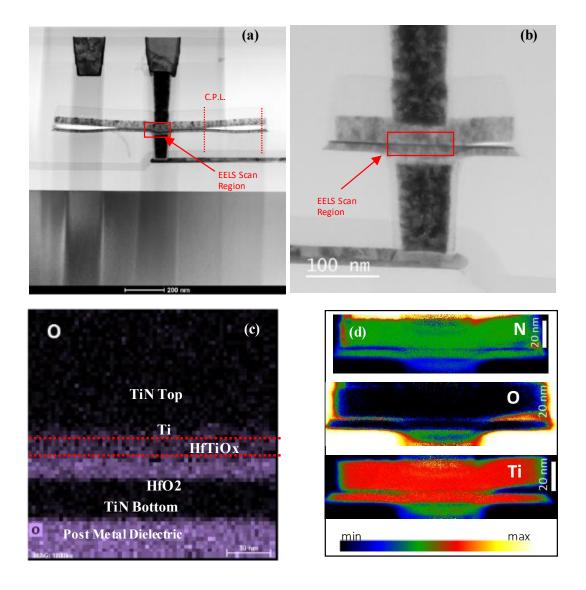

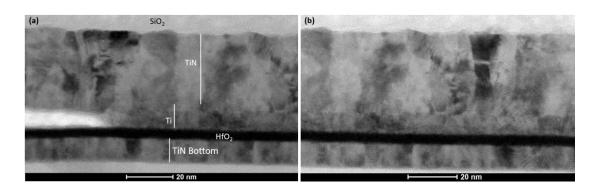

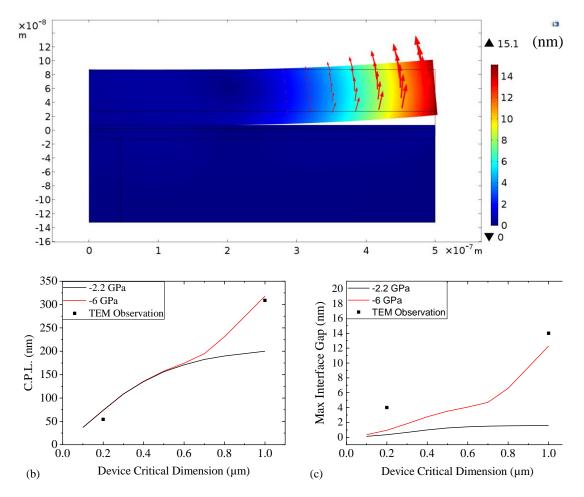

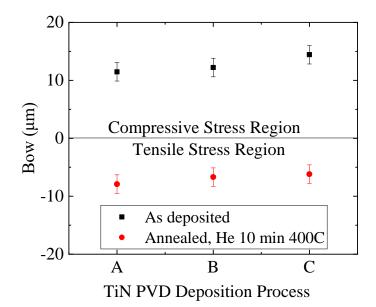

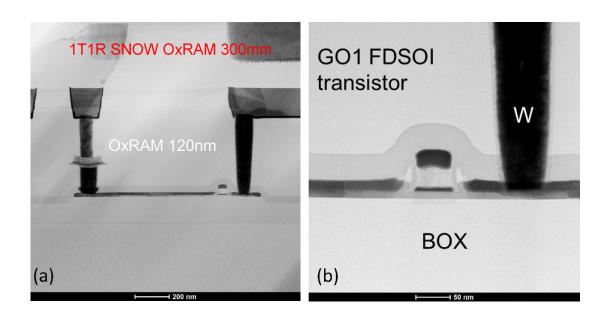

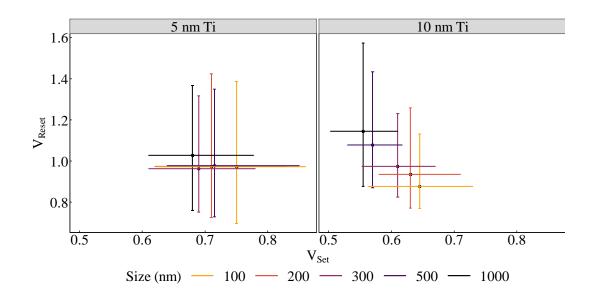

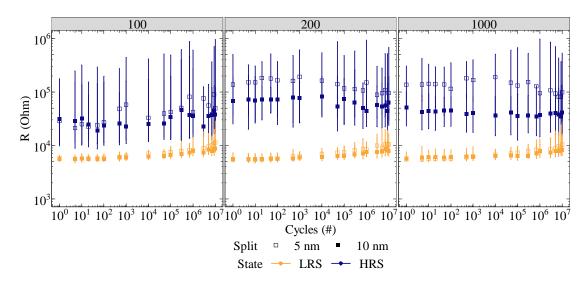

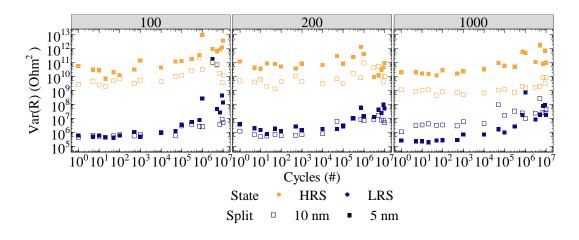

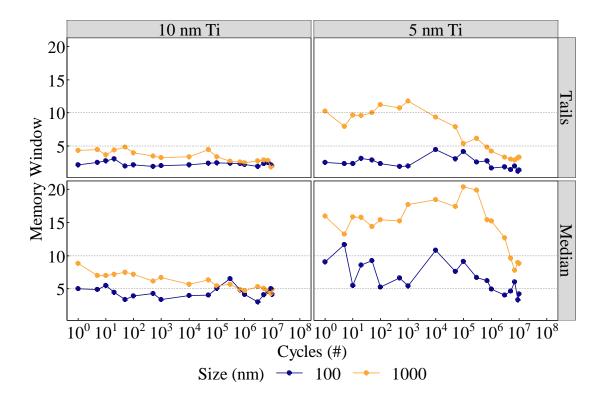

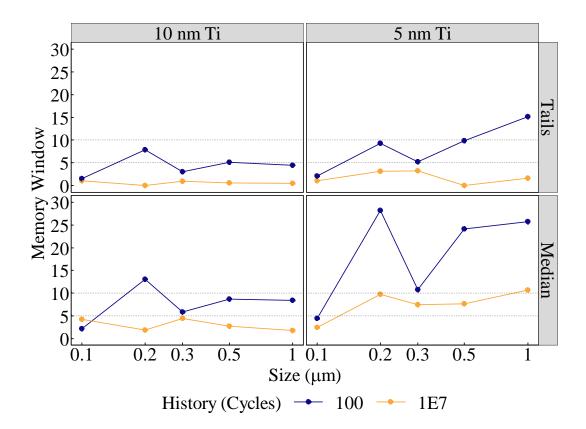

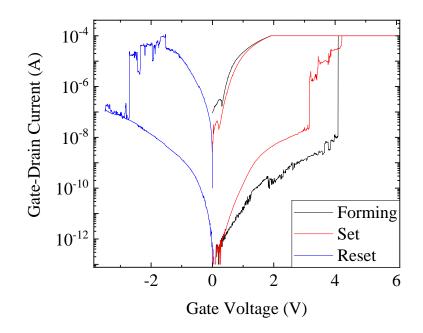

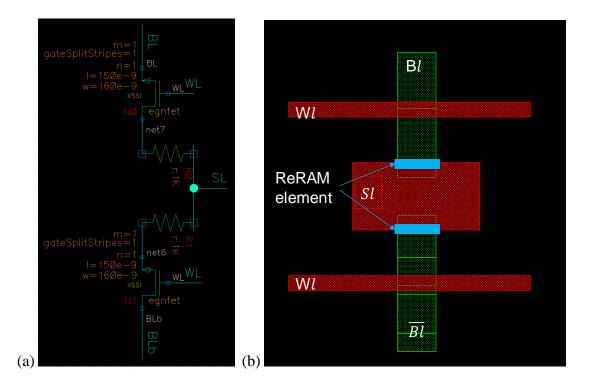

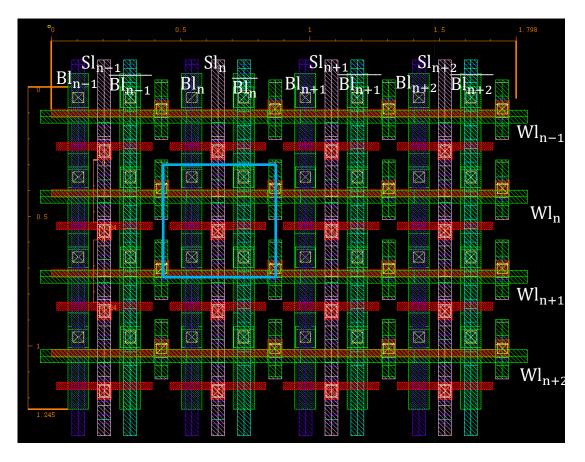

Figure 1-18 The mean and variance of the resistance distributions change with time at 25?C, 85?C, 150?C, and 230?C. First, the mean resistance increases in stage I. Then, the mean value drops in stage II. When the temperature is high enough, the stage III can be observed in a reasonable time and the mean will increase again. The variances slightly increase with time in the stages I and II but dramatically rise in the stage III. [118]