# THÈSE

présentée

à l'Université de Cergy Pontoise École Nationale Supérieure de l'Électronique de ses Applications

pour obtenir le grade de :

#### Docteur en Science de l'Université de Cergy Pontoise Spécialité : Sciences et Technologies de l'Information et de la Communication

Par

#### LE TRUNG Khoa

Équipes d'accueil : Équipe Traitement des Images et du Signal (ETIS) – CNRS UMR 8051 École Nationale Supérieure de l'Électronique et de ses Applications

Titre de la thèse

#### New Direction on Low Complexity Implementation of Probabilistic Gradient Descent Bit-Flipping Decoder

Soutenue le 03/05/2017 devant la commission d'examen composée de :

| Emmanuel Boutillon   | Professeur, Lab-STICC, Université Bretagne Sud      | Rapporteur                   |

|----------------------|-----------------------------------------------------|------------------------------|

| Chris Winstead       | Professeur, Utah University, USA                    | Rapporteur                   |

| Christophe Jégo      | Professeur, IMS, Institut Polytechnique de Bordeaux | ${ m x Examinateur}$         |

| Charly Poulliat      | Professeur, INP-ENSEEIHT Toulouse                   | Examinateur                  |

| Valentin Savin       | Dr., CEA-LETI, MINATEC, Grenoble                    | $\operatorname{Examinateur}$ |

| Fakhreddine Ghaffari | MCF, Université de Cergy Pontoise                   | Encadrant                    |

| David Declercq       | Professeur, ENSEA, Université de Cergy Pontoise     | Directeur de thèse           |

Dành cho Ba Má thân yêu của con, Ba Lê Trung Nhân và Má Nguyễn Thị Kim Chấn

> Dành cho Chị và các em, Dành cho vợ và con gái yêu dấu,

Cho tình thương của bố, mẹ dành cho con Cho tình yêu của Chị và các em, Cho tình yêu của Vợ và con

> To my parents, To my brothers and sisters, To my wife and daughter, For your love,

À mes parents, À mes frères et soeurs, À ma femme et ma pettite fille,

# Acknowledgment

I would like to express my deep gratitude to my advisors, Prof. David Declercq and Assoc. Prof. Fakhreddine Ghaffari, for their continuously guidance, support and corrections throughout the duration of my PhD work. In particular, I would like to thank them for believing in my potential and agreeing to become my doctoral advisors, for providing meaningful ideas, for initiating fruitful collaborations with partners which enabled me to finish my thesis successfully.

I would like to thank Prof. Emmanuel Boutillon and Prof. Chris Winstead for acting as my thesis reviewers, Prof. Christophe Jégo for serving as the president of the PhD committee and Prof. Charly Poulliat, Dr. Valentin Savin for being the examiners. The comments and corrections from the committee helped me significantly improve my thesis as well as my future career.

During my PhD study, I had the opportunities of doing some research visits to Error Correction Coding Laboratory in University of Arizona, USA, under supervision of Prof. Bane Vasíc. I would like to thank him for all of his supports, for providing me with very interesting ideas and discussions. I want to thank Xin Xiao, Nithin, Mohsen for discussing with me. For the research visit to University Politehnica Timisoara, Romania, I would like to thank Oana Boncalo and Alexandru Amaricai for their help and discussions .

I extend my thanks to all the colleagues in ETIS, ENSEA for their friendship, funs and encouragements especially Lam Nguyen, Hong Phan, Diouf Madiagne, Alexandre Marcastel.. and Truong Nguyen-Ly from CEA-LETI, Grenoble. The administrate assistant of our laboratory, Annick Bertinoti, and administrative assistant of the doctoral school, Emmanuelle Travet, Naima Chalabi, were always very helpful. Many thanks go to them for taking care of the administrative issues.

I would like to express my sincere gratitude to my colleagues in University of Technology (Bach Khoa University), Viet Nam National University Ho Chi Minh City, especially Ho Trung My, Huynh Thu, Hoang Trang, Do Hong Tuan, Duong Hoai Nghia for encouraging me to pursue the PhD study.

Last, but not least, my profound gratitude to my family, especially my beloved parents, Le Trung Nhan and Nguyen Thi Kim Chan, my brothers and sisters, Thanh Huong, Ngoc Lan, Minh Tuong, Trung Nghia, my wife, Van Nga and especially my lovely daughter, Sophie Vinh An, for their moral supports and encouragement throughout my life. They have inspired me and given me strength throughout my whole life.

Cergy - France, May 2017 LE TRUNG KHOA

# Author's publications related to the PhD

#### **Published** papers

- [J1] K. Le, F. Ghaffari, D. Declercq and B. Vasić, "Efficient Hardware Implementation of Probabilistic Gradient Descent Bit-Flipping", *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. PP, no. 99, pp. 1-12, 2016.

- [C1] K. Le, D. Declercq, F. Ghaffari, C. Spagnol, E. Popovici, P. Ivanis and B. Vasíc, "Efficient realization of probabilistic gradient descent bit flipping decoders", 2015 IEEE International Symposium on Circuits and Systems (IS-CAS), pp. 1494-1497, May 2015.

- [C2] K. Le, F. Ghaffari, D. Declercq and B. Vasić, "Hardware Optimization of the Perturbation for Probabilistic Gradient Descent Bit Flipping Decoders", 2017 IEEE International Symposium on Circuits and Systems (ISCAS), May 2017 (accepted).

- [C3] B. Vasić, P. Ivanis, D. Declercq and K. Le, "Approaching Maximum Likelihood Performance of LDPC Codes by Stochastic Resonance in Noisy Iterative Decoders", *Information Theory and Applications Workshop (ITA 2016)*, San Diego, CA, Feb. 2016.

#### Participation to research projects

The author participated to the research project "Innovative Reliable Chip Designs from Low-Powered Unreliable Components" (i-RISC), supported by the European Commission under the Seventh Framework Programme (Grant agreement number 309129) and the research project "Message passing Iterative Decoders based on Imprecise Arithmetic for Multi-Objective Power-Area-Delay Optimization" (DIAMOND) supported by the Agence National de la Recherche (ANR) under the Franco-Romanian (ANR-UEFISCDI) Join Research Program.

## Résumé

L'algorithme de basculement de bits à descente de gradient probabiliste (Probabilistic Gradient Descent Bit Flipping - PGDBF) est récemment introduit comme un nouveau type de décodeur de décision forte pour le code de contrôle de parité à faible densité (Low Density Parity Check - LDPC) appliqué au canal symétrique binaire. En suivant précisément les étapes de décodage du décodeur déterministe Gradient Descent Bit-Flipping (GDBF), le PGDBF intègre en plus la perturbation aléatoire dans l'opération de basculement des Nœuds de Variables (VNs) et produit ainsi une performance de décodage exceptionnelle qui est meilleure que tous les décodeurs à basculement des bits (Bit Flipping - BF) connus dans la littérature, et qui approche les performances du décodeur de décision souple. Nous proposons dans cette thèse plusieurs implémentations matérielles du PGDBF, ainsi qu'une analyse théorique de sa capacité de correction d'erreurs. Avec une analyse de chaîne de Markov du décodeur, nous montrons qu'en raison de l'incorporation de la perturbation aléatoire dans le traitement des VNs, le PGDBF s'échappe des états de piégeage qui empêchent sa convergence. De plus, avec la nouvelle méthode d'analyse proposée, la performance du PGDBF peut être prédite et formulée par une équation de taux de trames erronées en fonction du nombre des itérations, pour un motif d'erreur donné. L'analyse fournit également des explications claires sur plusieurs phénomènes de PGDBF tels que le gain de re-décodage (ou de redémarrage) sur un motif d'erreur reçu. La problématique de l'implémentation matérielle du PGDBF est également abordée dans cette thèse. L'implémentation classique du décodeur PGDBF, dans laquelle un générateur de signal probabiliste est ajouté au-dessus du GDBF, est introduite avec une augmentation inévitable de la complexité du décodeur. Plusieurs procédés de génération de signaux probabilistes sont introduits pour minimiser le surcoût matériel du PGDBF. Ces méthodes sont motivées par l'analyse statistique qui révèle les caractéristiques critiques de la séquence aléatoire binaire requise pour obtenir une bonne performance de décodage et suggérer les directions possibles de simplification. Les résultats de synthèse montrent que le PGDBF déployé avec notre méthode de génération des signaux aléatoires n'a besoin qu'une très faible complexité supplémentaire par rapport au GDBF tout en gardant les mêmes performances qu'un décodeur PGDBF théorique. Une implémentation matérielle intéressante et particulière du PGDBF sur les codes LDPC quasi-cyclique (QC-LDPC) est proposée dans la dernière partie de la thèse. En exploitant la structure du QC-LDPC, une nouvelle architecture pour implémenter le PGDBF est proposée sous le nom d'architecture à décalage des Nœuds de Variables (Variable-Node Shift Architecture - VNSA). En implémentant le PGDBF par VNSA, nous montrons que la complexité matérielle du décodeur est même inférieure à celle du GDBF déterministe tout en préservant la performance de décodage aussi élevée que celle fournie par un PGDBF théorique. Enfin, nous montrons la capacité de cette architecture VNSA à se généraliser sur d'autres types d'algorithmes de décodage LDPC.

### Abstract

Probabilistic Gradient Descent Bit Flipping (PGDBF) algorithm have been recently introduced as a new type of hard decision decoder for Low-Density Parity-Check Code (LDPC) applied on the Binary Symmetric Channel. By following precisely the decoding steps of the deterministic Gradient Descent Bit-Flipping (GDBF) decoder, PGDBF additionally incorporates a random perturbation in the flipping operation of Variable Nodes (VNs) and produces an outstanding decoding performance which is better to all known Bit Flipping decoders, approaching the performance of soft decision decoders. We propose in this thesis several hardware implementations of PGDBF, together with a theoretical analysis of its error correction capability. With a Markov Chain analysis of the decoder, we show that, due to the incorporation of random perturbation in VN processing, the PGDBF escapes from the trapping states which prevent the convergence of decoder. Also, with the new proposed analysis method, the PGDBF performance can be predicted and formulated by a Frame Error Rate equation as a function of the iteration, for a given error pattern. The analysis also gives a clear explanation on several phenomenons of PGDBF such as the gain of re-decoding (or restarting) on a received error pattern. The implementation issue of PGDBF is also addressed as a main part in this thesis. The conventional implementation of PGDBF, in which a probabilistic signal generator is added on top of the GDBF, is shown with an inevitable increase in hardware complexity. Several methods for generating the probabilistic signals are introduced which minimize the overhead complexity of PGDBF. These methods are motivated by the statistical analysis which reveals the critical features of the binary random sequence required to get good decoding performance and suggesting the simplification directions. The synthesis results show that the implemented PGDBF with the proposed probabilistic signal generator method requires a negligible extra complexity with the equivalent decoding performance to the theoretical PGDBF. An interesting and particular implementation of PGDBF for the Quasi-Cyclic LDPC (QC-LDPC) is shown in the last part of the thesis. Exploiting the structure of QC-LDPC, a novel architecture to implement PGDBF is proposed called Variable-Node Shift Architecture (VNSA). By implementing PGDBF with VNSA, it is shown that the decoder complexity is even smaller than the deterministic GDBF while preserving the decoding performance as good as the theoretical PGDBF. Furthermore, VNSA is also shown to be able to apply on other types of LDPC decoding algorithms.

# Contents

| 1        | $\mathbf{Intr}$ | oduction                                                             | 1  |

|----------|-----------------|----------------------------------------------------------------------|----|

|          | 1.1             | Context and motivations                                              | 1  |

|          | 1.2             | Main contributions and thesis outline                                | 3  |

| <b>2</b> | Har             | d decision decoders                                                  | 7  |

|          | 2.1             | Low-Density Parity-Check codes and channel models                    | 8  |

|          |                 | 2.1.1 Low-Density Parity-Check codes                                 | 8  |

|          |                 | 2.1.2 LDPC decoding concepts                                         | 9  |

|          |                 | 2.1.3 The channel models of LDPC decoding                            | 10 |

|          |                 | 2.1.4 Quasi-cyclic Low-Density Parity-Check codes                    | 10 |

|          | 2.2             | Bit-Flipping-based Decoders                                          | 12 |

|          |                 | 2.2.1 Energy computation in BF decoders                              | 13 |

|          |                 | 2.2.2 Flipping strategies                                            | 16 |

|          |                 | 2.2.3 Probabilistic Bit Flipping                                     | 18 |

|          |                 | 2.2.4 Performance comparisons                                        | 18 |

|          | 2.3             | Other Diversities of Hard decision Decoders                          | 20 |

|          |                 | 2.3.1 Gallager-A/Gallager-B decoders                                 | 20 |

|          |                 | 2.3.2 Majority voting decoder                                        | 21 |

|          |                 | 2.3.3 Differential Decoders                                          | 22 |

|          | 2.4             | The noise-aided BF decoders                                          | 23 |

|          |                 | 2.4.1 Noisy Gradient Descent Bit-Flipping decoding algorithm         | 24 |

|          |                 | 2.4.2 Probabilistic Gradient Descent Bit-Flipping decoding algorithm | 24 |

|          | 2.5             | Hardware complexity of BF-based decoders                             | 26 |

|          | 2.6             | Conclusion                                                           | 28 |

| 3        | The             | oretical analysis of Probabilistic Gradient Descent Bit Flipping     | 29 |

|          | 3.1             | Introduction                                                         | 29 |

|          | 3.2             | Markov Chain representation of the decoding process                  | 30 |

|          |                 | 3.2.1 Markov Chain of hard decision decoding process                 | 30 |

|          |                 | 3.2.2 Markov chain representation: GDBF and PGDBF illustrations      | 31 |

|          |                 | 3.2.2.1 Error patterns weight-1 and weight-2                         | 31 |

|          |                 | 3.2.2.2 Weight-3 error pattern                                       | 33 |

|          |                 | 3.2.2.3 Weight-4 error pattern                                       | 34 |

|          | 3.3             | Frame Error Rate Evaluation                                          | 35 |

|          |                 | 3.3.1 Markov Chain, algebraic and graph-theoretic considers          | 35 |

|          |     | 3.3.2 Classification of the states                                   | 36   |

|----------|-----|----------------------------------------------------------------------|------|

|          |     | 3.3.3 Frame Error Rate Computation                                   | 39   |

|          | 3.4 | Performance of Probabilistic Gradient Descent Bit Flipping Decoder . | 40   |

|          |     | 3.4.1 The asymptotic decoding performance of PGDBF                   | 40   |

|          |     | 3.4.2 The decoding performance of PGDBF in finite number of it-      |      |

|          |     | eration                                                              | 44   |

|          | 3.5 | Conclusion                                                           | 45   |

|          |     |                                                                      |      |

| 4        |     | cient hardware implementation of Probabilistic Gradient De-          | 4 17 |

|          |     | nt Bit Flipping                                                      | 47   |

|          | 4.1 | Introduction                                                         | 47   |

|          | 4.2 | The statistical analysis of PGDBF decoder                            | 47   |

|          |     | 4.2.1 Waterfall analysis                                             | 48   |

|          | 4.0 | 4.2.2 Error-floor analysis                                           | 49   |

|          | 4.3 | The optimized hardware implementation                                | 52   |

|          |     | 4.3.1 PGDBF global architecture                                      | 52   |

|          |     | 4.3.2 Implementation of the perturbation block                       | 53   |

|          |     | 4.3.2.1 Cyclically-shift truncated sequences                         | 53   |

|          |     | 4.3.2.2 Initialization with Linear Feedback Shift Register           | 55   |

|          |     | 4.3.2.3 Initialization with The Intrinsic-Valued Random Gen-         |      |

|          |     | erator                                                               | 57   |

|          |     | 4.3.3 The optimized architecture of the maximum finder               | 59   |

|          | 4.4 | Synthesis results                                                    | 60   |

|          |     | 4.4.1 PGDBF Synthesis Results                                        | 60   |

|          |     | 4.4.2 PGDBF Performance                                              | 64   |

|          | 4.5 | Conclusion                                                           | 68   |

| <b>5</b> | Δ ( | Quasi-Cyclic friendly architecture for LDPC decoders : the           |      |

| Ŭ        |     | iable-Node Shift Architecture                                        | 69   |

|          | 5.1 | Introduction                                                         | 69   |

|          | 5.2 | The Variable-Node Shift Architecture                                 | 70   |

|          | 0   | 5.2.1 The Conventional Architecture of QC-LDPC decoders              | 70   |

|          |     | 5.2.2 The Variable-Node Shift Architecture for QC-LDPC decoders      | 72   |

|          | 5.3 | The Variable-Node Shift Architecture for edge-type memory LDPC       | 12   |

|          | 0.0 | decoders: flooding MS and layered MS implementation illustrations .  | 74   |

|          | 5.4 | The Variable-Node Shift Architecture for node-type memory LDPC       |      |

|          | 0.1 | decoders: GDBF implementation illustration                           | 76   |

|          | 5.5 | The advantages of VNSA-based LDPC decoders with different type       | 10   |

|          | 0.0 | of VNUs                                                              | 80   |

|          | 5.6 | Implementations of PGDBF with Variable-Node Shift Architecture       | 82   |

|          | 0.0 | 5.6.1 The implementation of PGDBF with Variable-Node Shift Ar-       | 02   |

|          |     | chitecture                                                           | 82   |

|          |     | 5.6.2 An imprecise implementation of PGDBF with Variable-Node        | 04   |

|          |     | Shift Architecture                                                   | 86   |

|          | 5.7 | The synthesis results and decoding performance                       | 87   |

|          | 0.1 | The synthesis results and decoding performance                       | 01   |

|              | 5.8   | 5.7.1<br>5.7.2<br>Conclu | Synthesis results                                                                                                                                                                                             | 88  |

|--------------|-------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6            | Con   | clusio                   | and perspectives                                                                                                                                                                                              | 93  |

| ар           | pend  | lix                      |                                                                                                                                                                                                               | 95  |

| $\mathbf{A}$ |       |                          |                                                                                                                                                                                                               | 97  |

|              | A.1   |                          | LDPC codes used in the thesis $\dots \dots \dots$                                                             | 97  |

|              |       |                          | The Tanner QC-LDPC code $(a_v, a_c) = (5, 6), R = 0.4, M = 55,$<br>$N = 155 \text{ and } Z = 31 \dots $ | 97  |

|              |       |                          | 1296 and $Z = 54$                                                                                                                                                                                             |     |

|              | A.2   | Min S                    | 1296 and $Z = 54$                                                                                                                                                                                             |     |

|              |       | A.2.1<br>A.2.2           | Flooding Min Sum decoding algorithm                                                                                                                                                                           |     |

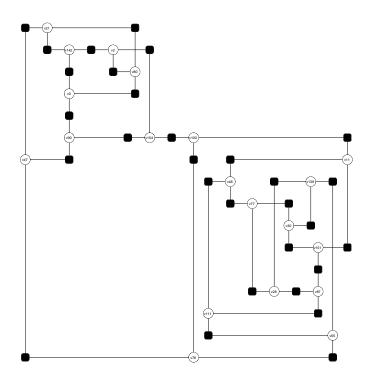

|              | A.3   |                          | ht-20 codewords in Tanner code                                                                                                                                                                                |     |

|              |       | A.3.2                    | Type I                                                                                                                                                                                                        | 102 |

| Bi           | bliog | raphy                    |                                                                                                                                                                                                               | 108 |

# List of Figures

| 1.1  | An illustrating system where LDPC code is applied                                                                                                                                                                                                                                                                                                                                                  | 1  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | An example of the parity check matrix $H$                                                                                                                                                                                                                                                                                                                                                          | 8  |

| 2.2  | The Tanner graph presentation of a parity matrix $H$                                                                                                                                                                                                                                                                                                                                               | 9  |

| 2.3  | The Binary Symmetric Channel model.                                                                                                                                                                                                                                                                                                                                                                | 10 |

| 2.4  | The Additive White Gaussian Noise channel model                                                                                                                                                                                                                                                                                                                                                    | 10 |

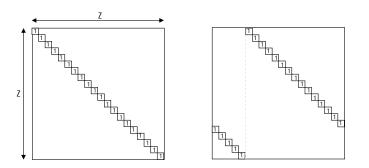

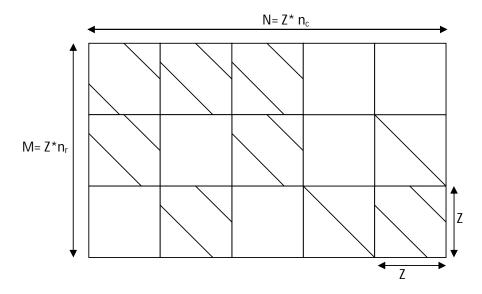

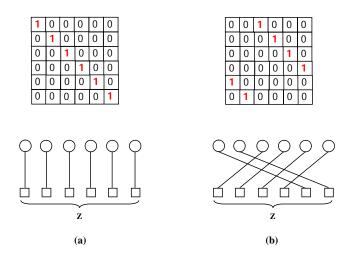

| 2.5  | A main diagonal $Z \times Z$ matrix and one of its circulant shift version<br>used in the construction of QC-LDPC code. The zero entries are not                                                                                                                                                                                                                                                   | 11 |

| 0.0  | shown for the sake of simplicity. $\dots \dots \dots$                                                                                                                                                                                                                                              | 11 |

| 2.6  | An example of the parity check matrix $H$ of a QC-LDPC code                                                                                                                                                                                                                                                                                                                                        | 11 |

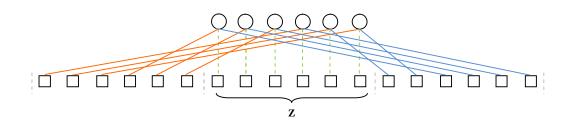

| 2.7  | The cyclic shift of $6x6$ diagonal matrix with shift factor is 0 (a) and 2 (b) and the corresponding connections between the VNs and CNs.                                                                                                                                                                                                                                                          | 12 |

| 2.8  | A full connection of Z VNs in a column of the base matrix with $d_v = 3$ to their neighbor CNs.                                                                                                                                                                                                                                                                                                    | 12 |

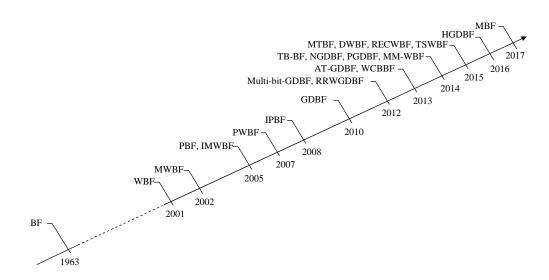

| 2.9  | The BF decoders development since the bit flipping decoding skim in-<br>troduced by Gallager in 1963. These BF decoders can be found at the<br>following references: BF[1], WBF[2], MWBF[3], PBF[4], IMWBF[5],<br>PWBF[6], IPBF[7], GDBF[8], Multi-bit-GDBF[9], RRWGDBF[10],<br>AT-GDBF[11], WCBBF[12], TB-BF[13], NGDBF[14], PGDBF[15],<br>MM-WBF[16], MTBF[17], DWBF[18], RECWBF[19], TSWBF[20], |    |

| 2.10 | HGDBF[21], MBF[22]                                                                                                                                                                                                                                                                                                                                                                                 | 13 |

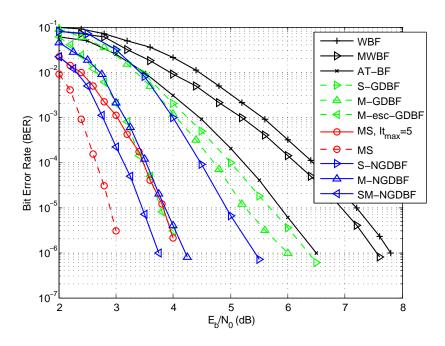

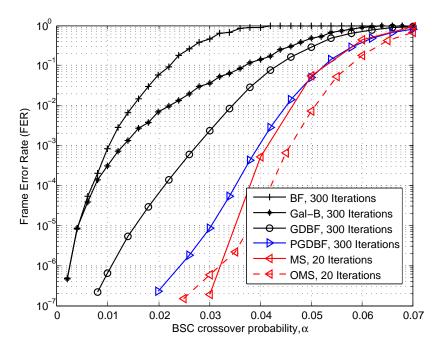

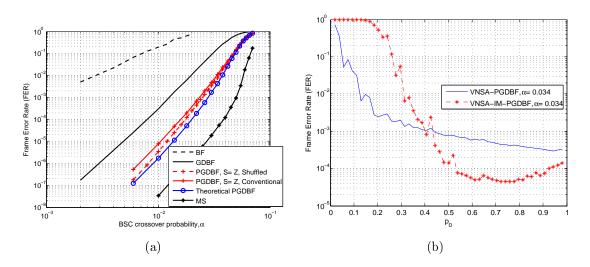

|      | for all other decoders                                                                                                                                                                                                                                                                                                                                                                             | 19 |

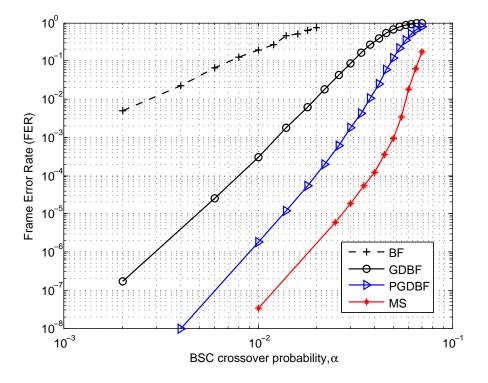

| 2.11 | Performance comparison between LDPC decoders: BF, Gallager-B (Gal-B), GDBF, PGDBF ( $p_0 = 0.9$ ), Quantized MS, Quantized Offset Min-Sum (OMS) with offset factor of 1 of the regular QC-LDPC code ( $d_v = 4, d_c = 8, Z = 54$ ), ( $N = 1296, M = 648$ )                                                                                                                                        | 19 |

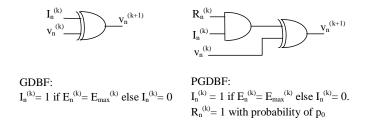

| 2.12 | The difference in the flipping operator between GDBF and PGDBF algorithms. $\dots \dots \dots$                                                                                                                                                                                                     | 25 |

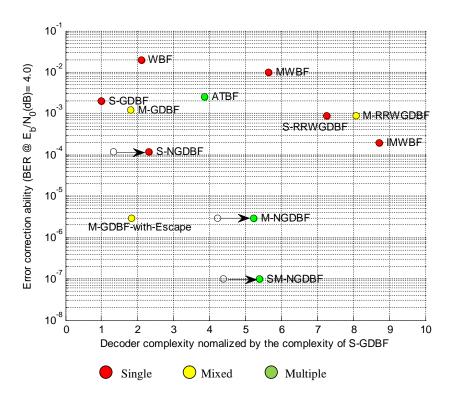

| 2.13 | Performance-complexity comparison of some typical BF-based de-<br>coders on the PEGReg504x1008, regular $d_v = 3$ , $d_c = 6$ LDPC code.                                                                                                                                                                                                                                                           | 27 |

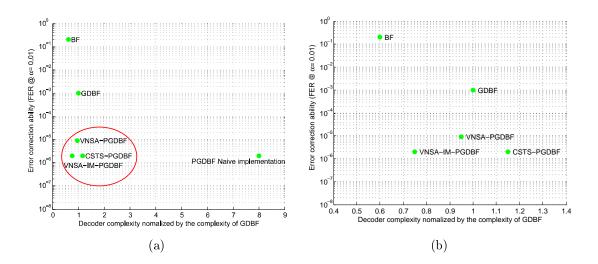

| 2.14         | Performance-complexity comparison of some typical BF-based de-<br>coders on BSC channel for the regular $d_v = 3$ , $d_c = 6$ , $M = 648$ ,<br>N = 1296 QC-LDPC code. The PGDBF implementations in the red<br>cycle are the one proposed in this thesis | 28              |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

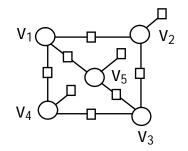

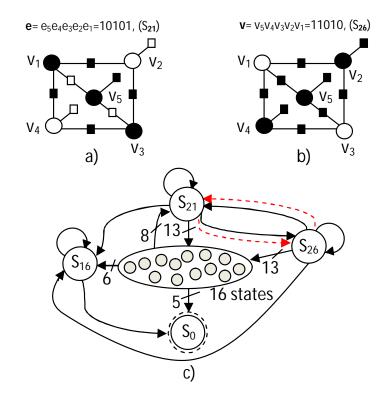

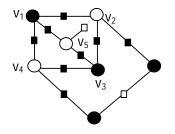

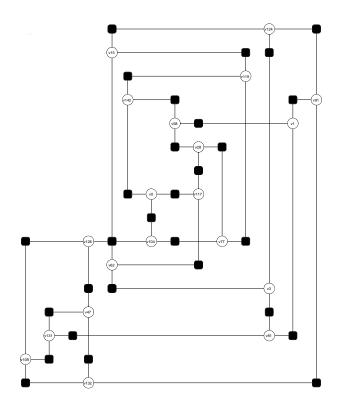

| $3.1 \\ 3.2$ | Trapping Set TS(5,3) in the Tanner Code                                                                                                                                                                                                                 | 31              |

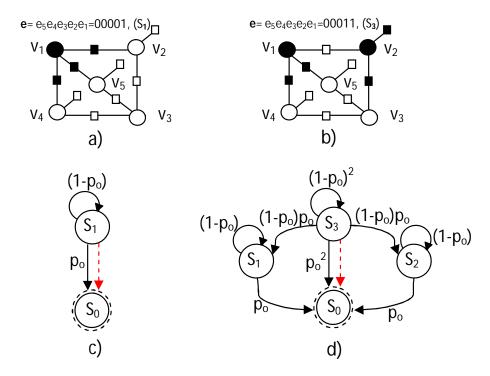

| 3.3          | are the transitions of PGDBF 2 erroneous bits located in Tanner graph of Tanner code. The 2 erroneous bits are either a). sharing a CN or b). separating from                                                                                           | 32              |

| 3.4          | each other                                                                                                                                                                                                                                              | 33              |

| 3.5          | of PGDBF                                                                                                                                                                                                                                                | 34              |

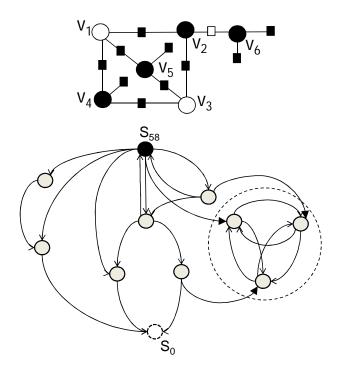

| 26           | resentation of PGDBF decoder.                                                                                                                                                                                                                           | $\frac{35}{37}$ |

| $3.6 \\ 3.7$ | An uncorrectable error pattern of PGDBF since the converging state                                                                                                                                                                                      | 37              |

|              | $S_0$ is not in the induced Markov chain of $e. \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                     | 41              |

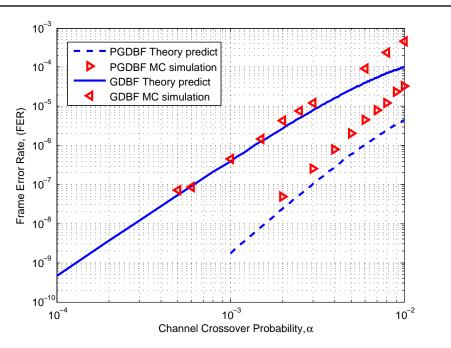

| 3.8<br>3.9   | Performance of PGDBF ( $p_0 = 0.7$ ) and GDBF by simulation and<br>theoretical prediction on the Tanner code                                                                                                                                            | 44              |

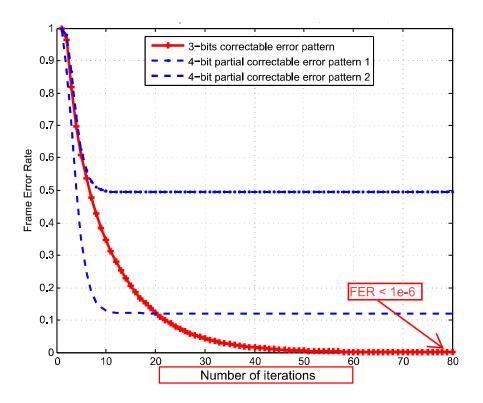

|              | 3.5 and 3.10                                                                                                                                                                                                                                            | 45              |

| 3.10         | An weight-4 partial-uncorrectable error pattern of PGDBF                                                                                                                                                                                                | 45              |

| 4.1          | Performance comparison between LDPC decoders: BF, GDBF, PGDBF $(p_0 = 0.7)$ , Quantized MS of the regular QC-LDPC code $(d_v = 3, d_c =$                                                                                                                |                 |

| 4.9          | 6, Z = 54, $(N = 1296, M = 648)$                                                                                                                                                                                                                        | 48              |

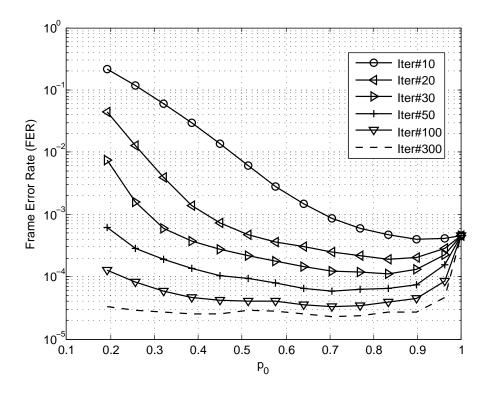

| 4.2          | Frame Error Rate versus $p_0$ in the waterfall region ( $\alpha = 0.01$ ) of<br>Tanner code ( $d_v = 3, d_c = 5, Z = 31$ ), ( $N = 155, M = 93$ )                                                                                                       | 49              |

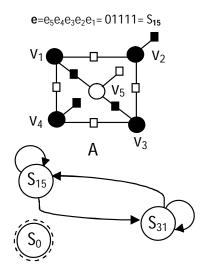

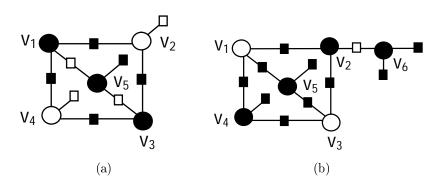

| 4.3          | Error configurations with (a) 3 erroneous bits and (b) 4 erroneous bits located on a $TS(5,3)$ . Black/white circles denote erroneous/correct variable nodes, and black/white squares denote unsatisfied/satisfied                                      |                 |

|              | check nodes                                                                                                                                                                                                                                             | 50              |

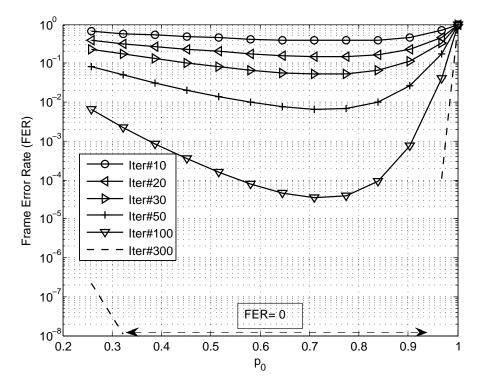

| 4.4          | Frame Error Rate versus $p_0$ in the error floor region with 3 erroneous<br>bits of Tanner code $(d_v = 3, d_c = 5, Z = 31), (N = 155, M = 93)$                                                                                                         | 51              |

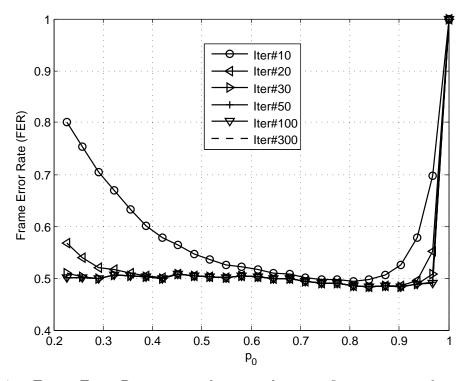

| 4.5          | Frame Error Rate versus the $p_0$ in the error floor region with 4 erroneous bits of Tanner code $(d_v = 3, d_c = 5, Z = 31), (N = 155, M = 93).$                                                                                                       | 51              |

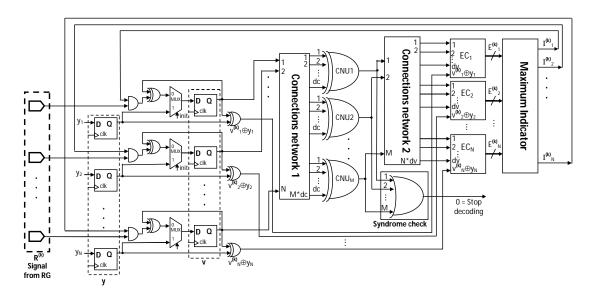

| 4.6          | The global architecture of the PGDBF. The PGDBF follow precisely<br>the data flow of GDBF with difference coming from the random gen-                                                                                                                   |                 |

|              | erator and the AND-gates                                                                                                                                                                                                                                | 52              |

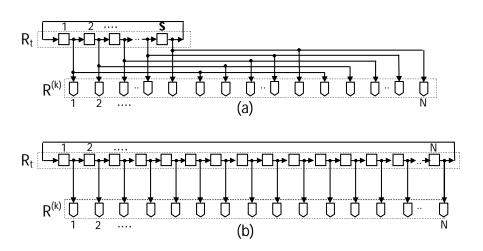

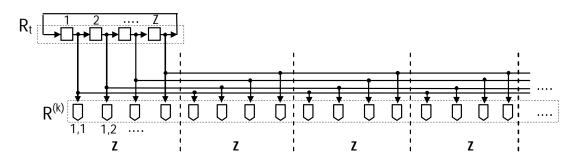

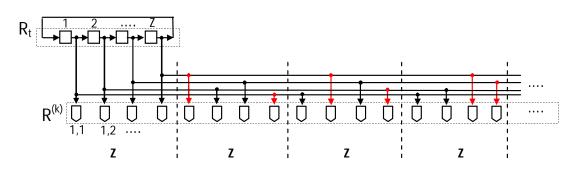

| 4.7          | Generation of the random signals, (a) corresponds to the use of trun-                                                                                        |            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|              | cated sequences, and (b) to the use of full sequences. $\ldots$ $\ldots$ $\ldots$                                                                            | 54         |

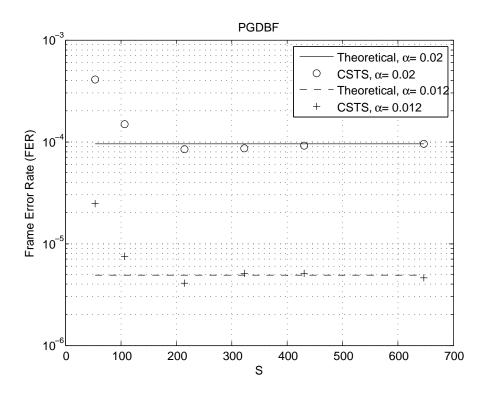

| 4.8          | Decoding performance of CSTS-PGDBF as a function of the size $S$ of $R_t^{(0)}$                                                                              | 55         |

| 4.9          | A LFSR unit to generate 1 random bit. $\ldots$                                                                                                               | 56         |

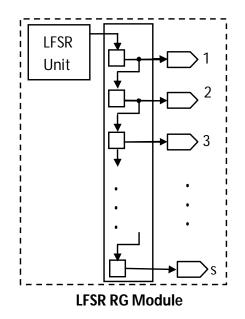

| 4.10         | The LFSR RG module                                                                                                                                           | 56         |

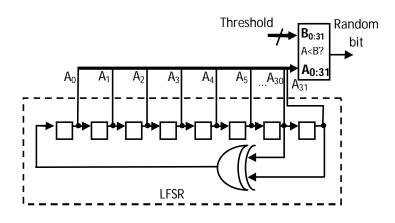

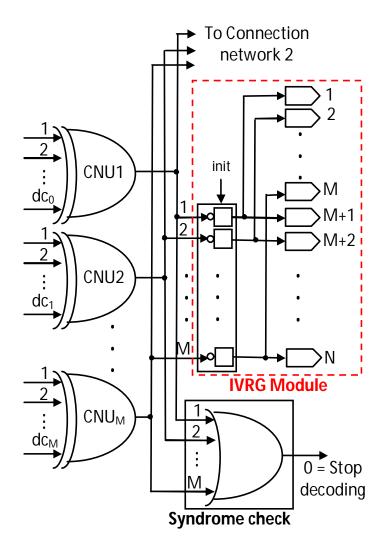

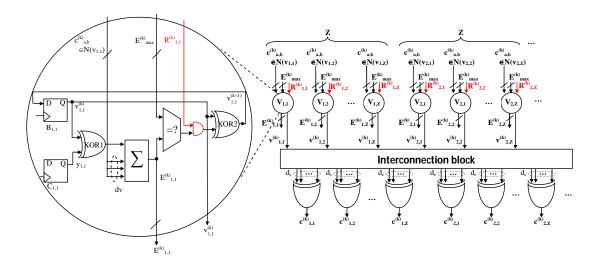

|              | A block diagram of the Intrinsic-Valued Random Generator module                                                                                              | 50         |

| 4.11         | for $S = M = N/2$ . The CNs values are copied into the $R_t^{(0)}$ at the                                                                                    |            |

|              | first iteration, then cyclically shifted at each iteration                                                                                                   | 58         |

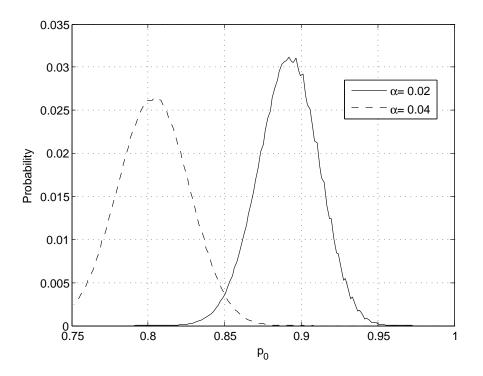

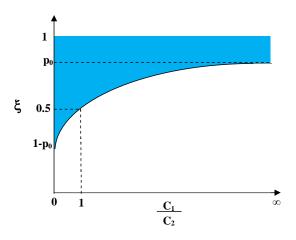

| 4.12         | The distribution of $p_0$ for the IVRG-PGDBF and a $(d_v = 3, d_c =$                                                                                         |            |

|              | 6, $N = 1296$ ) QC-LDPC code, for $\alpha = 0.02$ and $\alpha = 0.04$ .                                                                                      | 59         |

| 4.13         | Detailed circuits of implemented Energy Computation and Maximum                                                                                              |            |

|              | Indicator blocks for $d_v = 3$ LDPC codes, (a) Energy Computation                                                                                            | <b>a</b> 0 |

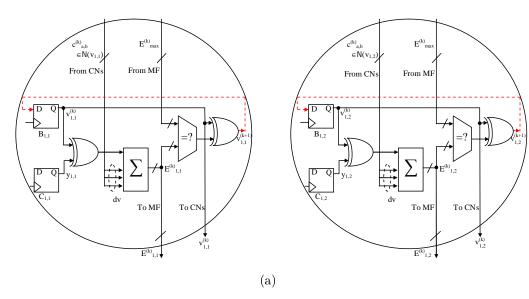

|              | block, (b) Maximum Indicator block.                                                                                                                          | 60         |

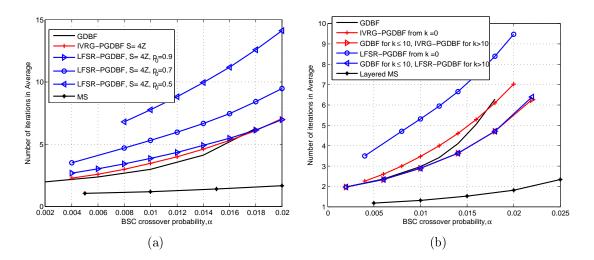

| 4.14         | Average number of iterations for GDBF, PGDBF and MS decoders                                                                                                 |            |

|              | on the dv3R050N1296 regular LDPC code. In Figure (a), randomness                                                                                             |            |

|              | is applied at the beginning of decoding process in PGDBF decoders.                                                                                           |            |

|              | In Figure (b). PGDBF decoders are with $S = 4Z$ and $p_0 = 0.7$ in                                                                                           | <u></u>    |

|              | LFSR-PGDBF                                                                                                                                                   | 63         |

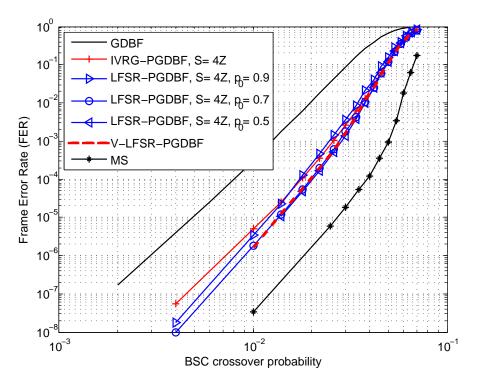

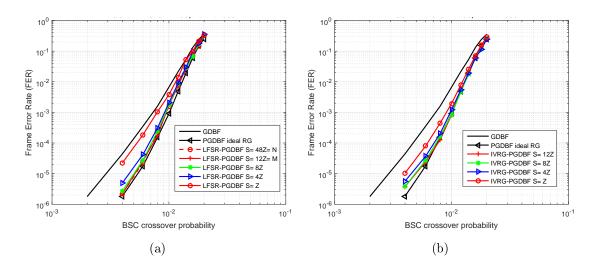

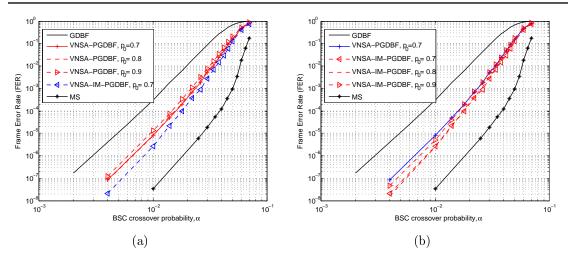

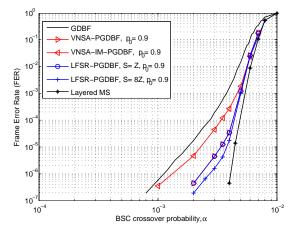

| 4.15         | Decoding performance of GDBF, LFSR-PGDBF, IVRG-PGDBF and                                                                                                     |            |

| 1 1 0        | MS decoders on the LDPC code $d_v = 3$ , $d_c = 6$ , $N = 1296$ (dv3R050N129)                                                                                |            |

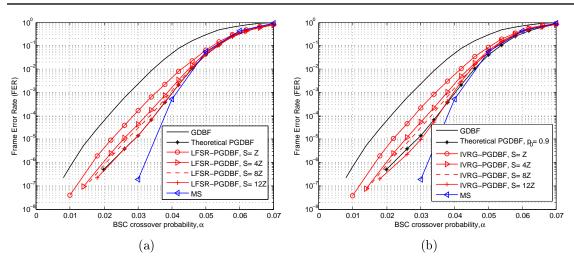

| 4.16         | Effect of the RS length S on the decoding performance for the $dv4R050N1$                                                                                    |            |

| 4 1 17       | code: (a). LFSR-PGDBF decoders $(p_0 = 0.9)$ , (b). IVRG-PGDBF                                                                                               |            |

| 4.17         | Effect of the RS length S on the decoding performance for the dv3R050N1                                                                                      |            |

| 4 1 0        | code: (a). LFSR-PGDBF decoders $(p_0 = 0.7)$ , (b). IVRG-PGDBF.                                                                                              |            |

| 4.18         | Effect of the RS length S on the decoding performance for the dv4R075N1 code: (a). LFSR-PGDBF decoders $(p_0 = 0.9)$ , (b). IVRG-PGDBF.                      |            |

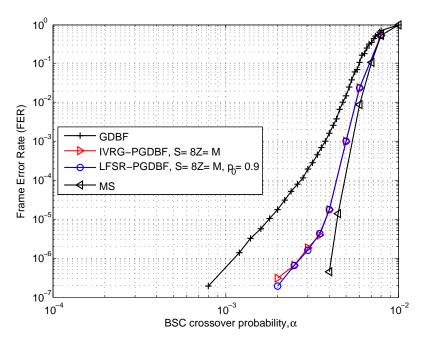

| 1 10         | Decoding performance of GDBF, PGDBF ( $It_{max} = 300$ ) and MS                                                                                              | 01         |

| ч.1 <i>5</i> | $(It_{max} = 20)$ decoders on a QC-LDPC code with $dv = 4$ , Rate = 0.88,                                                                                    |            |

|              | $Z = 140, M = 1120 \text{ and } N = 9520. \dots \dots$ | 67         |

|              | $Z = 140, M = 1120 \text{ and } N = 5020. \dots \dots$ | 01         |

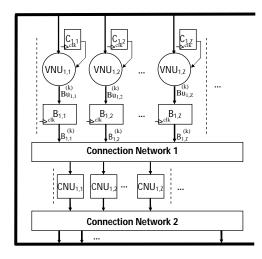

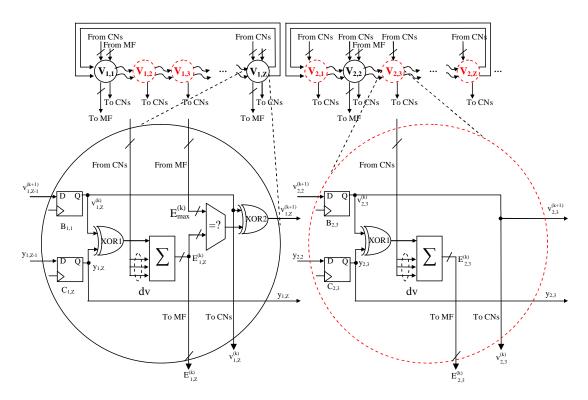

| 5.1          | The conventional architecture of QC-LDPC                                                                                                                     | 71         |

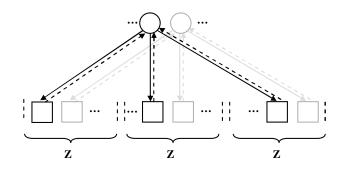

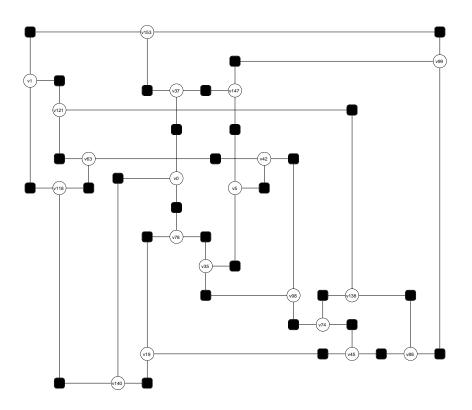

| 5.2          | The Tanner graph of a QC-LDPC code                                                                                                                           | 71         |

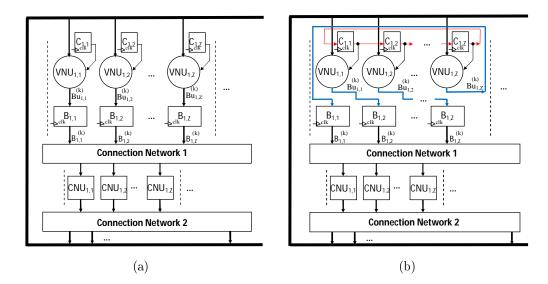

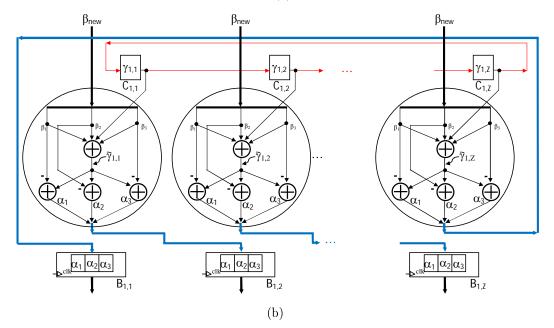

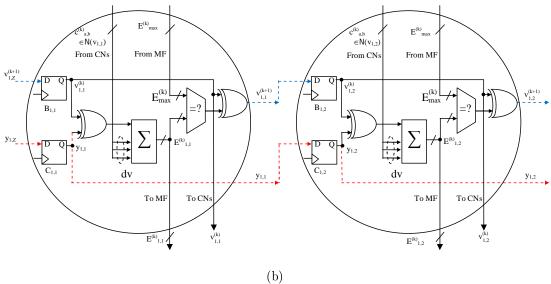

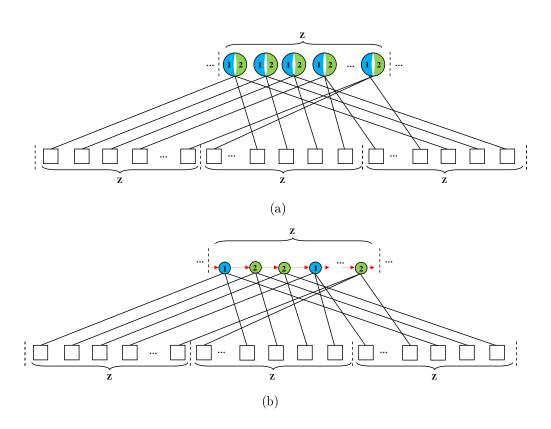

| 5.3          | The generic QC-LDPC decoder architectures: Figure 5.3(a) the con-                                                                                            |            |

|              | ventional architecture. Figure 5.3(b) the proposed Variable-Node                                                                                             |            |

|              | Shift Architecture (VNSA).                                                                                                                                   | 73         |

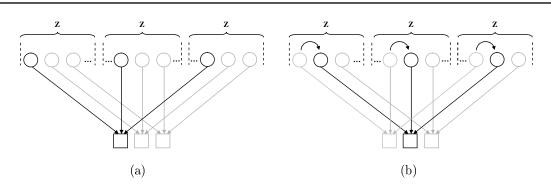

| 5.4          | With non-memory cyclically shift (a) and with memory cyclically shift                                                                                        |            |

|              | (b), the messages are both well conveyed to a common CNU thank                                                                                               |            |

|              | to the constructive implemented connections in QC-LDPC decoders                                                                                              | 74         |

| 5.5          | When a cyclic shift is applied on the memory of VNU, the messages                                                                                            |            |

|              | from CNUs are also sent to the corresponding cyclic shift VNU                                                                                                | 74         |

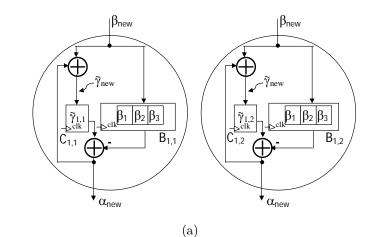

| 5.6          | VNSA application on Flooding MS. Figure 5.6(a): 2 consecutive                                                                                                |            |

|              | VNUs in the conventional flooding MS implementation. Figure 5.6(b):                                                                                          |            |

|              | Z consecutive VNUs in a base-column of base matrix in VNSA-based                                                                                             |            |

|              | implementation where the memory elements are cyclically shifted                                                                                              | 75         |

| 5.7  | in the conventional layered MS implementation. Figure 5.7(b): $Z$ consecutive VNUs in a base-column of base matrix in VNSA-based                                                                                                                                                                                                                           |            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

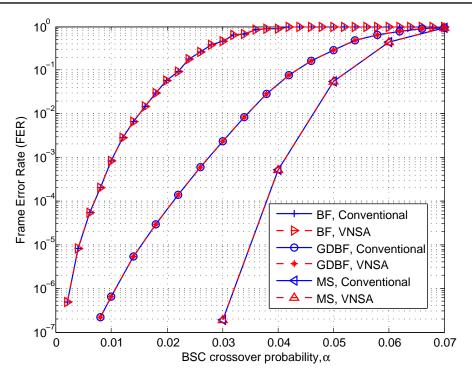

| 5.8  | implementation where the memory elements are cyclically shifted Performance comparison between BF, GDBF, Quantized flooding MS LDPC decoders both conventional and VNSA-based implementations for the regular QC-LDPC code ( $d_v = 4, d_c = 8, Z = 54$ ), ( $N =$                                                                                         | 77         |

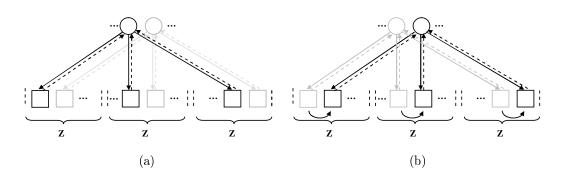

| 5.9  | 1296, $M = 648$ )                                                                                                                                                                                                                                                                                                                                          | 78         |

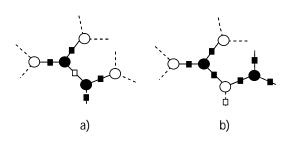

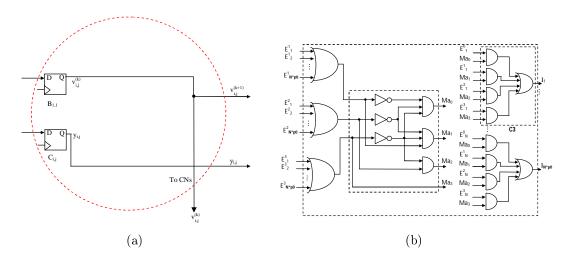

| 5.10 | memory elements are cyclically shifted                                                                                                                                                                                                                                                                                                                     | 79         |

|      | VNU (Figure 5.10(b)). $\ldots$                                                                                                                                                                                                                                                                                                                             | 81         |

|      | The hardware efficiency of VNSA over the conventional implementation.                                                                                                                                                                                                                                                                                      | 81         |

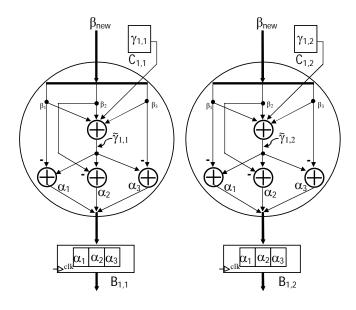

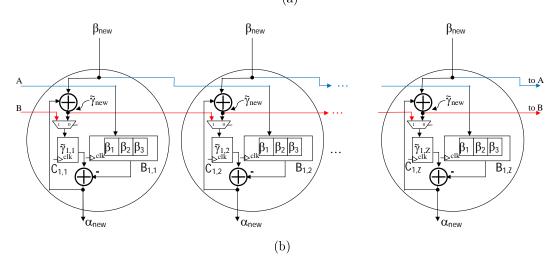

| 5.12 | The implementation of VNSA-PGDBF decoder                                                                                                                                                                                                                                                                                                                   | 83         |

| 5.13 | The conventional implementation of PGDBF                                                                                                                                                                                                                                                                                                                   | 83         |

| 5.14 | The optimized probabilistic signals generator proposed in Chapter 4.                                                                                                                                                                                                                                                                                       | 84         |

| 5.15 | The probabilistic signals generator proposed in Chapter 4 with the                                                                                                                                                                                                                                                                                         |            |

|      | hardwire shuffled                                                                                                                                                                                                                                                                                                                                          | 84         |

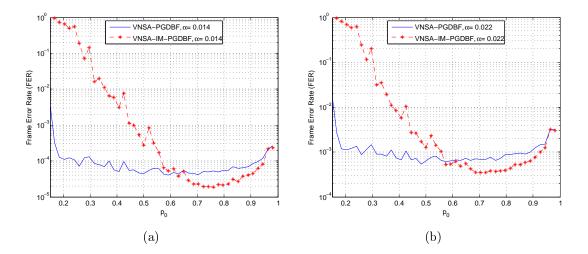

| 5.16 | Figure 5.16(a) Decoding performance comparison of PGDBF decoder<br>implemented in Chapter 4 with the hardwire connections in random<br>generator shuffled. Figure 5.16(b) The statistical on decoding perfor-<br>mance of VNSA-PGDBF and VNSA-IM-PGDBF as a function of $p_0$<br>on the $((d_v, d_c) = (4, 8), Z = 54, N = 1296$ and $M = 648)$ LDPC code. | 85         |

| 5.17 | The statistical on decoding performance of VNSA-PGDBF and VNSA-<br>IM-PGDBF as a function of $p_0$ on the $((d_v, d_c) = (3, 6), Z = 54,$                                                                                                                                                                                                                  | ٥ <b>٢</b> |

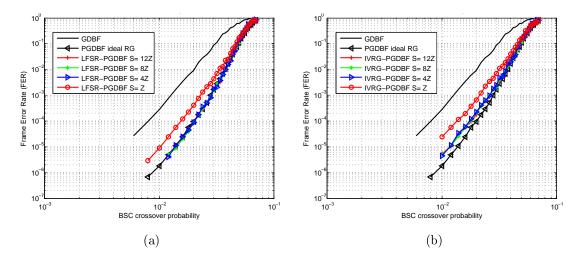

| 5.18 | N = 1296 and $M = 648$ ) LDPC code                                                                                                                                                                                                                                                                                                                         | 85         |

|      | IM-PGDBF.                                                                                                                                                                                                                                                                                                                                                  | 87         |

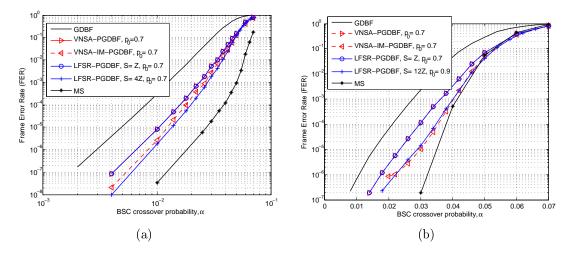

| 5.19 | The decoding performance of the VNSA-PGDBF and VNSA-IM-<br>PGDBF on different LDPC code. Figure 5.19(a) for the $((d_v, d_c) = (3, 6), Z = 54, N = 1296$ and $M = 648$ ) LDPC code. Figure 5.19(b)                                                                                                                                                         |            |

| 5.20 | for the $((d_v, d_c) = (4, 8), Z = 54, N = 1296 \text{ and } M = 648)$ LDPC code.<br>The decoding performance of the VNSA-PGDBF and VNSA-IM-<br>PGDBF with the variation of $p_0$ on the $((d_v, d_c) = (3, 6), Z = 54,$                                                                                                                                   | 89         |

|      | N = 1296 and $M = 648$ ) LDPC code                                                                                                                                                                                                                                                                                                                         | 90         |

| 5.21 | The decoding performance comparison on the $((d_v, d_c) = (4, 34), Z = 140, N = 9520$ and $M = 1120)$ LDPC code.                                                                                                                                                                                                                                           | 90         |

# List of Tables

| 2.1          | The complexity of some typical hard decision decoders                                                                                                                                                                                                                     | 26 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $3.1 \\ 3.2$ | Number of codeword weight-20 and $TS(5,3)$ in Tanner code [23]<br>Error correction ability of LDPC decoders on the Type I codeword                                                                                                                                        | 42 |

| 3.3          | of Tanner code. The numbers in the brackets are (number of uncor-<br>rectable - number of partial-uncorrectable) error patterns<br>Error correction ability of LDPC decoders on the Type II codeword<br>of Tanner code. The numbers in the brackets are (number of uncor- | 43 |

| 3.4          | rectable - number of partial-uncorrectable) error patterns Error correction ability of LDPC decoders on the Type III codeword                                                                                                                                             | 43 |

| 0.4          | of Tanner code. The numbers in the brackets are (number of uncor-<br>rectable - number of partial-uncorrectable) error patterns.                                                                                                                                          | 43 |

| 4.1          | Hardware resource used to implement the PGDBF decoders as a func-<br>tion of S. The percentages in brackets indicate the additional hard-                                                                                                                                 | 01 |

| 4.2          | ware compared to the GDBF                                                                                                                                                                                                                                                 | 61 |

| 4.3          | additional hardware compared to GDBF                                                                                                                                                                                                                                      | 62 |

|              | decoders, and MS decoders [24, 25]. QC-LDPC $(d_v, d_c) = (3, 6)$ ,<br>$R = 1/2, N = 1296, Z = 54. \dots$                                                                                                                                                                 | 63 |

| 4.4          | Frequency and throughput comparison between GDBF, PGDBF de-<br>coders and MS decoder from [26]. QC-LDPC $(d_v, d_c) = (4, 34)$ ,<br>$R = 0.88, N = 9520, Z = 140. \dots \dots$        | 64 |

| 5.1          | Comparison on hardware resource used to implement the GDBF and                                                                                                                                                                                                            | 04 |

|              | PGDBF decoders by using the conventional and the VNSA archi-<br>tectures. The percentages in brackets indicate the additional/saving                                                                                                                                      |    |

| 5.2          | hardware compared to the GDBF<br>Frequency and throughput comparison between GDBF decoder, PGDBF                                                                                                                                                                          | 88 |

|              | decoders, and MS decoders [24, 25]                                                                                                                                                                                                                                        | 88 |

# Glossary

**APP:** A Posteriori Probability AWGN: Additive White Gaussian Noise **BER:** Bit Error Rate BI-AWGN: Binary-Input Additive White Gaussian Noise **BP:** Belief-Propagation **BSC:** Binary Symmetric Channel **CN:** Check Node **CNU:** Check Node Processing Unit **DE:** Density Evolution EM: Edge-Memory FER: Frame Error Rate LDPC: Low Density Parity Check LLR: Log-Likelihood Ratio LSB: Least Significant Bit ML: Maximum Likelihood **MP:** Message Passing MS: Min-Sum **NMS:** Normalized Min-Sum **OMS:** Offset Min-Sum QC: Quasi-Cyclic SNR: Signal-to-Noise Ratio **VN:** Variable Node **VNU:** Variable Node Processing Unit

# Chapter 1

# Introduction

#### **1.1** Context and motivations

Figure 1.1 illustrates an application system where the LDPC coding is employed. A vector of K information bits is sent through a noisy channel in which errors may occur. The noisy channel could be any communication channel such as wire, wireless communication system... where errors may appear during the transmission or the noisy storage medium such as flash memory... where errors happen during the storing, writing to or reading out of the memory. With targeting to detect and correct the errors, LDPC is deployed by adding the LDPC encoder and decoder to the system as in Figure 1.1. LDPC encoder forms a N-bits codeword by adding M parity bits to the K information bits sequence before sending through the channel. At the channel output, N received bits are processed by an LDPC decoder targeting to accurately recover K information bits.

Figure 1.1: An illustrating system where LDPC code is applied.

LDPC codes have attracted high attention in the past several years due to their excellent performance under iterative decoding process. These studies focus either on improving the error correction performance of the LDPC codes or on reducing the implementation complexity of the decoders for practical applications. Soft decision iterative decoding, such as Belief Propagation (BP) or Min-Sum (MS) algorithms offers the best error correction performance, close to the theoretical coding bounds, but comes along with an intensive computation cost [27]. On the contrary, the class of hard-decision iterative decoders is often seen as a very low-complexity solution, very fast in computation, with an associated performance loss. This work focuses on the class of A Posteriori Probability (APP) based hard decision decoders, belonging to the family of Bit-Flipping (BF) decoders where, contrary to message-passing decoders, both the extrinsic and the intrinsic information are exchanged between the nodes of the Tanner graph [3][28].

From the recent literature, it can be seen that the hard decision decoding algorithms are an attractive research topic due to their low complexity and fast computation. In the next generation of communication systems, throughput and power consumption are the key challenges. The high throughput system is required to support the continuously increasing demand of traffic volume, while power consumption, especially in the mobile devices, becomes a significant concern. LDPC error correction modules are a part of the system and so, need to be optimized to fulfill these high throughput and energy saving targets. From this point, hard decision decoders, *i.e.* Bit Flipping decoders, with their advantages of simple and fast computation, become promising candidates provided that their error correction ability is improved. Indeed, hard decision decoders require very simple computations which may lead to an extremely high throughput. Also, the simple computations with very low decoder complexity may result less energy consumption in hard decision decoders than the soft decision decoders. The problem is that the decoding performance of hard decision decoders is usually weak and need to be improved in order to cope with error correction demand.

In the direction of improving BF decoding performance by modifying the algorithm computations, the recent study of iterative LDPC decoders implemented on faulty-hardware has led to the counter-intuitive conclusion that the noisy decoders could perform better than their noiseless versions. In other words, the random perturbation on algorithm computations, in some case, helps improving the error correction capability. This random perturbation (probabilistic) effect on decoding performance appears to be very attractive and worth to study. The reason of this is twofold. First, since random perturbation improves the decoding performance, it seems simpler to inject the randomness to the computation than modifying the decoding algorithm with the same decoding gain. The probabilistic algorithms studied in this thesis are, actually, better than all similar deterministic decoders in term of performance. Second, with the understanding on the improving principle of perturbation on decoding performance, it facilitates the design of fault-tolerant decoders.

This thesis focuses on a newly proposed probabilistic BF-based decoder which is a random perturbation version of Gradient Descent Bit Flipping (GDBF) [8], called as Probabilistic Gradient Descent Bit Flipping (PGDBF) proposed by Rasheed *et al.* in [15], applied on BSC channel. PGDBF provides the best error correction compared to all known BF-based decoders and approaches the soft information decoding performance such as Min-Sum. Although the very promising performance capability, several issues of PGDBF were left unexplored so far. First, the outstanding performance of PGDBF is observed by simulation. There is lack of an analytic method to analyse and explore its asymptotic performance gain. Second, the advantage of PGDBF comes from the presence of a probabilistic signal generator on top of the deterministic decoder. One of our preliminary work in [29] showed that the additional cost for this probabilistic signal generator is too large and becomes the bottleneck of PGDBF. The efficient implementation of PGDBF is, therefore, needed to minimize the complexity overhead while maintaining its performance gain.

#### **1.2** Main contributions and thesis outline

The main contributions of this thesis are:

- Propose an analytic method to analyze the PGDBF decoding algorithm. This analyzing method can be extended to other hard decision decoders.

- Propose an efficient hardware realization of PGDBF decoder for generic LDPC codes that minimizes the complexity overhead.

- Propose a novel, hardware efficient architecture for LDPC decoding suitable for QC-LDPC algorithms demonstrated by the PGDBF proof-of-concept implementation.

We briefly summarize in the following the content of each chapter of the thesis correspondingly to the above contributions.

#### Chapter 2: Hard decision decoders

Chapter 2 starts by providing a brief introduction of LDPC codes and LDPC decoding concept. The channel models, *i.e.* Binary Symmetric Channel and Additive White Gaussian Noise channel, in which the distortion affects on the transmitted signals, are also presented. The Quasi-Cyclic construction of LDPC codes is introduced by highlighting its structure which is used in the proposed architecture called Variable-Node Shift Architecture in Chapter 5. The second part of this chapter provides a literature review on the development of the hard decision decoders. We first discuss the BF-based decoders. BF decoder family is a type of A Posteriori Probability propagation decoders and several solutions have been proposed in the litterature to modify and improve the original BF decoder [2][8][14][15]. From the recent literature, it is clear that BF decoders made a big evolution from a "toy" algorithm with a very weak in error correction capability to very powerful decoder that can be competitive with the soft decision decoders. *Extrinsic* message passing decoders such as Gallager-A, Gallager-B... are also presented in this chapter together with the new type of noise-added BF decoders - Noisy Gradient Descent Bit Flipping decoder applied on AWGN and Probabilistic Gradient Descent Bit Flipping decoder applied on BSC channel. The noise-added BF decoders share the same principle that adds a random perturbation to the selection of the flipped bits, helps the decoders to escape from the trapping points which prevent the convergence of the decoders. Beside the good decoding performance of these noise-added BF decoders, their hardware complexity becomes the emerging issue which comes from the exhaustive implementation of the randomness generation. Smart implementations are required such that the performance gain is preserved while minimizing the additional hardware overhead.

#### Chapter 3: Theoretical analysis of Probabilistic Gradient Descent Bit Flipping

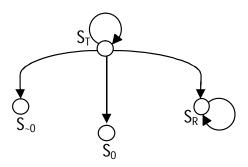

Chapter 3 introduces an analysis method for hard decision decoders denoted as Finite State Tracking (FST). Although FST is shown to be able to apply on different type of hard decision decoders, we limit the FST presentation in this chapter only on PGDBF decoder. FST represents the PGDBF decoding process from an iteration to another as a state transition in a Markov Chain (MC). A state of PGDBF decoding is represented as a state in this MC and by analyzing the MC, the closed-form expression of Frame Error Rate as a function of number of iteration can be derived. The uncorrectable and partial-uncorrectable error pattern definition is newly introduced in this chapter in order to indicate correspondingly the error pattern that can not be corrected and the one which can be corrected with some probability by PGDBF. The uncorrectable and partial-uncorrectable error pattern can be also determined by analyzing the MC. We illustrate the utilization of FST by analyzing the performance of PGDBF decoder and compare it with other BF decoders. It is firstly shown that the number of uncorrectable error patterns of PGDBF on the tested LDPC code is significantly reduced compared to GDBF and conventional BF decoders. The predictive performance curves on the error floor are then derived, based one the estimated number of uncorrectable and partially correctable error patterns and are finally confirmed by the simulation results. The improvement of PGDBF is clearly explained by showing that many transitions leading to the zeroerror state in PGDBF do not appear in deterministic GDBF. Furthermore, FST provably shows that for some given error patterns, the PGDBF can converge to the zero-error state only if some specific transitions occur. Getting into these transitions depends on the realization of the random signal. This explains the decoding gain phenomenon of re-initialization (or restarting, rewinding) of the PGDBF decoding from the beginning with new random realizations.

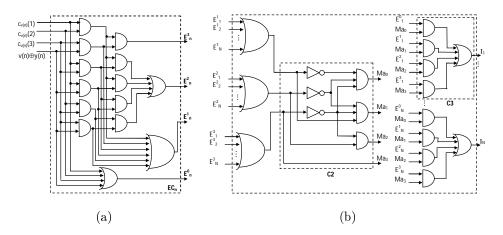

#### Chapter 4: Efficient hardware implementation of Probabilistic Gradient Descent Bit Flipping

Chapter 4 presents an efficient hardware (HW) implementation of the PGDBF decoder which minimizes the resource overhead needed to implement the random perturbations and the maximum finder of the PGDBF. In Section 4.2, the conducted statistical analysis in PGDBF is presented in order to show the precise characterization of its key parameters, especially the values of the random generator parameters that lead to the maximum coding gains. This analysis is performed through Monte Carlo simulations in both the waterfall and the error floor regions. Section 4.3 shows the optimized HW architecture for the PGDBF decoder. The proposed architecture is based on the use of a short random signals that are duplicated to fully apply the PGDBF decoding rules on the whole codeword. Two different initialization solutions are proposed with equivalent HW overheads, but with different behaviors on different LDPC codes. An optimization of the maximum finder unit of the PGDBF algorithm is also presented in order to reduce the critical path and improve the decoding throughput. Finally, Section 4.4 shows the synthesis results on ASIC 65nm technology, and Monte-Carlo simulations with a bit-accurate C implementation of the proposed PGDBF architecture on LDPC codes with various rates and lengths.

#### Chapter 5: A Quasi-Cyclic friendly architecture for LDPC decoders : the Variable-Node Shift Architecture

Chapter 5 introduces a new decoding architecture for the QC-LDPC codes, called as Variable-Node Shift Architecture (VNSA). The VNSA takes advantage of the structure of the QC-LDPC codes to shift the memory of the decoders while preserving the exact decoding operations. It is shown in this chapter that the VNSA-based decoders significantly reduce the complexity and achieve the better decoding performance compared to the conventional decoder implementations. These advantages come from the fact that by shifting the memory of the decoders, the variable node computations can be processed differently when different types of variable nodes are implemented. This dynamical processing helps the decoder break some trapping states and converge while the decoder with conventional implementation does not. The hardware savings also come from the fact that some variable node implementations in VNSA are simpler than those of the conventional implementation making the global complexity reduced. The chapter is presented as follows. The VNSA principle is firstly presented in the generic form in Section 5.2 since it can be applied to different decoding algorithms. The illustrations of VNSA applications on different types of LDPC decoders are presented in the next sections (Section 5.3 and 5.4) for the edge-type memory and node-type memory decoders in which the VNSA is shown to be well adapted for all of these decoders. The VNSA becomes trully advantageous when different functions are required for the VNU or the CNU implementations. These advantages are either expressed in terms of performance gain, or in HW complexity savings which is discussed in Section 5.5. We illustrate the interest of this new architecture with the implementation of the Probabilistic Gradient Descent Bit Flipping basing on the VNSA (called VNSA-PGDBF) in Section 5.6. It is shown that the outstanding decoding performance of PGDBF is preserved in VNSA-PGDBF while the decoder complexity is significantly reduced and even smaller than the deterministic GDBF. A further simplified version of VNSA-PGDBF is also introduced, called as the imprecise VNSA-PGDBF (VNSA-IM-PGDBF). This VNSA-IM-PGDBF not only reduces the complexity compared to the VNSA-PGDBF but also improves the decoding performance.

CHAPTER 1. INTRODUCTION

## Chapter 2

## Hard decision decoders

This chapter starts by providing a brief introduction of LDPC codes and LDPC decoding concept (Section 2.1). The channel models, *i.e.* Binary Symmetric Channel and Additive White Gaussian Noise channel, in which the distortion affects on the transmitted signals, are also presented. The Quasi-Cyclic construction of LDPC codes is introduced by highlighting its structure which is used in the proposed architecture called Variable-Node Shift Architecture in Chapter 5. The second part of this chapter provides a literature review on the development of the hard decision decoders. We first discuss the BF-based decoders in Section 2.2. BF decoder family is a type of A Posteriori Probability propagation decoders and several solutions have been proposed in the litterature to modify and improve the original BF decoder [2][8][14][15]. From the recent literature, it is clear that BF decoders made a big evolution from a "toy" algorithm with a very weak in error correction capability to very powerful decoder that can be competitive with the soft decision decoders. *Extrinsic* message passing decoders such as Gallager-A, Gallager-B... are also presented in this chapter (Section 2.3) together with the new type of noise-added BF decoders -Noisy Gradient Descent Bit Flipping decoder applied on AWGN and Probabilistic Gradient Descent Bit Flipping decoder applied on BSC channel (Section 2.4). The noise-added BF decoders share the same principle that adds a random perturbation to the selection of the bits to be flipped, helps the decoders to escape from the trapping points which prevent the convergence of the decoders. Beside the good decoding performance of these noise-added BF decoders, their hardware complexity becomes the emerging issue which comes from the exhaustive implementation of the randomness generation. Efficient implementations are required such that the performance gain is preserved while minimizing the additional hardware overhead. The hardware complexity of BF decoders is reviewed in Section 2.5. Section 2.6 concludes this chapter.

#### 2.1 Low-Density Parity-Check codes and channel models

#### 2.1.1 Low-Density Parity-Check codes

A binary LDPC code is defined by a sparse parity-check matrix H with size  $(M \times N)$ , where N > M. Each row of H represents a parity check function, computed by a Check Node (CN), on the bits so-called Bit Nodes or Variable Nodes (VN) represented by the columns of H. The CN  $c_m$   $(1 \le m \le M)$  checks the VN  $v_n$   $(1 \le n \le N)$  if the entry  $h_{m,n} = 1$ . An example of the parity-check matrix H is illustrated in Figure 2.1.

|     | ◄ |   |   |   |   |   |   |   |   | Ν |   |   |   |   |   |   |   |   | <b>→</b> |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----------|

| ₹   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0        |

|     | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0        |

|     | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0        |

| м   | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1        |

|     | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0        |

|     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0        |

|     | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0        |

|     | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0        |

| . ↓ | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0        |

Figure 2.1: An example of the parity check matrix H.

A codeword is a vector  $\mathbf{x} = (x_1, x_2, \dots, x_N) \in \{0, 1\}^N$  which satisfies  $H\mathbf{x}^T = \mathbf{0}$ . This codeword  $\mathbf{x}$  is produced by the LDPC encoder (see Figure 1.1) and is sent through a transmission channel. The output of the channel is denoted by  $\mathbf{y} = \{y_1, y_2, \dots, y_N\}$ . Depending on the channel model, the value of  $y_n$  could be only a binary value (0 or 1) in Binary Symmetric Channel or a higher level of precision as in the Additive White Gaussian Noise (AWGN) channel. An introduction of the channel models is presented in the next section.

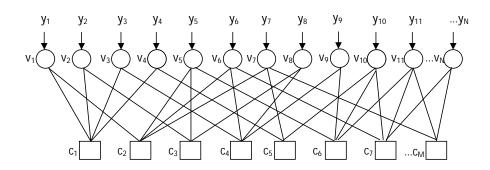

Another alternative representation of an LDPC code is a bipartite graph called Tanner graph composed of two types of nodes, the VNs  $v_n$ , n = 1, ..., N and the CNs  $c_m$ , m = 1, ..., M as in Figure 2.2 where the cycles represent the VNs and squares represent the CNs. In the Tanner graph, a VN  $v_n$  is connected by an edge to a CN  $c_m$  if the entry  $h_{m,n} = 1$ .

The set of CNs connected to the VN  $v_n$  is called the neighbor set of this VN and denoted as  $\mathcal{N}(n)$ . Similarly, the set of VNs connected to the CN  $c_m$  is the neighbor set of this CN and referred as  $\mathcal{N}(m)$ . The connection degree is defined by the size of the neighbor set, i.e. the VN degree  $d_{v_n} = |\mathcal{N}(n)|$  and the CN degree  $d_{c_m} = |\mathcal{N}(m)|$ . An LDPC code is called as regular code when its connection degrees are equal for all nodes, i.e.  $d_{c_m} = d_c, \forall m$  and  $d_{v_n} = d_v, \forall n$ .

Figure 2.2: The Tanner graph presentation of a parity matrix H.

#### 2.1.2 LDPC decoding concepts

LDPC decoding process is defined by the iterative updating and passing the computed messages between the VNs and CNs on the edges of the Tanner graph through decoding iteration. A decoding iteration is typically composed by the following steps:

- 1. VNs computation: The VNs compute the messages to send to the CNs basing on the channel received values and the messages from the CNs.

- 2. VNs to CNs: Computed messages are sent to the CNs.

- 3. **CNs computation**: The CNs compute the new messages basing on their incoming messages.

- 4. CNs to VNs: The new CNs messages are sent to the VNs.

During the decoding process, the codeword validity is always verified basing on the intermediate values by the syndrome check computation. The decoding process is terminated when either a valid codeword is found, in which case the decoding success is declared or the number of iterations reach to the maximum allowed value,  $It_{max}$ , in which case the decoding failure is declared.

The nature of passed messages defines different types of LDPC decoding algorithms. In soft decision message passing algorithms such as Belief Propagation (BP) or Min-Sum (MS) [27], the probability of a given bit to be 0 or 1 is passed back and forth along the edges of the Tanner graph. These soft messages require a very complex computations in the VNs and CNs and the large interleaver (or interconnection) network to exchange them. However, they provide the best decoding performance approaching the decoding bounds. Another type of LDPC decoding algorithms is hard decision decoders in which only binary hard decision values are exchanged between VNs and CNs. The computations in VNs and CNs of hard decision decoders decoders usually lower in complexity, faster in computation compared to soft decision decoders. However, a non-negligible performance loss is observed in hard decision decoders resulting in not being the first option for practical applications.

Figure 2.3: The Binary Symmetric Channel model.

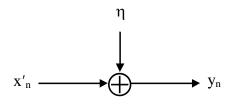

Figure 2.4: The Additive White Gaussian Noise channel model.

#### 2.1.3 The channel models of LDPC decoding

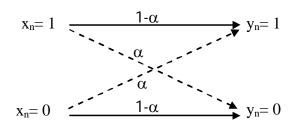

Depending on the transmission channel model, the decoder input value,  $y_n$ , can be differently defined. In Binary Symmetric Channel (BSC) model, each bit  $x_n$  in **x** is flipped with a probability  $\alpha$  called channel crossover probability as described in Figure 2.3 forming  $y_n$ , *i.e.*  $y_n = x_n$  with  $p = 1 - \alpha$  and  $y_n = not(x_n)$  with  $p = \alpha$ .