#### THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Bretagne Loire

En Cotutelle Internationale avec

Carleton University, Ottawa, canada

pour le grade de

#### **DOCTEUR DE L'UNIVERSITÉ DE RENNES 1**

Mention : Traitement du Signal et Télécommunications

**Ecole doctorale Matisse**

présentée par

#### Abdelaziz HAMDOUN

préparée à l'unité de recherche UMR 6164 – I.E.T.R Institut d'Electronique et de Télécommunications de Rennes ISTIC – UFR Informatique et Electronique

**Design of GaN-based microwave** components and application to novel high power reconfigurable antennas.

Thèse soutenue à Rennes le 19 Octobre 2016 devant le jury composé de :

Nathalie ROLLAND

Professeur à l'université de Lille 1, France / rapporteur

Mustapha YAGOUB

Professeur à l'université d'Ottawa, Canada / rapporteur Olivier LAFOND

Maitre de Conférence à l'université de Rennes 1, France / membre Steve McGARRY

Maitre de Conférence à l'université de Carleton, Ottawa, Canada / membre

Mohamed HIMDI

Professeur à l'université de Rennes 1, France / Directeur de thèse Langis ROY

Professeur à l'université de Carleton, Ottawa, Canada / Directeur de

Xavier CASTEL

Maitre de Conférence à l'université de Rennes 1, France / membre

Maitre de Conférence à l'université de Carleton, Ottawa, Canada / membre invité

#### Table of Contents

| Table of Contents                                         |       |

|-----------------------------------------------------------|-------|

| List of Figures                                           |       |

| List of tables                                            | vi    |

| List of Acronyms                                          | vii   |

| Acknowledgements                                          | ix    |

| Abstract                                                  | 1     |

| Résumé en français                                        | 2     |

| CHAPTER I                                                 | 1     |

| Introduction I. Research Motivations                      |       |

| II. Objective of Research                                 | 5     |

| III. Thesis Organisation                                  | 6     |

| CHAPTER II                                                | 7     |

| A Review of the Literature of Gallium Nitride Technology  |       |

| 1. Overview                                               | 7     |

| 2. Choice of the Substrate                                | 14    |

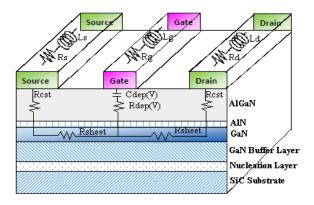

| II. NRC GaN500 MMIC HEMT Process Features and Limitations | 16    |

| III. Use of GaN in Reconfigurable RF/Microwave Systems    | 21    |

| IV. Summary                                               | 32    |

| CHAPTER III                                               | 33    |

| GaN Varactor and Switch Devices Modeling  I. Introduction |       |

| II. GaN-based Varactors Diodes Modeling                   | 36    |

| 1. Review of GaN HEMT for Power Varactors Diodes Applica  | tions |

|                                                           | 36    |

| 2. Realized GaN HEMT-based Varactor Diodes           | 46           |

|------------------------------------------------------|--------------|

| 3. GaN500v1 and GaN150v0 Varactor Devices            | 47           |

| 3.1 Small Signal Modeling                            | 48           |

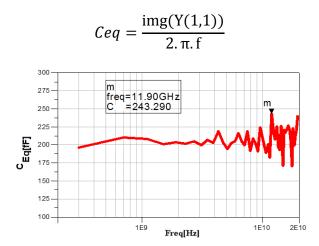

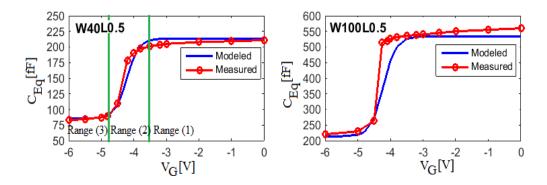

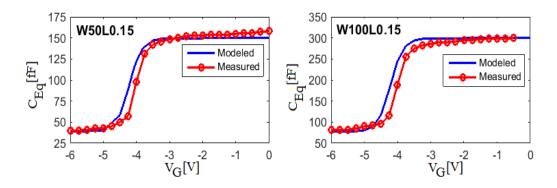

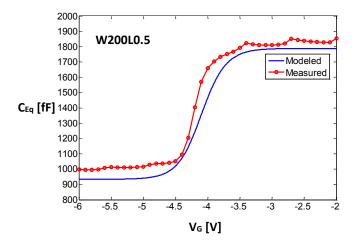

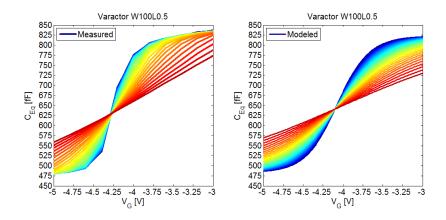

| 3.1.1 Analysis of Equivalent Capacitance             | 52           |

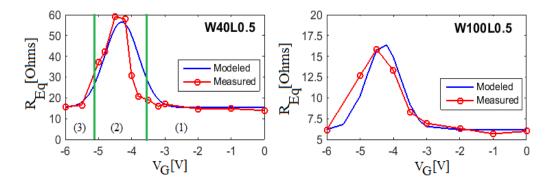

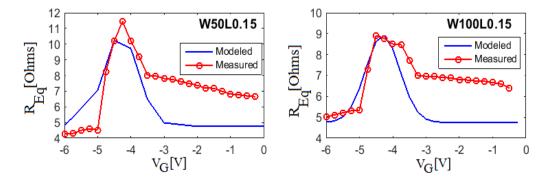

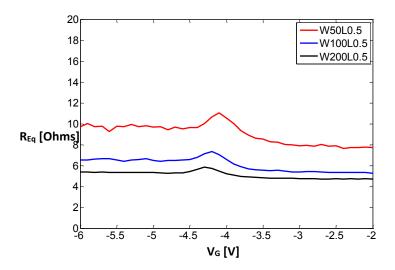

| 3.1.2 Analysis of Equivalent Series resistance       | 55           |

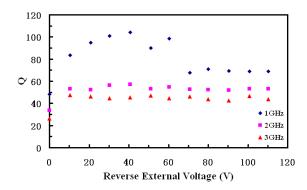

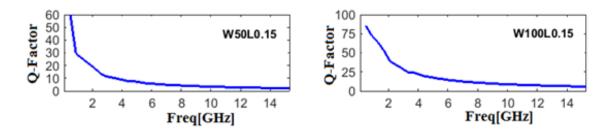

| 3.1.3 Analysis of Q-Factor                           | 56           |

| 4. GaN500v2 Varactor Devices                         | 58           |

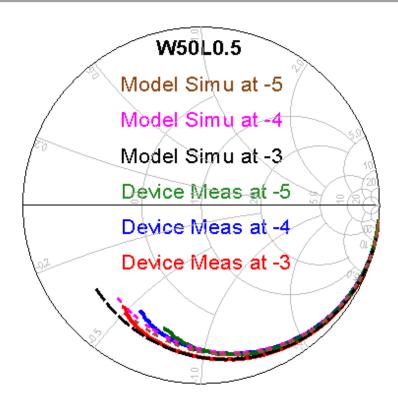

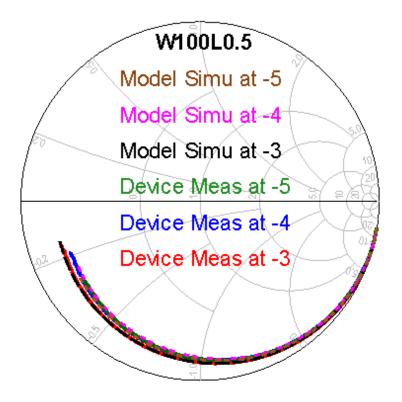

| 4.1 Small Signal Measurement                         | 58           |

| 4.1.1 Analysis of Equivalent Capacitance             | 61           |

| 4.1.2 Analysis of Equivalent Series Resistance       | 65           |

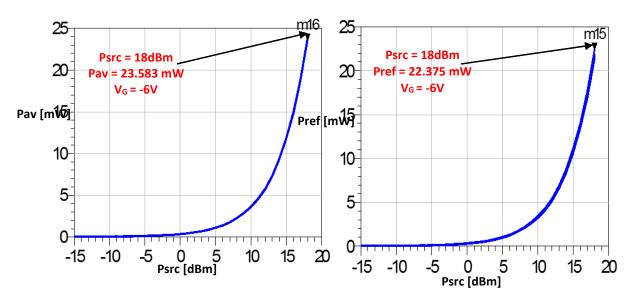

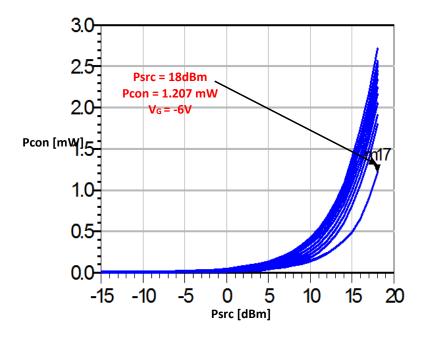

| 4.2 Large Signal Measurements                        | 68           |

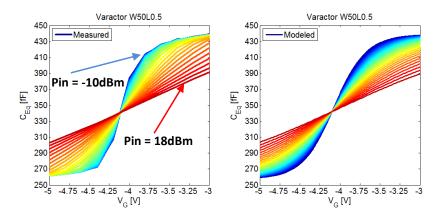

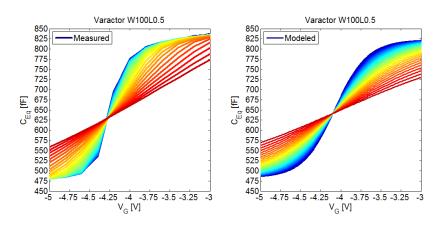

| 4.2.1 Analysis of Equivalent Capacitance             | 69           |

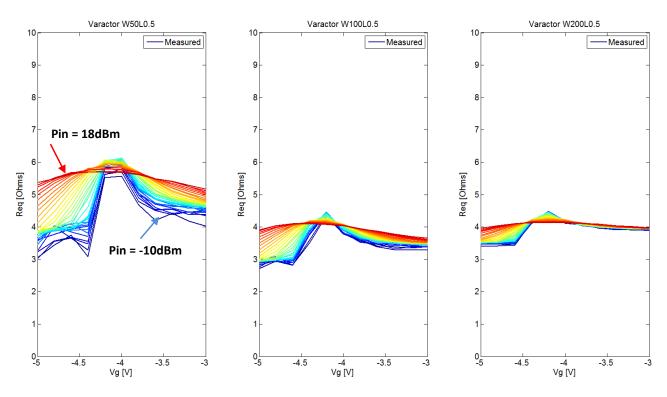

| 4.2.2 Analysis of Equivalent Series Resistance       | 71           |

| 5. Summary                                           | 74           |

| III. GaN-based Switch Devices Modeling               | 75           |

| 1. Review of GaN HEMT for Power Switching Devices A  | applications |

|                                                      | 75           |

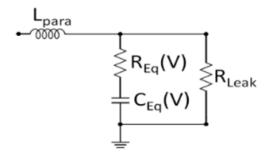

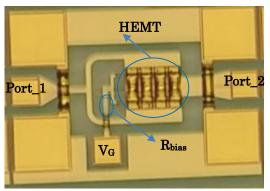

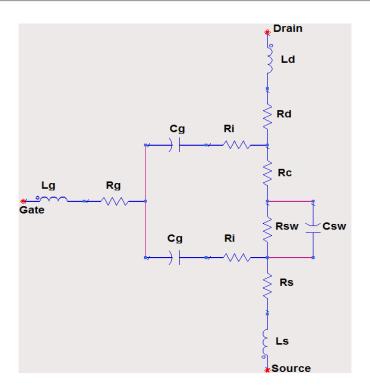

| 2. NRC GaN Switch Modeling                           | 78           |

| 2.1 Proposed GaN Single Switch Model                 | 78           |

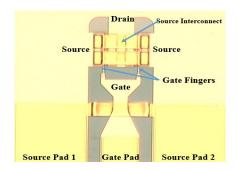

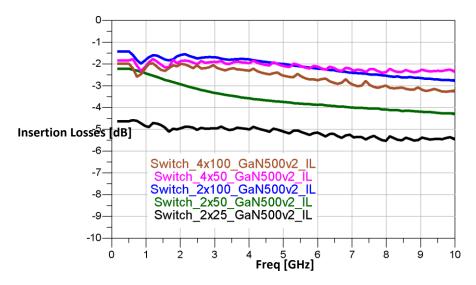

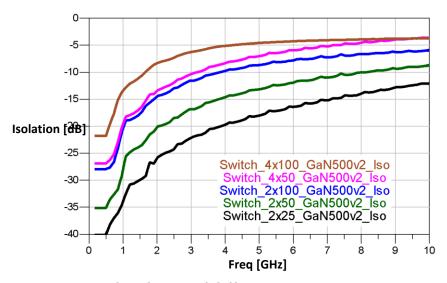

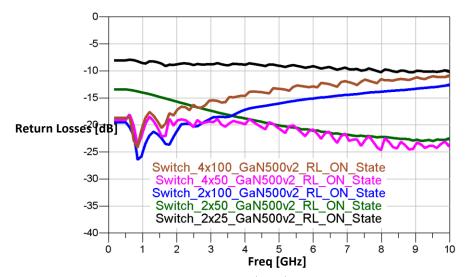

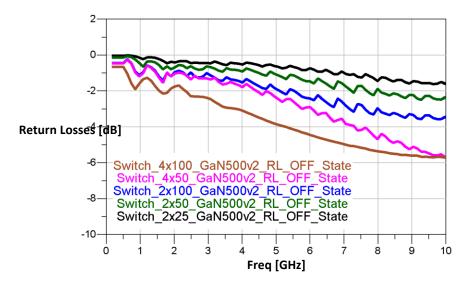

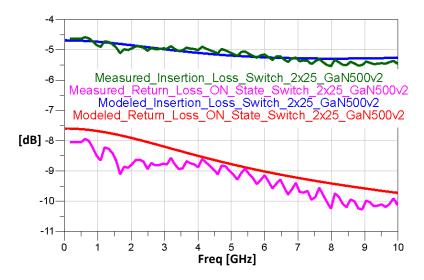

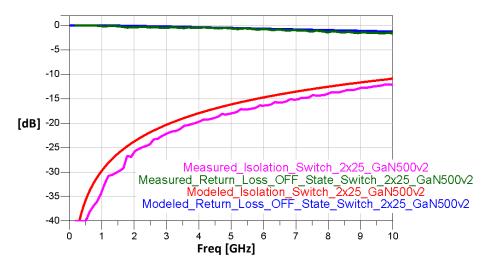

| 3. GaN500v2 Small Signal Switches Measurements       | 82           |

| 3.1 Different Sizes Standalone Signal Switch Devices | 82           |

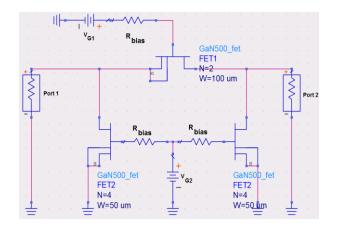

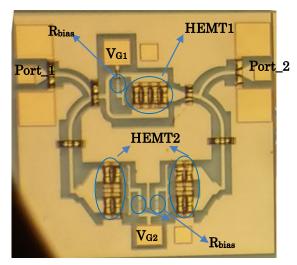

| 3.2 SPST Switch Structure                            | 87           |

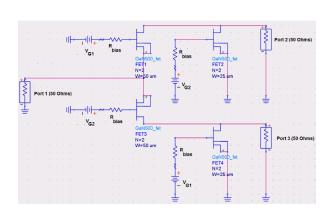

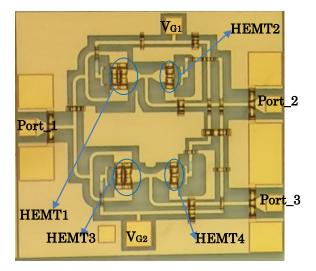

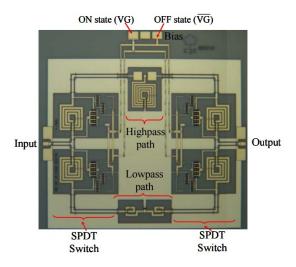

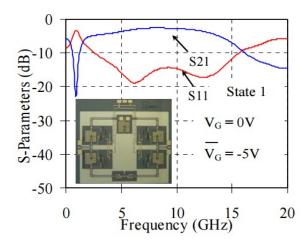

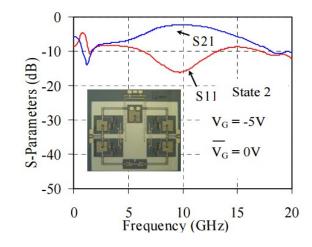

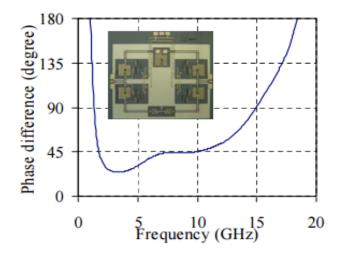

| 3.3 SPDT Switch Structure                            | 89           |

| IV. Summary                                          | 92           |

| CHAPTER IV                                           | 94           |

|                                                      |              |

| Realized GaN-Based Reconfigurable Circuits           | 94           |

| I. Introduction                                 | 94  |

|-------------------------------------------------|-----|

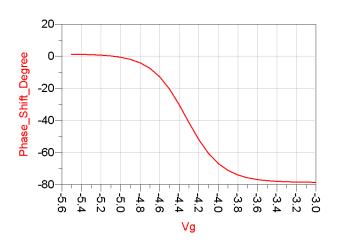

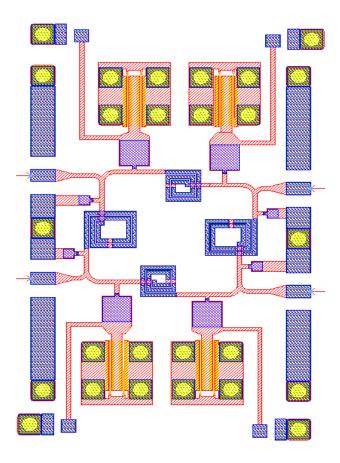

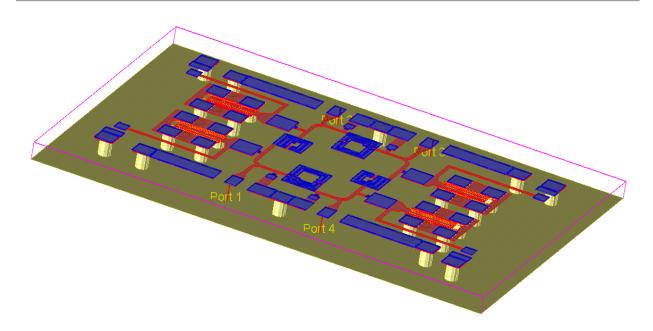

| II. Tunable Phase Shifters                      | 97  |

| 1. Review                                       | 97  |

| 2. Design of Analog GaN-based Phase Shifter     | 105 |

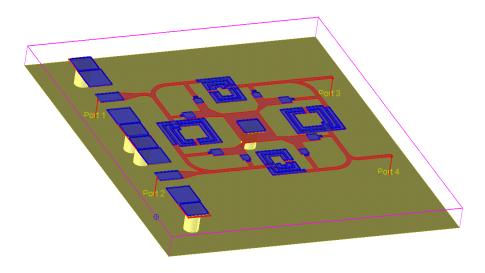

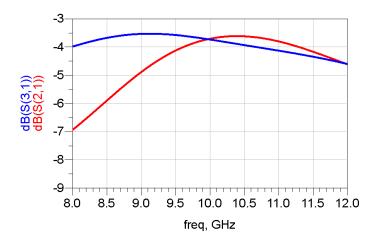

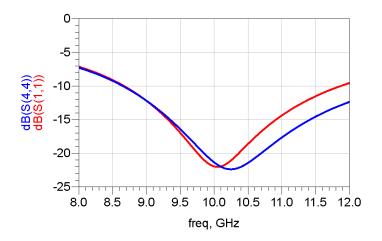

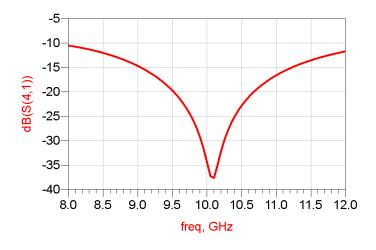

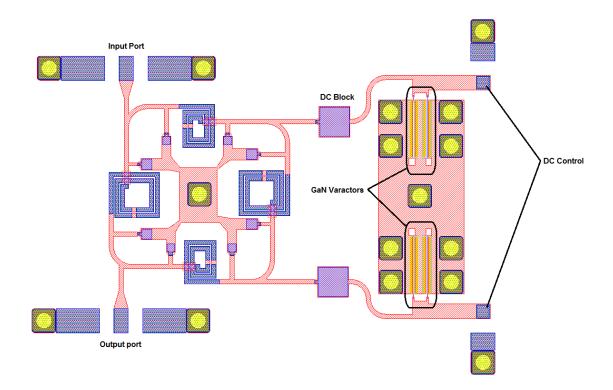

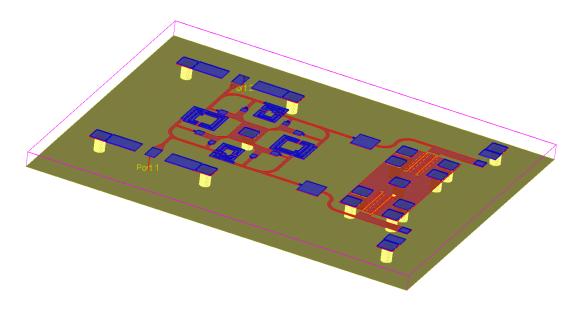

| 2.1 Quadrature 3-dB 90° Hybrid Coupler          | 108 |

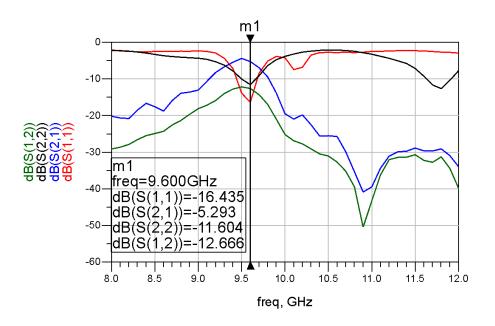

| 2.1.1. Simulated Results and Discussion         | 115 |

| 2.2 Phase Shifter Design                        | 117 |

| 2.1.2. Simulated Results and Discussion         | 119 |

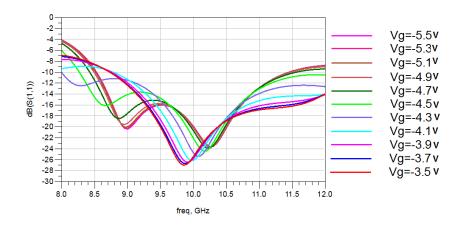

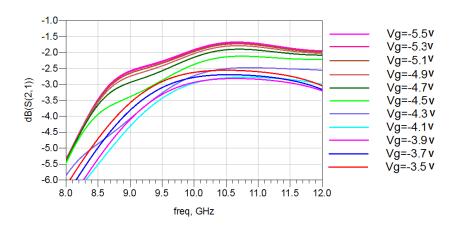

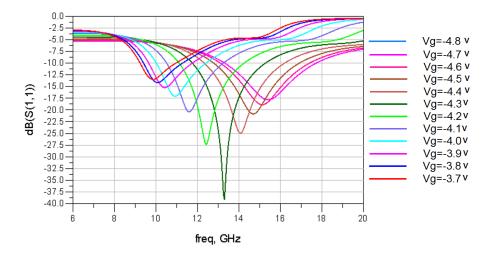

| III. GaN Reconfigurable 3-dB/90° Hybrid Coupler | 122 |

| 1. Review                                       | 122 |

| 2. Design of Reconfigurable 3-dB/90° Coupler    | 124 |

| 2.1 Simulated Results and Discussion            | 125 |

| IV. GaN-based Oscillator                        | 129 |

| 1. Review                                       | 129 |

| 2. Design of GaN-based Oscillators              | 132 |

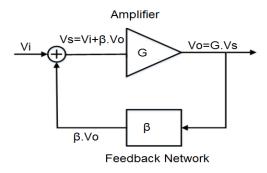

| 2.1 Feedback Oscillator Topology                | 133 |

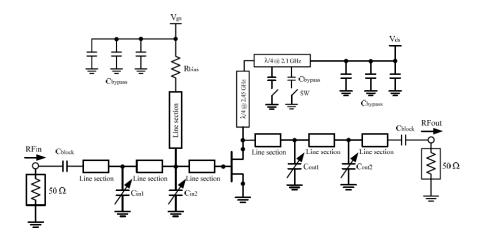

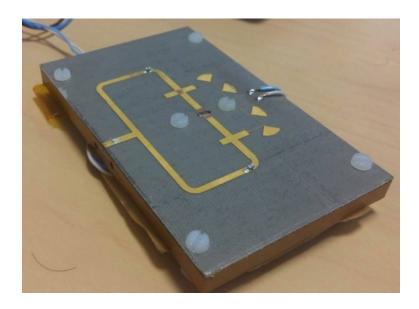

| 2.2 Power Amplifier Design                      | 133 |

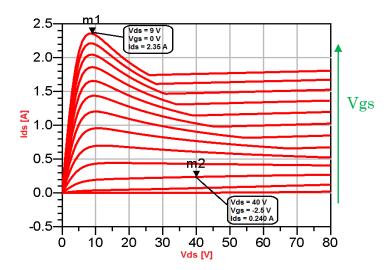

| 2.2.1 PA Design Procedure                       | 133 |

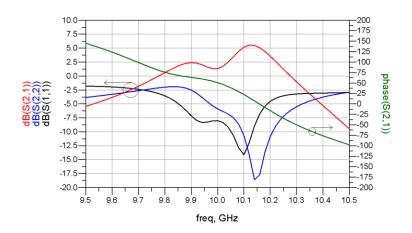

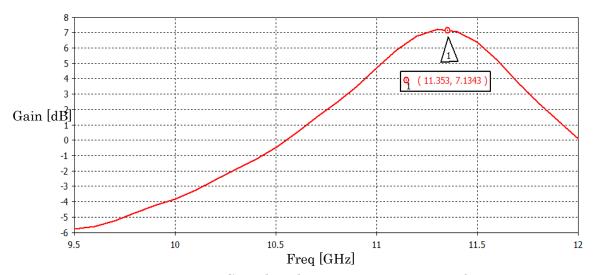

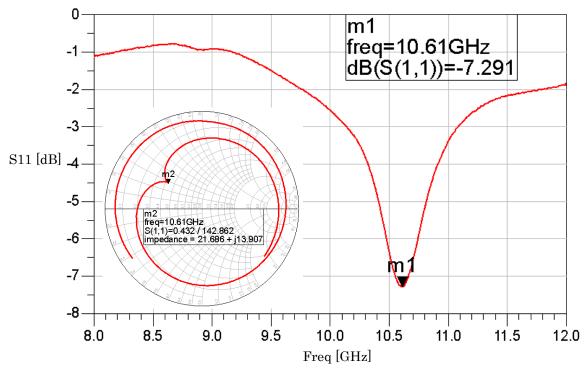

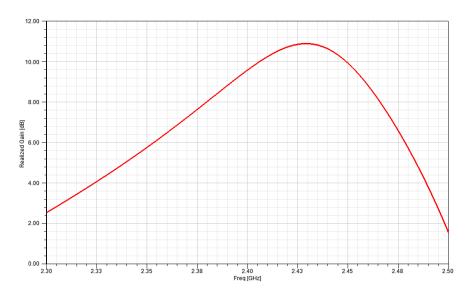

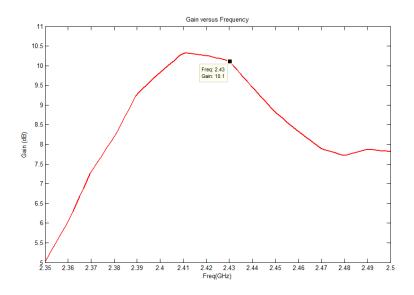

| 2.2.2 PA Simulated Results                      | 140 |

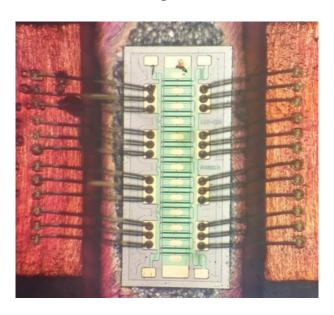

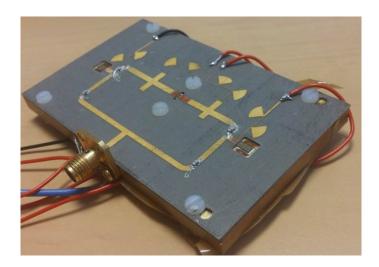

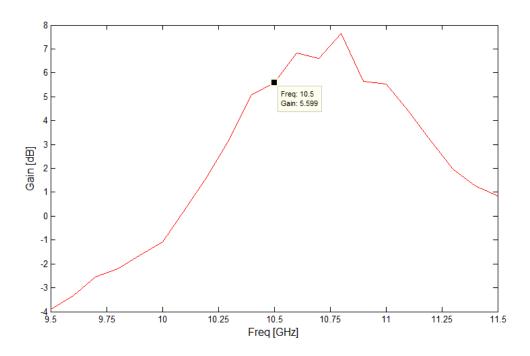

| 2.2.3 PA Measured Results                       | 140 |

| 3. Oscillator Design                            | 142 |

| 3.1 Start-up Oscillation Condition              | 142 |

| 3.2 Phase Noise in Oscillator                   | 144 |

| 3.3 Fixed Frequency Oscillator (FFO)            | 145 |

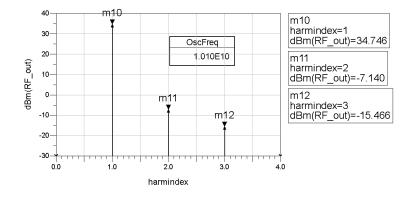

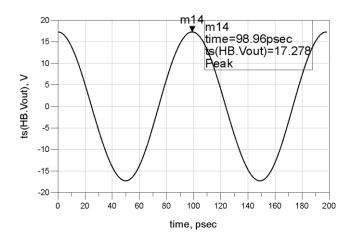

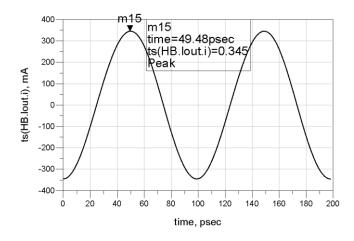

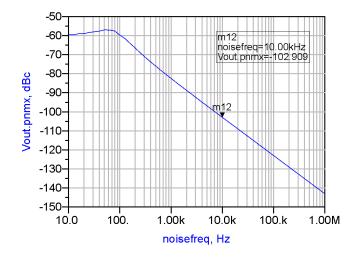

| 3.3.1 Simulation Results                        | 145 |

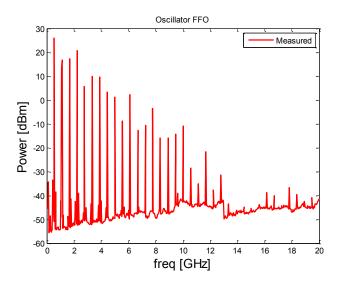

| 3.3.2 Measurements Results                      | 148 |

| 3.4 Tunable Frequency Oscillator (TFO)          | 149 |

| 3.4.1 Simulation Results                                 | 149      |

|----------------------------------------------------------|----------|

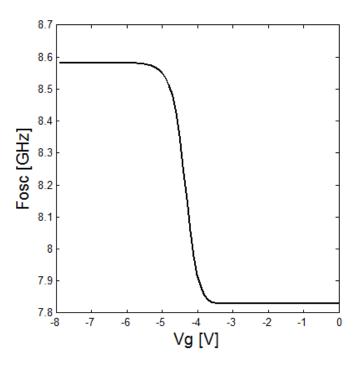

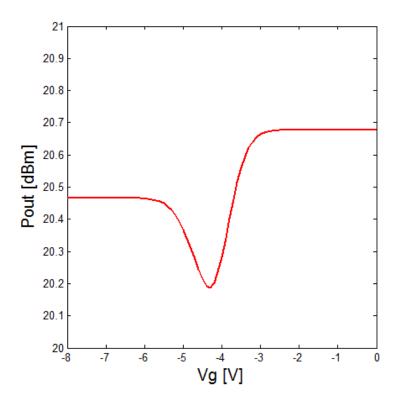

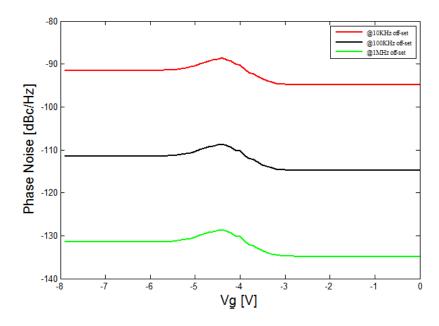

| 3.4.2 Measurement Results                                | 152      |

| V. Frequency Reconfigurable Active Antennas              | 153      |

| 1. Review                                                | 153      |

| 2. Reconfigurable Annular Slot Antenna using GaN Varacto | or 154   |

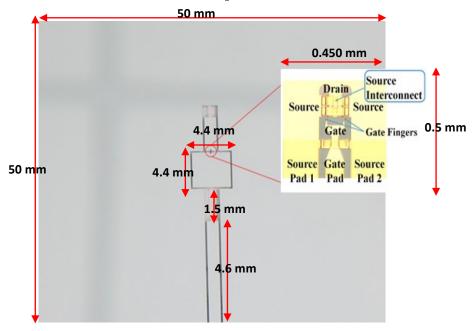

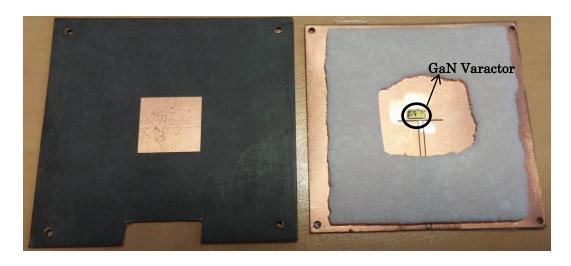

| 2.1 Antenna Design                                       | 154      |

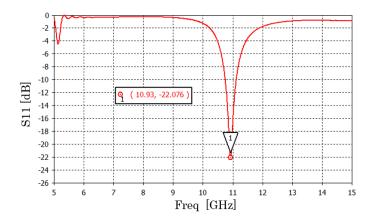

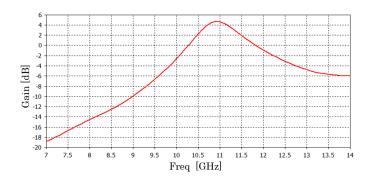

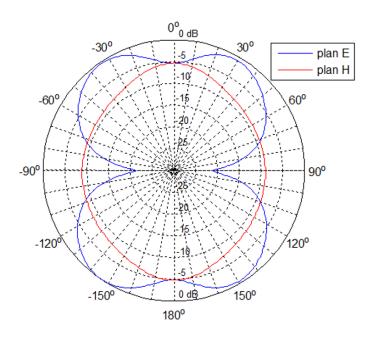

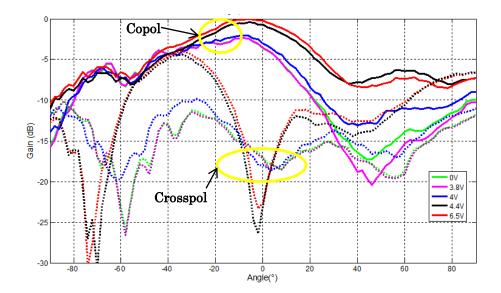

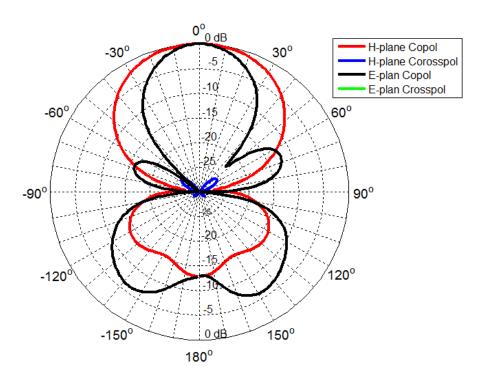

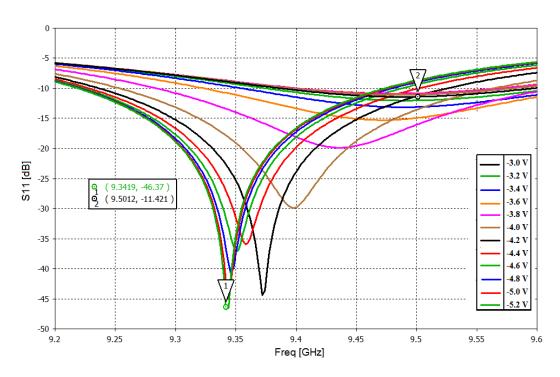

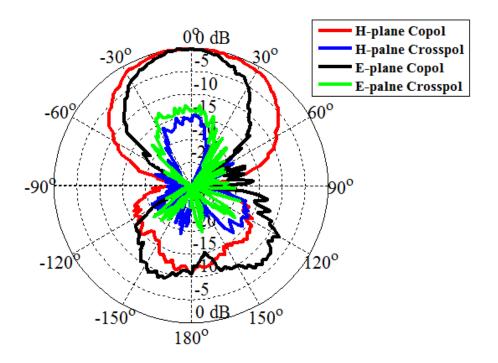

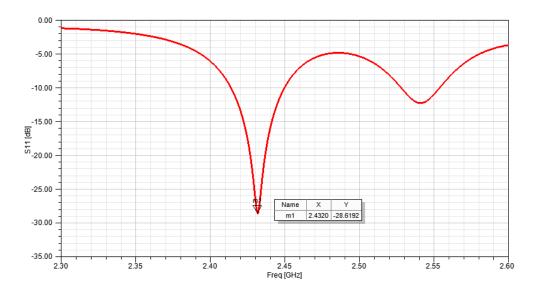

| 2.2 Simulated Return Loss and Radiation Pattern          | 155      |

| 2.3 Measured Return Loss and Radiation Pattern           | 158      |

| 3. Reconfigurable Aperture Coupled Slot Antenna using Ga | .N       |

| Varactor                                                 | 162      |

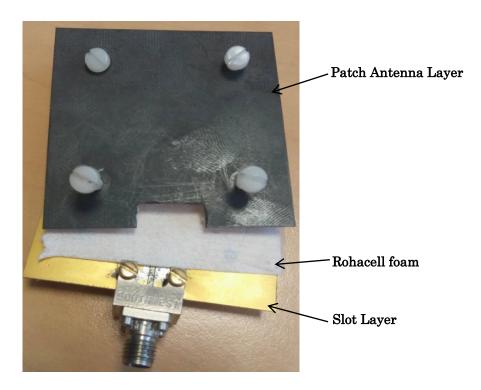

| 3.1 Antenna Design                                       | 162      |

| 3.2 Simulated Return Loss and Radiation Pattern          | 163      |

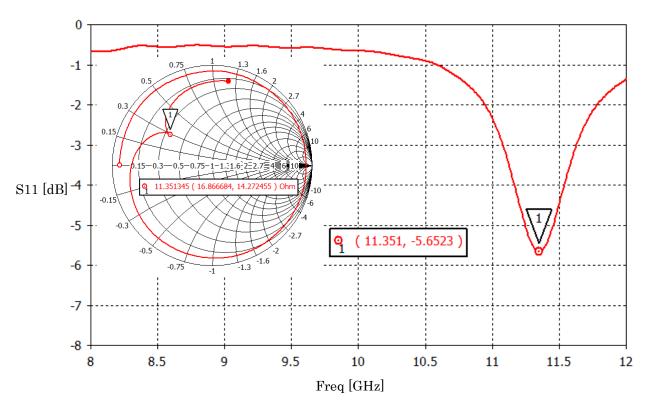

| 3.3 Measured Return Loss and Radiation Pattern           | 167      |

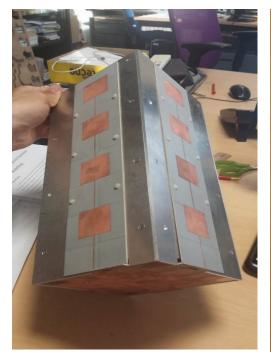

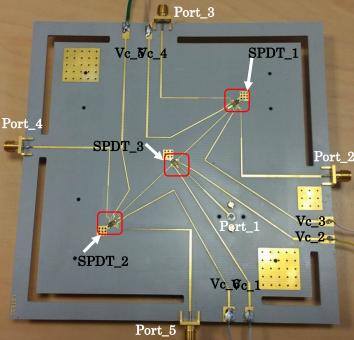

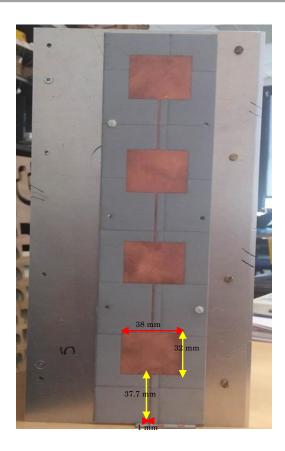

| 4. Beam Steering Patch Antenna Arrays using GaN SPDT S   | Switch   |

| Structure                                                | 170      |

| 4.1 Antenna Design                                       | 170      |

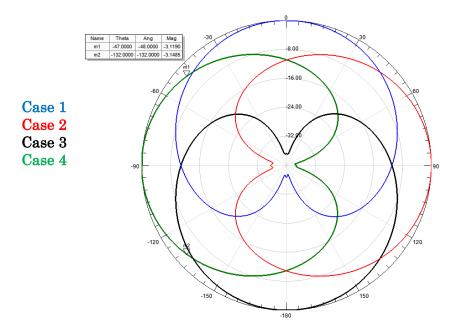

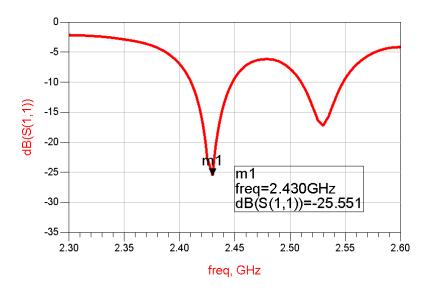

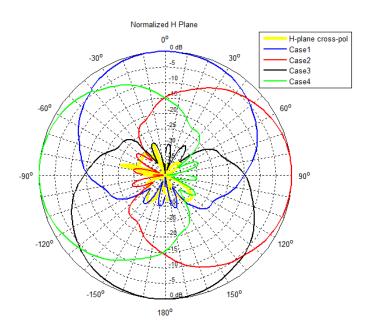

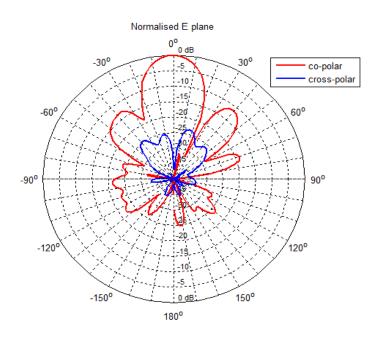

| 4.2 Simulated Return Loss and Radiation Pattern          | 174      |

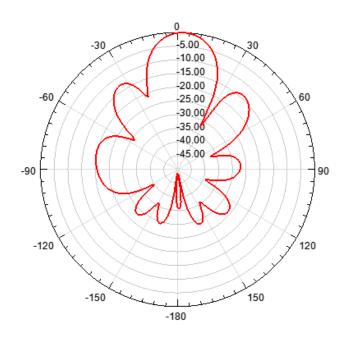

| 4.3 Measured Return Loss and Radiation Pattern           | 178      |

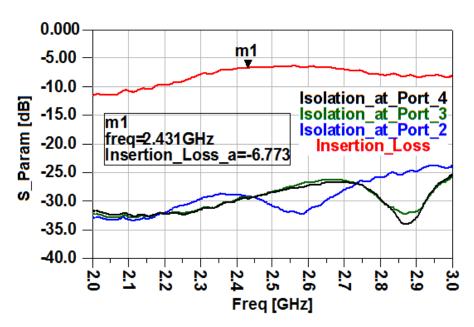

| 4.4 Measured Insertion Loss and Isolation of the Feeding | g System |

|                                                          | 181      |

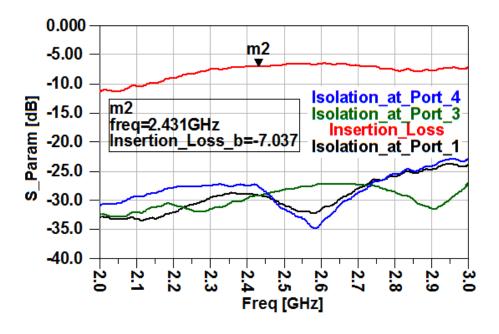

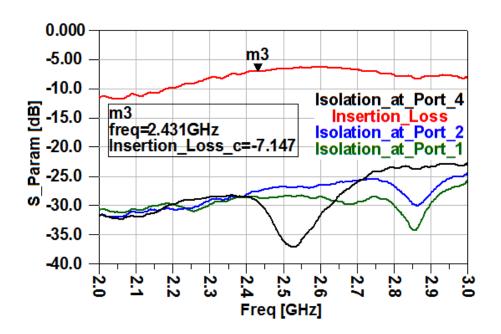

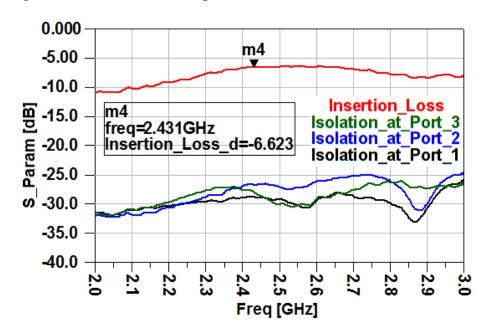

| 4.4.1 Small Signal Measurements                          | 181      |

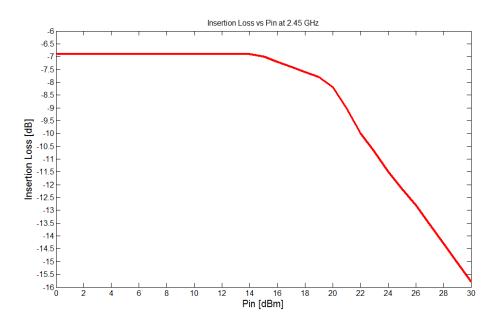

| 4.4.2 Large Signal Measurements                          | 184      |

| VI. Summary                                              | 185      |

| CHAPTER V                                                | 186      |

| Conclusion and Future Work                               | 186      |

| Ribliography                                             | 1        |

## List of Figures

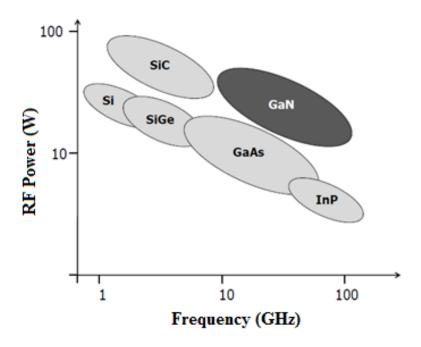

| Figure II.1: Most used Semiconductor Technologies and their Frequency/Power limits [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

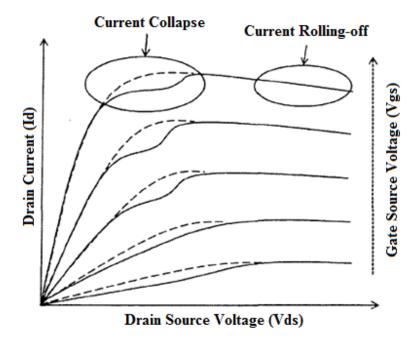

| Figure II.2: Current due to trapping effect and thermal effect [18]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11   |

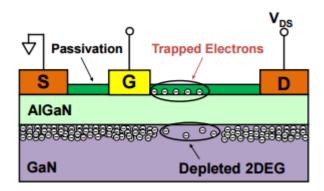

| Figure II.3: A sketch of an AlGaN/ GaN HEMT structure with trapped electrons [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12   |

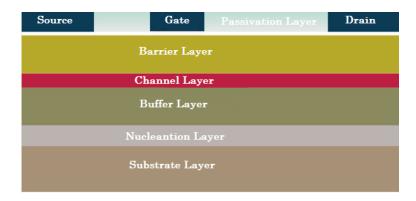

| Figure II.4: Cross-Section of HEMTs (Not Drawn to Scale)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13   |

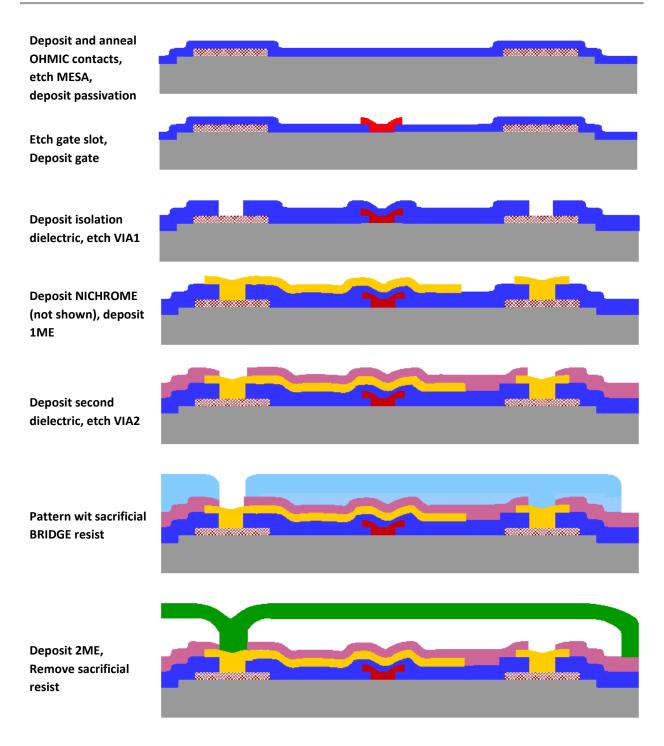

| Figure II.5: Cross-sectional view of HFET, showing process sequence (not to scale) [31]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19   |

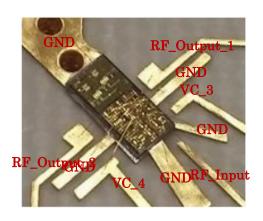

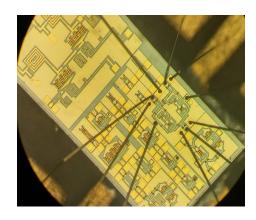

| Figure II.6: Photo of a T/R-Module front-end with GaN MMIC chips [43]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22   |

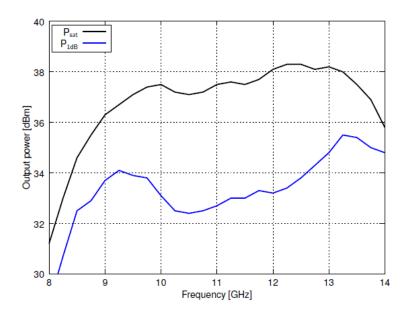

| Figure II.7: Measured output power versus frequency of the GaN MMIC DA at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23   |

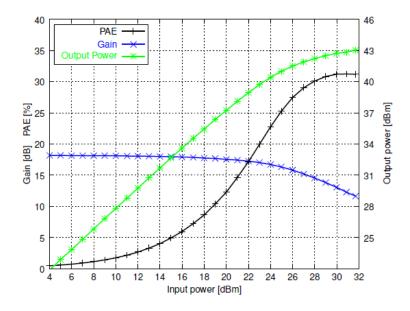

| Figure II.8: Measured power performance of the GaN MMIC HPA at 11 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23   |

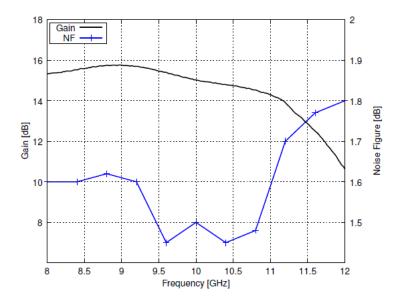

| Figure II.9: Measured gain and noise figure versus frequency of the GaN MMIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24   |

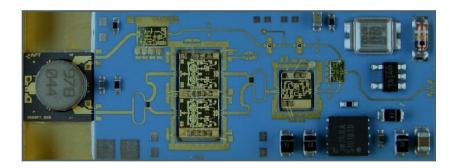

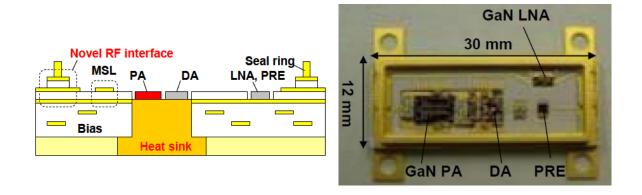

| Figure II.10: (Left) A schematic view and (Right) a photograph of the Fabricated T/R module us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | sing |

| HTCC technology [44]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24   |

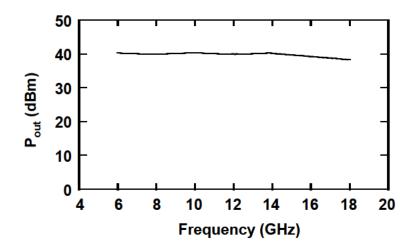

| Figure II.11: Measured Pout of fabricated T/R module as a function of frequency, biased at $30~\mathrm{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | [44] |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25   |

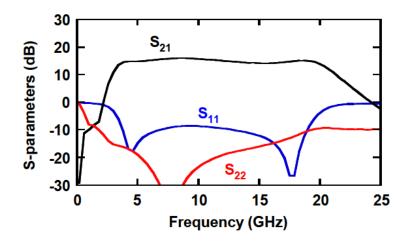

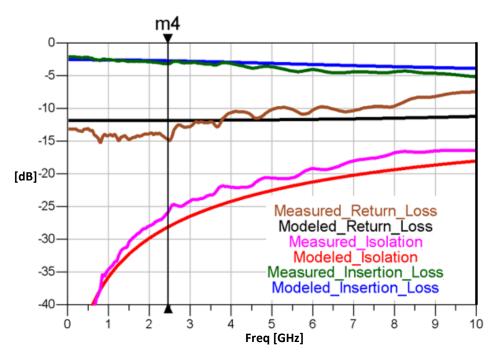

| Figure II.12: Measured S-parameters of GaN LNA MMIC (Vds = 15 V) [44]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25   |

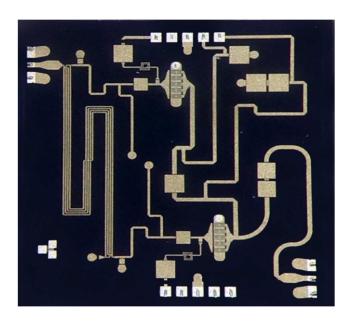

| Figure II.13: Photograph of the fabricated amplifier [45]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26   |

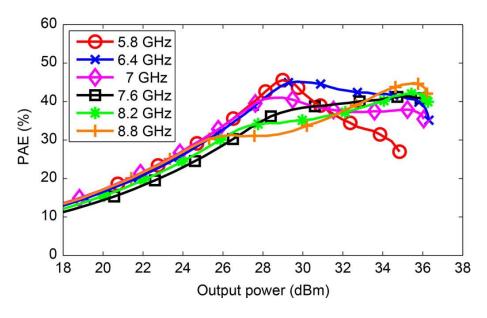

| Figure II.14: Measured PAE versus output power [45]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26   |

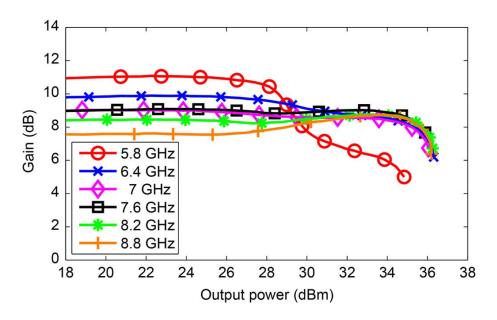

| Figure II.15: Measured gain versus output power [45]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27   |

| Figure~II.16: The ~concept~of~impedance~matching~conditions~of~the~band~and~class~reconfigurable~polynomial conditions~of~the~band~and~class~reconfigurable~polynomial conditions~of~the~band~and~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polynomial~class~reconfigurable~polyn   | wer  |

| amplifier [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28   |

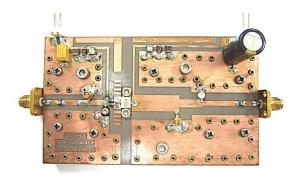

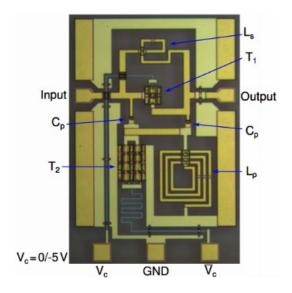

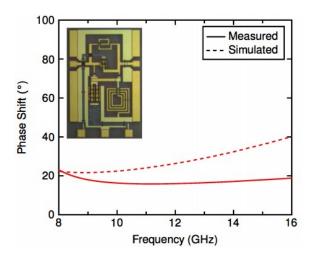

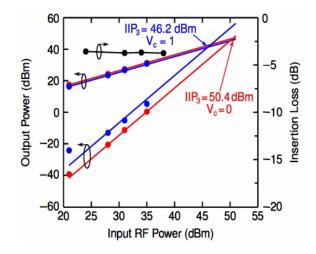

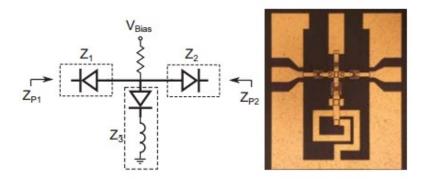

| Figure II.17: Photograph of the fabricated class-reconfigurable power amplifier [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28   |

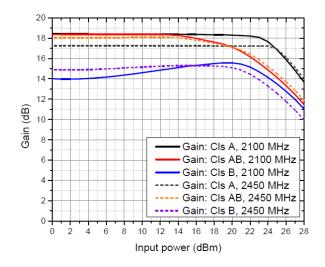

| Figure II.18: Simulated gain verses input power at different matching states [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28   |

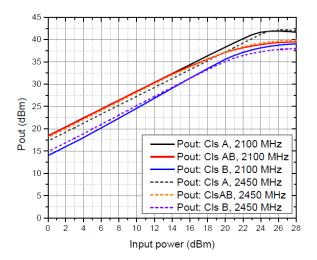

| Figure II.19: Simulated output power verses input power at different matching states [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29   |

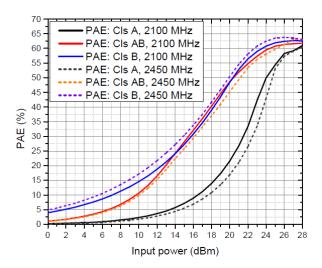

| Figure II.20: Simulated power added efficiency verses input power at different matching states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | [46] |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29   |

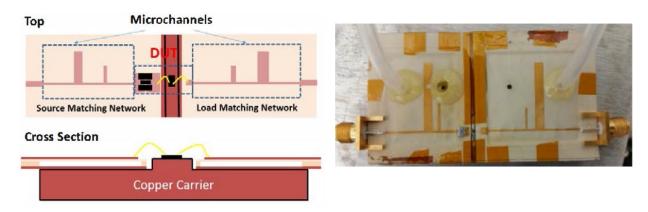

| Figure II.21: (Left) Top and cross sectional view and (Right) Picture of the packaged PA [47]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30   |

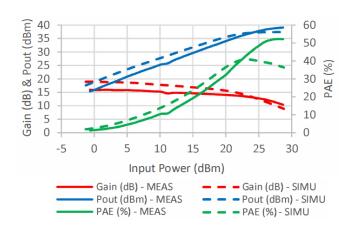

| Figure II.22: Acetone configuration: measurements at 2.3 GHz, simulations at 2. 4 GHz [47]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30   |

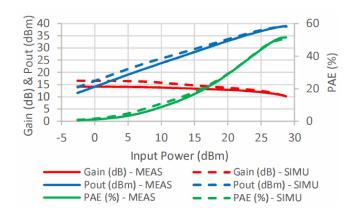

| Figure II.23: Air configuration: measurements at 5.7 GHz, simulations at 5.8 GHz [47]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31   |

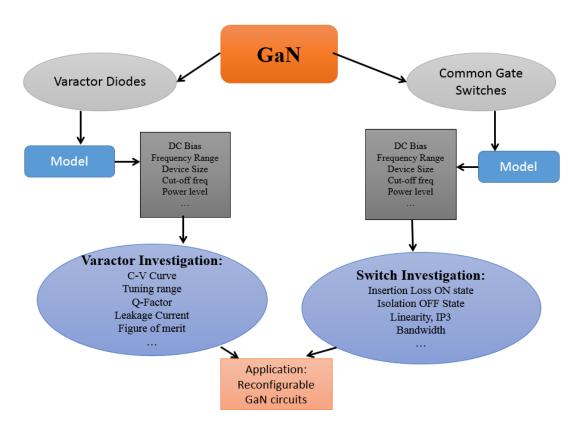

| Figure III.1: Work Plan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35   |

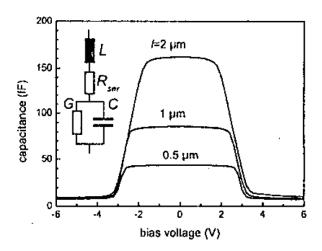

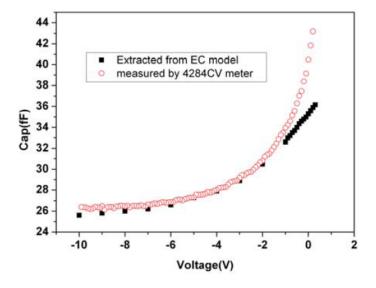

| Figure III.2: C-V characteristics of devices with different electrode length (spacing = 1 um, width =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | = 50 |

| um) [53]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37   |

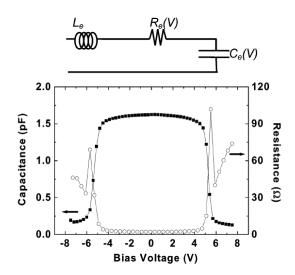

| $ Figure \ III.3: \ Extracted \ capacitance \ (black \ line) \ and \ resistance \ (white \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ and \ resistance \ (white \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ and \ resistance \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ MSM \ varactor \ columnwise \ (black \ line) \ of \ the \ (black \ line) \ of \ (black \ line) \ of$ | ver  |

| the entire bias range at $1.1~\mathrm{GHz}$ . The inserted schematic shows the first-order equivalent circuit of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | the  |

| MSM varactor [54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38   |

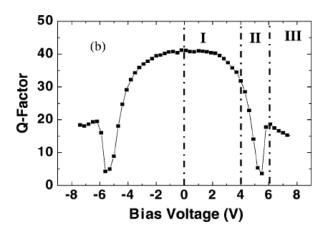

| Figure III.4: Q-factor versus tuning bias at 1.1 GHz [54]                                                    | 39       |

|--------------------------------------------------------------------------------------------------------------|----------|

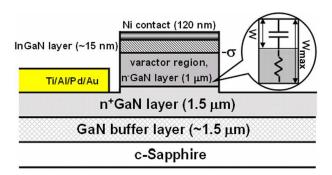

| Figure III.5: A Schematic diagram of the AlGaN/GaN-based varactor [55]                                       | 40       |

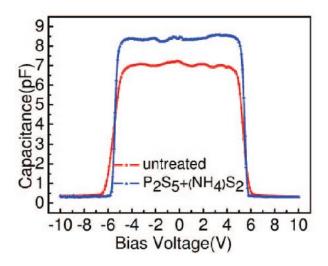

| Figure III.6: Measured C-V curves of the untreated and sulfur-treated AlGaN/GaN-based MSM                    |          |

| varactors [55]                                                                                               | 40       |

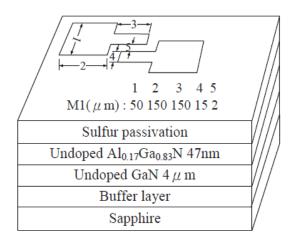

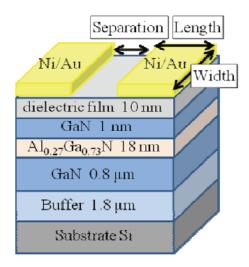

| Figure III.7: Schematic diagram of the AlGaN/GaN MSM-2DEG varactor of the samples prepared                   | ared in  |

| this study [56]                                                                                              | 41       |

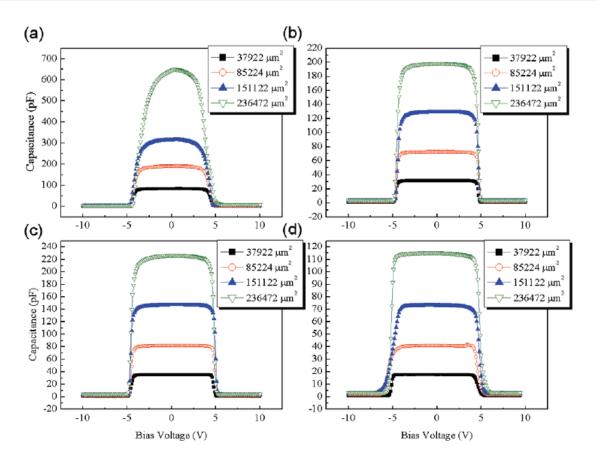

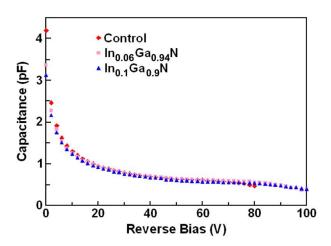

| Figure III.8: Capacitance-Voltage (C-V) characteristics of varactors with different electrode an             | reas (a) |

| without any dielectric film, (b) with SiO2 film, (c) with Gd2O3 film, and (d) with Si3N                      | 4 film.  |

| Measurement frequency = 1MHz, electrode area = 37922, 85224, 151122, and 236472                              | 2 μm2,   |

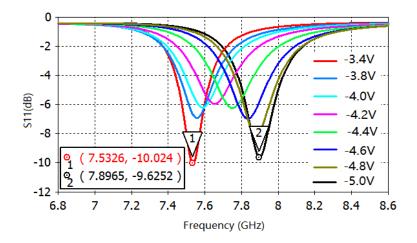

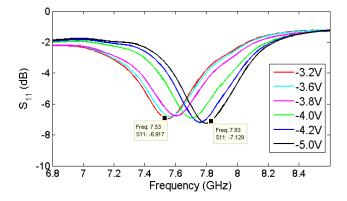

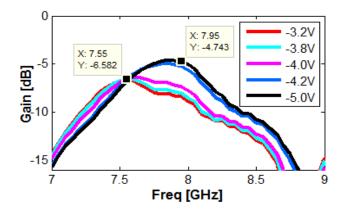

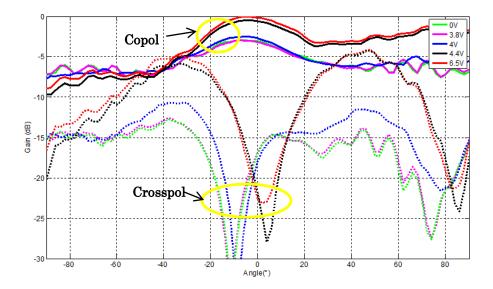

| respectively [56]                                                                                            | 42       |