École doctorale SPIM

# Génération automatique de tests à partir de modèles SysML pour la validation fonctionnelle de systèmes embarqués

# **THÈSE**

présentée et soutenue publiquement le 29 juin 2012

pour l'obtention du grade de

# Docteur de l'Université de Franche-Comté (Spécialité Informatique)

par

#### Jonathan Lasalle

#### Composition du jury

Président : Mr Jacques Julliand, Professeur à l'Université de Franche-Comté

Directeurs : Mr Fabrice Bouquet, Professeur à l'Université de Franche-Comté

Mr Fabien Peureux, Maître de Conférences à l'Université de Franche-Comté

Rapporteurs: Mr Jean-Michel Bruel, Professeur à l'Université de Toulouse

Mr Pierre-Alain Müller, Professeur à l'Université de Haute-Alsace

Examinateur : Mr Bernard Botella, Ingénieur au CEA/LIST

#### Remerciements

En premier lieu, je souhaite remercier Fabrice Bouquet et Fabien Peureux, pour m'avoir fait l'honneur d'être mes encadrants durant cette thèse, et pour m'avoir soutenu et fait confiance tout au long de cette aventure. Je remercie vivement Pierre-Alain Müller et Jean-Michel Bruel d'avoir accepté d'être rapporteurs de mes travaux et de m'avoir transmis une partie de leurs connaissances à travers leurs remarques. Merci également à Bernard Botella pour son expertise en qualité d'examinateur. Enfin, un grand merci à Jacques Julliand pour avoir accepté de présider le jury. Merci à vous tous pour l'évaluation faite de mes travaux.

Je tiens également à remercier Emilie Oudot, Brice Wittmann ainsi que Frédéric Fondement pour leur collaboration, contribuant ainsi à l'obtention des résultats présentés dans ce mémoire. Merci à mes parents et à Isabelle Jacques pour m'avoir aidé à chasser les fautes d'orthographe de ce document. J'ai ici également une pensée pour Christelle Bloch, Pascal Chatonnay et Fabrice Bouquet qui m'ont offert l'opportunité d'effectuer un stage de M2 recherche au sein du DISC, m'ouvrant ainsi la porte du monde de la recherche.

Je remercie également tous les membres du département DISC pour leur accueil et pour leur sympathie à mon égard. Merci à Jean-Christophe Lapayre et Olga Kouchnarenko pour m'avoir successivement accueilli au sein du LIFC puis du DISC. Merci à Frédéric Dadeau de m'avoir intégré au comité d'organisation de l'école d'été TAROT 2012, me permettant ainsi de contribuer à sa réussite. Enfin, merci à Fabien Peureux, encadrant, collègue et désormais ami, pour ses leçons phylosophico-culturelles de toute beauté.

Je profite également de cette occasion pour remercier tous ceux qui m'ont fait confiance en m'offrant la possibilité d'effectuer des enseignements. Merci à Jean-Michel Hufflen pour sa confiance en m'ayant laissé seul maître à bord des TD de Scheme durant 5 années. Merci également à Françoise Greffier, Nicolas Janet, Christophe Lang, François Piat et aux 3 Fab' du bureau 425C.

Je voudrais remercier mes frères et soeurs ainsi que mes parents qui, de par leurs encouragements inconditionnels, m'ont permis d'atteindre ce but. Maman, papa, votre soutien sans faille durant ces vingt-trois années de scolarité se voit ici récompensé. Je ne vous en serai jamais assez reconnaissant.

A l'issu de toutes ces années, un bilan peut être dressé. Plus aucun doute n'est permis. Tu as raison Pierre-Christophe, je suis définitivement bavard. Je te remercie de m'avoir supporté et écouté (enfin...plutôt "entendu") durant toutes ces années d'étude. Merci à Stéphane, pour son soutien et pour son amitié inconditionnelle. Merci à Elizabeta, pour nos improbables discussions aux accents de l'Est. Merci également à Kalou, son petit frère et leur geekitude commune.

Merci à tous, compagnons de galère, compagnons de croissants, compagnons d'happy : Adrien, Ben, Elena, Jérôme, Julien, Laloi, Oscar, Rami, Régis, Sarga, Sébastien, Thomas, Yvan et tous ceux que j'oublie, pour leurs conseils (plus ou moins) avisés, pour cet environnement de travail convivial, pour cette ambiance détendue, éléments nécessaires à la réussite d'une telle épreuve. En espérant vivre avec vous d'autres aventures.

Enfin, un grand merci à tous les étudiants que j'ai croisés, durant toutes ces années, qui m'ont apporté tant de joie et de satisfaction... et tout particulièrement une étudiante, la plus ravissante de toutes, qui me montre jour après jour la voie, et qui est dorénavant mon épouse : Solaine, je t'aime.

A ma chère et tendre que j'aime infiniment . . .

# Table des matières

| Partie I | Contexte, problématiques et état de l'art                 | 1  |

|----------|-----------------------------------------------------------|----|

| Chapit   | re 1 Introduction                                         | 3  |

| 1.1      | Contexte                                                  | 4  |

| 1.2      | Le projet VETESS                                          | 8  |

| 1.3      | Problématiques                                            | 12 |

| 1.4      | Structure du document                                     | 13 |

| 1.5      | Exemple fil rouge : système d'éclairage avant de véhicule | 14 |

| Chapit   | re 2 Etat de l'art                                        | 17 |

| 2.1      | Model-Based Testing                                       | 18 |

| 2.2      | Stratégies de génération de tests                         | 19 |

|          | 2.2.1 Test aléatoire                                      | 19 |

|          | 2.2.2 Test exhaustif                                      | 20 |

|          | 2.2.3 Couverture structurelle                             | 21 |

|          | 2.2.4 Couverture des exigences                            | 22 |

|          | 2.2.5 Scénarios                                           | 23 |

|          | 2.2.6 Bilan                                               | 24 |

| 2.3      | Modélisation des systèmes embarqués                       | 25 |

|          | 2.3.1 Modélisation environnementale                       | 25 |

|          | 2.3.2 Langage de modélisation                             | 26 |

|          | 2.3.3 Représentation du temps                             | 32 |

| 2.4      | Synthèse                                                  | 33 |

| artie I | [ Co                         | ntributions                                   | 35   |

|---------|------------------------------|-----------------------------------------------|------|

| Chapit  | ${ m tre}\; { m 3}\; { m N}$ | Iodélisation en SysML pour le test            | 37   |

| 3.1     | Préser                       | ntation du langage SysML                      | . 38 |

|         | 3.1.1                        | Les diagrammes structurels                    | . 39 |

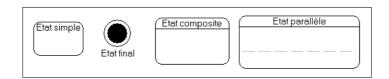

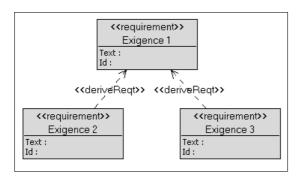

|         | 3.1.2                        | Les diagrammes comportementaux                | . 41 |

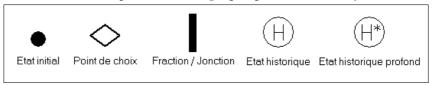

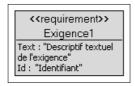

|         | 3.1.3                        | Le diagramme d'exigences                      | . 42 |

| 3.2     | SysMI                        | L pour le test (SysML4MBT)                    | . 42 |

|         | 3.2.1                        | Diagramme de bloc SysML4MBT                   | . 43 |

|         | 3.2.2                        | Diagramme interne de bloc SysML4MBT           | . 45 |

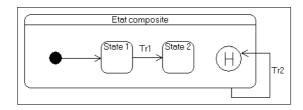

|         | 3.2.3                        | Diagramme d'états-transitions                 | . 47 |

|         | 3.2.4                        | OCL                                           | . 49 |

|         | 3.2.5                        | Représentation des exigences                  | . 50 |

|         | 3.2.6                        | Sémantique opérationnelle et contraintes      | . 51 |

| 3.3     | Comp                         | aratif entre SysML4MBT et UML4MBT             | . 56 |

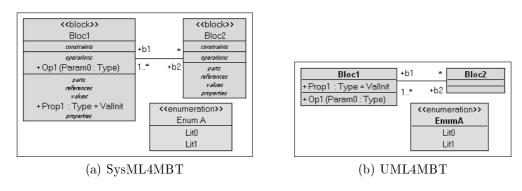

|         | 3.3.1                        | Diagramme de bloc                             | . 56 |

|         | 3.3.2                        | Diagramme interne de bloc                     | . 57 |

|         | 3.3.3                        | Diagramme d'états-transitions                 | . 57 |

|         | 3.3.4                        | Diagramme d'exigences                         | . 58 |

| 3.4     | $\operatorname{Cadre}$       | formel pour SysML4MBT                         | . 59 |

|         | 3.4.1                        | Structures nécessaires                        | . 59 |

|         | 3.4.2                        | Modèle SysML4MBT                              | . 60 |

|         | 3.4.3                        | Diagramme de définition de bloc               | . 60 |

|         | 3.4.4                        | Diagramme d'états-transitions                 | . 61 |

| 3.5     | Exem                         | ple fil rouge                                 | . 64 |

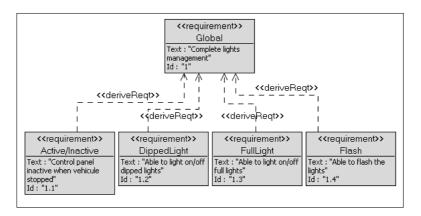

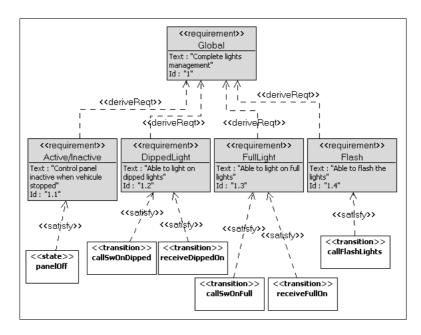

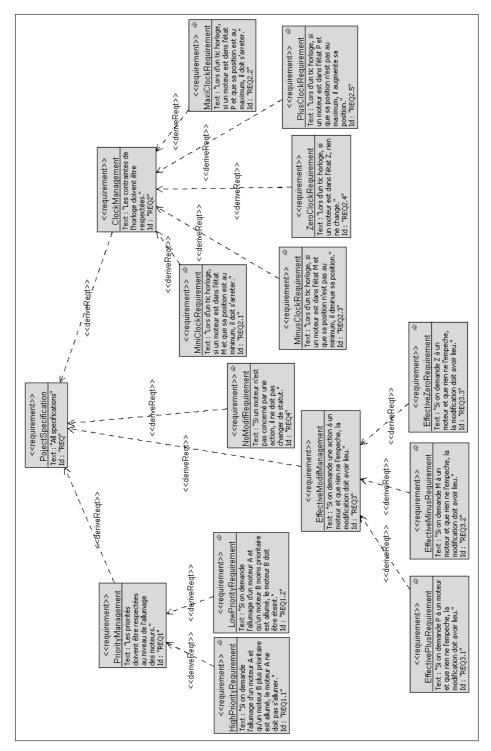

|         | 3.5.1                        | Représentation des exigences                  | . 64 |

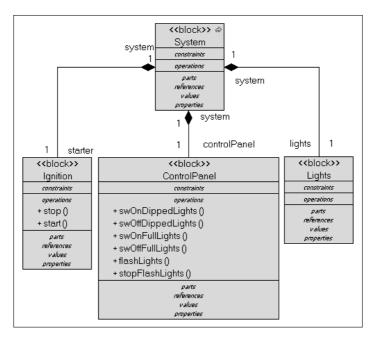

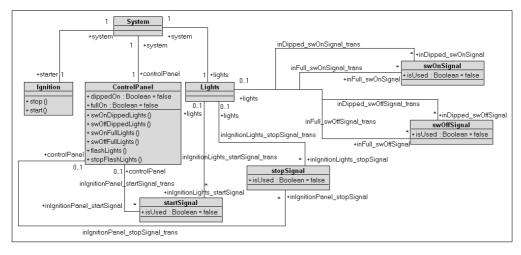

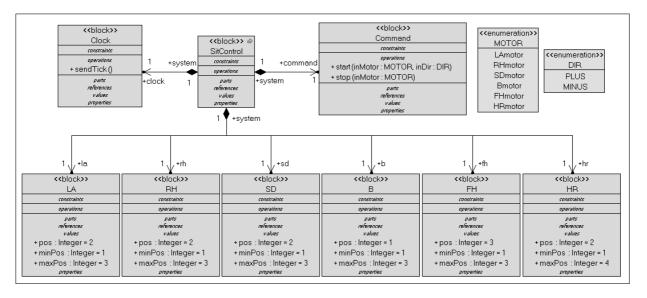

|         | 3.5.2                        | Représentation de la structure                | . 64 |

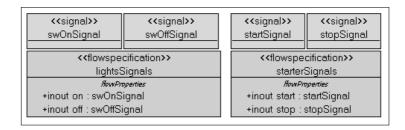

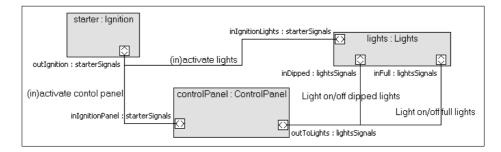

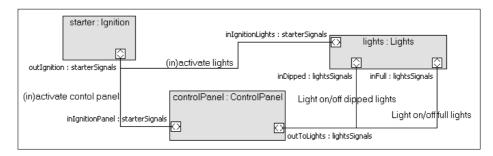

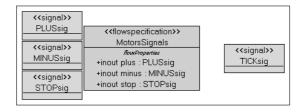

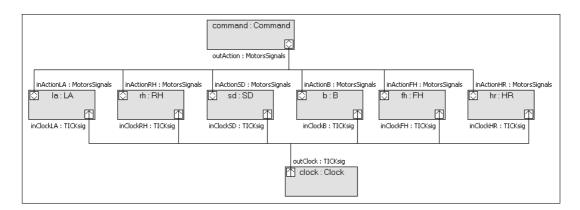

|         | 3.5.3                        | Représentation des communications             | . 66 |

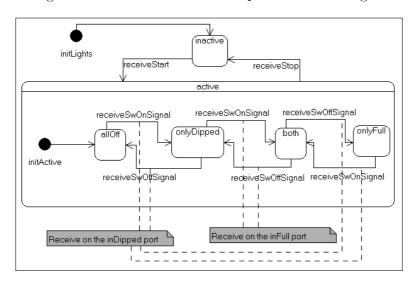

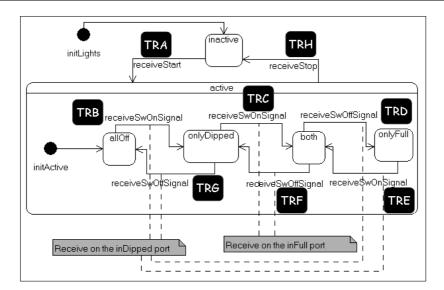

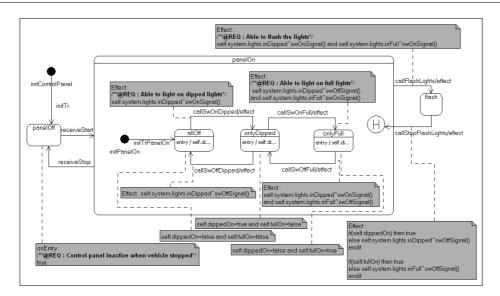

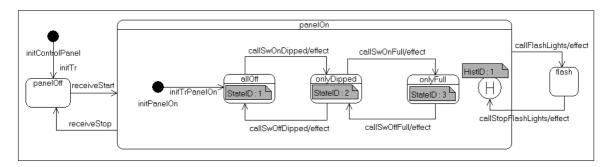

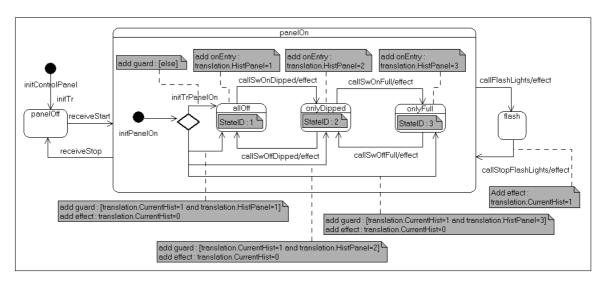

|         | 3.5.4                        | Représentation dynamique                      | . 68 |

|         | 3.5.5                        | Complément au diagramme d'exigences           | . 72 |

| 3.6     | Synth                        | èse                                           | . 73 |

| _       |                              | tratégies de couverture des modèles SysML     | 75   |

| 4.1     |                              | alisation des tests                           |      |

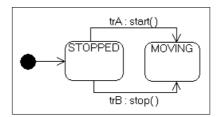

| 4.2     | Exem                         | ple d'illustration des critères de couverture | . 78 |

| 4.3       | Critèr  | es classiques de sélection de tests                                                         | 79  |

|-----------|---------|---------------------------------------------------------------------------------------------|-----|

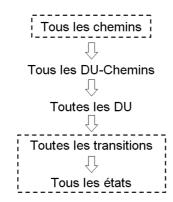

|           | 4.3.1   | Critère Tous les états                                                                      | 80  |

|           | 4.3.2   | Critère Toutes les transitions                                                              | 80  |

|           | 4.3.3   | Critère $Toutes\ les\ DU$                                                                   | 81  |

|           | 4.3.4   | Critère Tous les DU-Chemins                                                                 | 82  |

|           | 4.3.5   | Critère Tous les chemins                                                                    | 82  |

| 4.4       | Positio | onnement UML4MBT et analyse                                                                 | 83  |

| 4.5       | Critèr  | es de sélection de tests pour SysML4MBT                                                     | 84  |

|           | 4.5.1   | Critère D/CC                                                                                | 85  |

|           | 4.5.2   | Critère Toutes les $DU_{sig}$                                                               | 85  |

|           | 4.5.3   | Critère Tous les $DU_{sig}$ -Chemins                                                        | 86  |

|           | 4.5.4   | ComCover                                                                                    | 87  |

|           | 4.5.5   | Illustration                                                                                | 91  |

| 4.6       | Exem    | ple fil rouge                                                                               | 92  |

|           | 4.6.1   | Numérotation et rappels                                                                     | 92  |

|           | 4.6.2   | Tests générés par la stratégie $\mathit{Toutes}\ \mathit{les}\ \mathit{transitions} + D/CC$ | 94  |

|           | 4.6.3   | Tests générés par ComCover                                                                  | 94  |

|           | 4.6.4   | Vérification des métriques                                                                  | 94  |

| 4.7       | Synth   | èse                                                                                         | 96  |

|           |         |                                                                                             |     |

| Partie II | I R     | éalisations et expérimentations                                                             | 99  |

| Chapit    | re 5 Iı | mplémentation                                                                               | 101 |

| 5.1       |         | formation de SysML4MBT vers UML4MBT                                                         |     |

|           | 5.1.1   | Sous-ensembles UML4MBT et SysML4MBT communs                                                 |     |

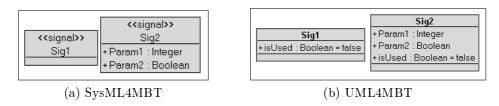

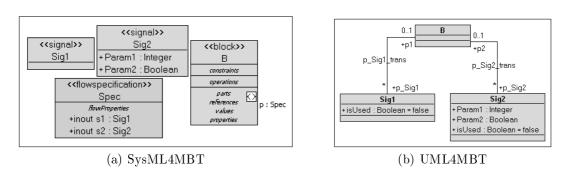

|           | 5.1.2   | Signaux et ports                                                                            |     |

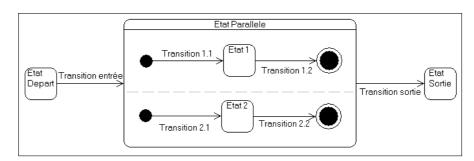

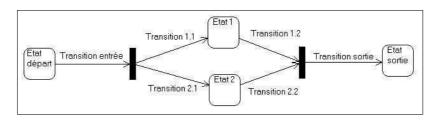

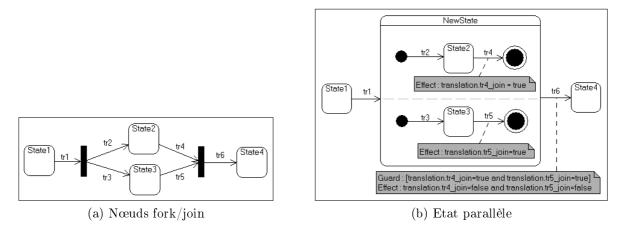

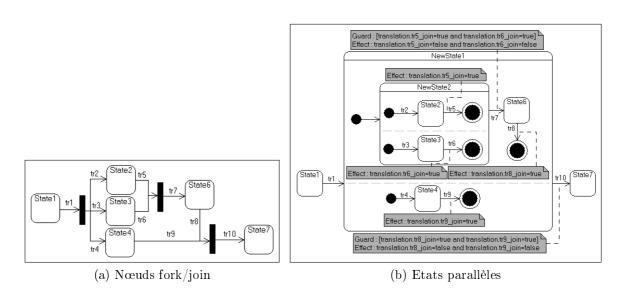

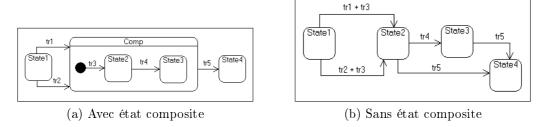

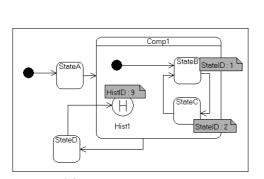

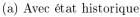

|           | 5.1.3   | Nœuds fork/join, états historiques et parallèles                                            | 107 |

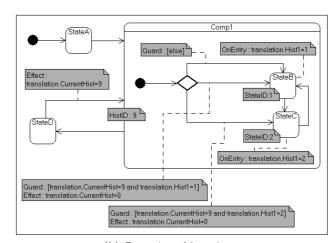

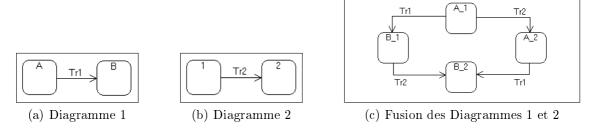

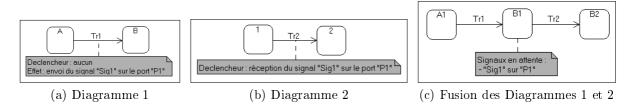

|           | 5.1.4   | Diagrammes d'états-transitions multiples                                                    | 112 |

|           | 5.1.5   | Création du diagramme d'objets                                                              | 116 |

|           | 5.1.6   | Exigences                                                                                   |     |

|           | 5.1.7   | Synthèse                                                                                    | 119 |

| 5.2       | Exem    | ple fil rouge                                                                               | 119 |

|           |         |                                                                                             | 110 |

|           | 5.2.1   | Diagramme d'exigences                                                                       |     |

|           | -       |                                                                                             | 119 |

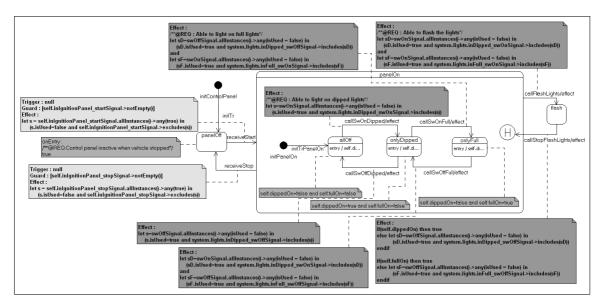

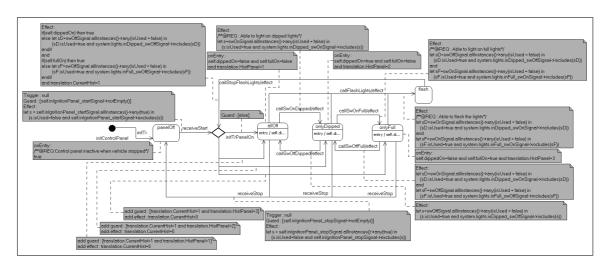

|            | 5.2.3  | Partie dynamique                          | . 121 |

|------------|--------|-------------------------------------------|-------|

|            | 5.2.4  | Diagramme d'objets                        | . 126 |

| 5.3        | Applie | cation de ComCover                        | . 126 |

|            | 5.3.1  | Justification de la surcharge             | . 126 |

|            | 5.3.2  | ComCover en appliquant la couverture D/CC | . 128 |

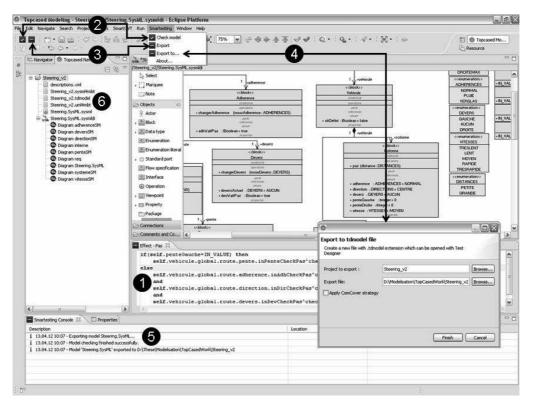

| 5.4        | Déplo  | iement                                    | . 129 |

| 5.5        | Synth  | èse                                       | . 130 |

| Chapit     | re 6 C | Chaîne outillée et expérimentations       | 131   |

| 6.1        | Gestic | on des systèmes discrets et continus      | . 133 |

|            | 6.1.1  | Systèmes discrets                         | . 134 |

|            | 6.1.2  | Systèmes continus                         | . 135 |

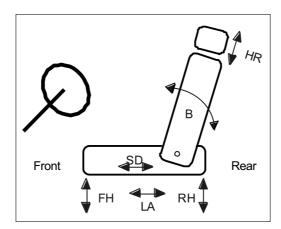

| 6.2        | Régla  | ge électronique d'un siège de véhicule    | . 136 |

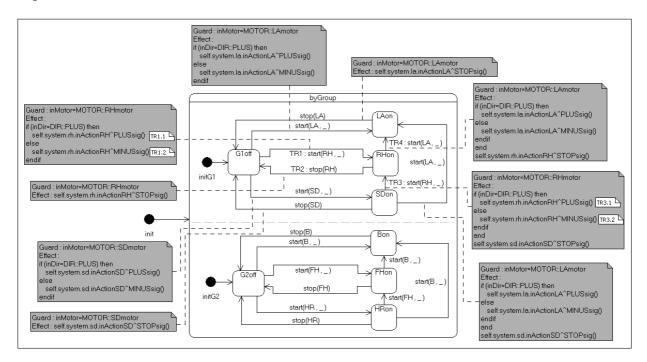

|            | 6.2.1  | Modèle                                    | . 138 |

|            | 6.2.2  | Génération de tests                       | . 144 |

|            | 6.2.3  | Bilan                                     | . 146 |

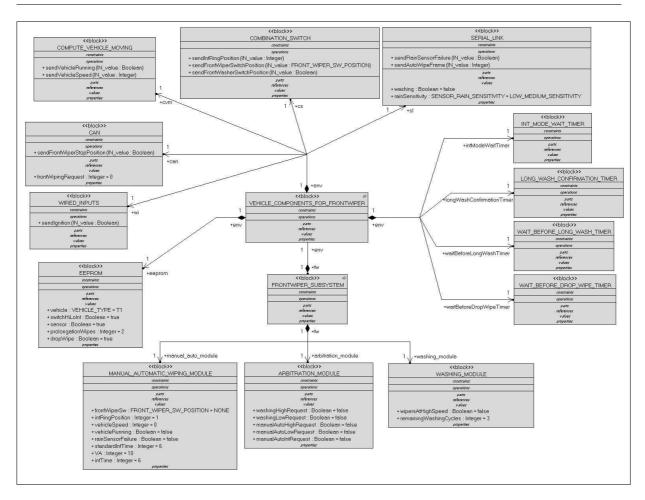

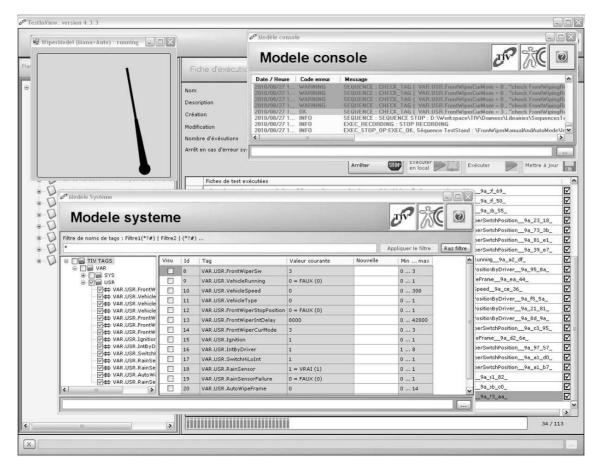

| 6.3        | Essuie | e-glace avant d'un véhicule               | . 147 |

|            | 6.3.1  | Modèle                                    | . 147 |

|            | 6.3.2  | Génération de tests sur le modèle SysML   | . 148 |

|            | 6.3.3  | Génération de tests Test Designer $^{TM}$ | . 149 |

|            | 6.3.4  | Publication et exécution des tests        | . 150 |

|            | 6.3.5  | Bilan                                     | . 150 |

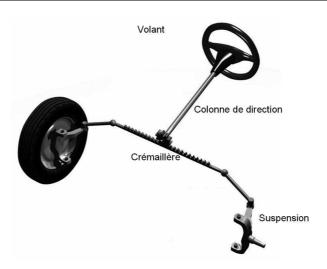

| 6.4        | Colon  | ne de direction d'un véhicule             | . 151 |

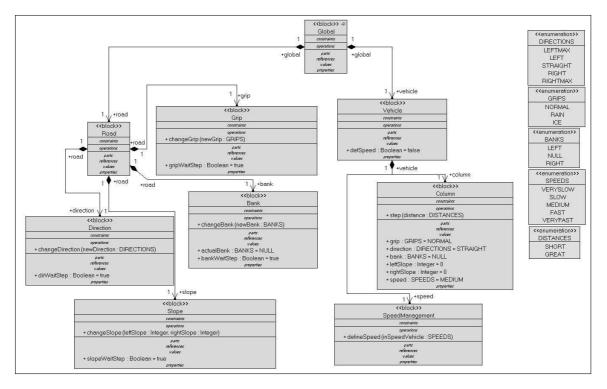

|            | 6.4.1  | Modèle                                    | . 152 |

|            | 6.4.2  | Génération de tests sur le modèle SysML   | . 153 |

|            | 6.4.3  | Génération de tests Test Designer $^{TM}$ | . 153 |

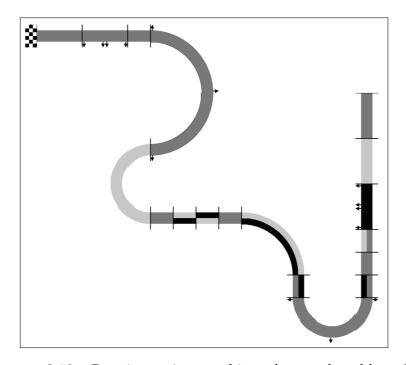

|            | 6.4.4  | Publication et exécution des tests        | . 154 |

|            | 6.4.5  | Bilan                                     | . 159 |

| 6.5        | Synth  | èse                                       | . 159 |

|            |        |                                           |       |

| Conclusi   | ons e  | t perspectives                            | 163   |

| Bibliogran | hie    |                                           | 169   |

# Table des figures

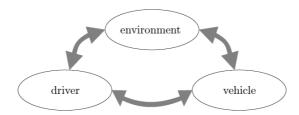

| 2.1  | Triplet de modélisation des systèmes embarqués véhicule                | 25       |

|------|------------------------------------------------------------------------|----------|

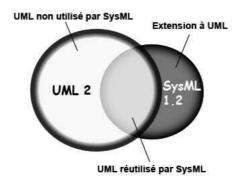

| 3.1  | Recouvrement des langages SysML et UML2                                | 38       |

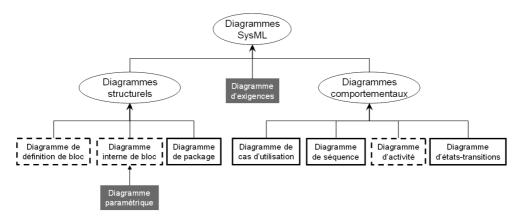

| 3.2  | Diagrammes SysML et liens avec UML                                     | 39       |

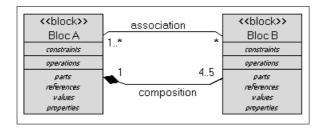

| 3.3  | Représentation graphique d'un bloc SysML4MBT                           | 43       |

| 3.4  |                                                                        | 44       |

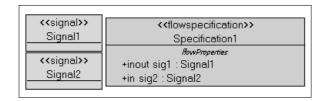

| 3.5  | Représentation graphique d'un signal SysML4MBT                         | 45       |

| 3.6  | Représentation graphique d'une spécification de flux SysML4MBT         | 45       |

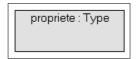

| 3.7  | Représentation graphique d'une propriété du diagramme interne de bloc  |          |

|      | SysML4MBT                                                              | 46       |

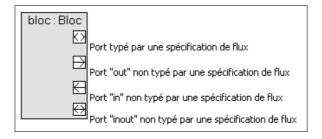

| 3.8  | Représentation graphique des ports du diagramme interne SysML4MBT      | 46       |

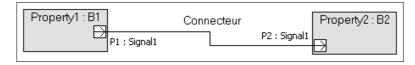

| 3.9  |                                                                        | 47       |

| 3.10 | ı                                                                      | 47       |

| 3.11 |                                                                        | 47       |

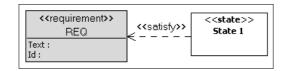

|      |                                                                        | 50       |

|      |                                                                        | 50       |

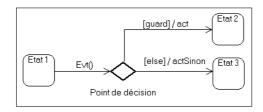

|      | · · · · · · · · · · · · · · · · · · ·                                  | 51       |

|      |                                                                        | 53       |

|      |                                                                        | 54       |

|      |                                                                        | 55       |

|      |                                                                        | 55       |

|      |                                                                        | 65       |

|      |                                                                        | 66       |

|      |                                                                        | 67       |

|      | y 1                                                                    | 67       |

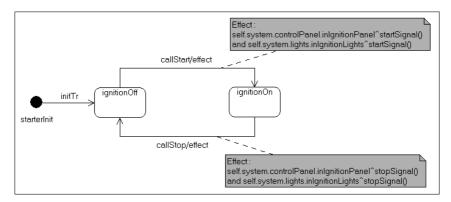

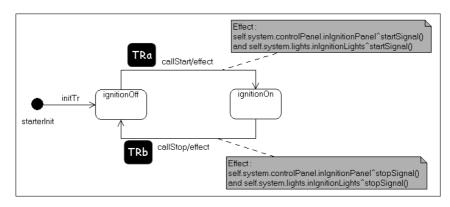

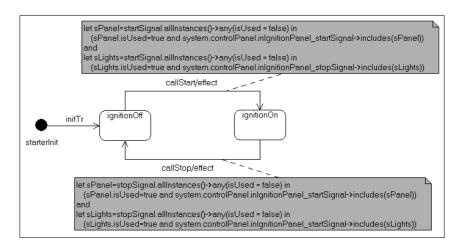

| 3.23 | Diagramme d'états-transitions du bloc Ignition du modèle SysML4MBT     |          |

|      | 1                                                                      | 68       |

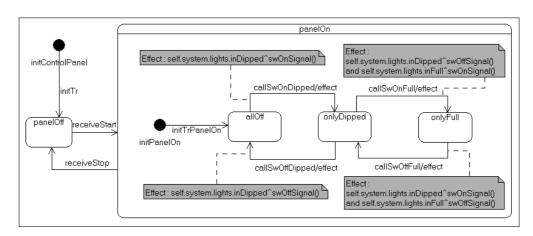

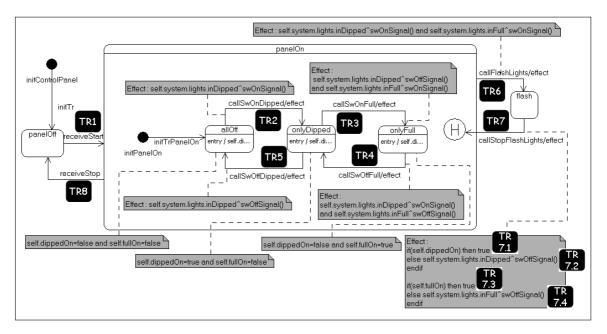

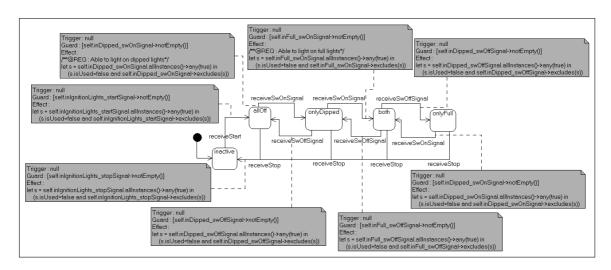

| 3.24 | Diagramme d'états-transitions du bloc ControlPanel du modèle SysML4MBT |          |

|      | r                                                                      | 69       |

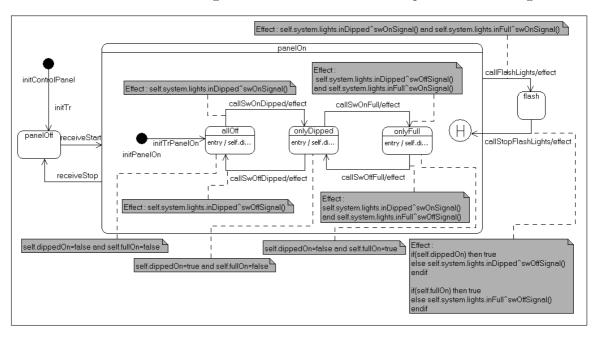

|      | v 1                                                                    | 70       |

| 3.26 | Diagramme d'états-transitions du bloc ControlPanel du modèle SysML4MBT |          |

| 0.07 | 1 9                                                                    | 71       |

| 3.27 | Diagramme d'états-transitions du bloc Lights du modèle SysML4MBT de    | 70       |

| 2.00 |                                                                        | 72<br>72 |

| 5.28 | Diagramme d'exigences du modèle SysML4MBT de l'exemple fil rouge       | 73       |

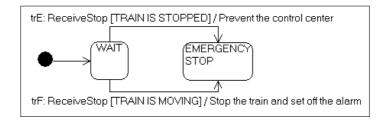

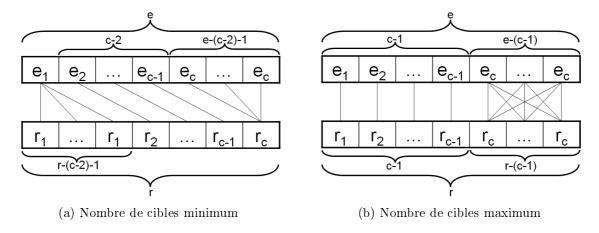

| 4.1                                                                                                  | Hiérarchie des critères de couverture                                                                                                                                                                                                              | 76                                                                   |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

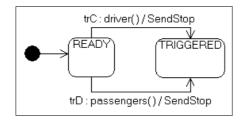

| 4.2                                                                                                  | Diagramme d'états-transitions de l'état général du train                                                                                                                                                                                           | 78                                                                   |

| 4.3                                                                                                  | Diagramme d'états-transitions des boutons d'arrêt d'urgence du train                                                                                                                                                                               | 79                                                                   |

| 4.4                                                                                                  | Diagramme d'états-transitions du gestionnaire d'arrêt d'urgence du train .                                                                                                                                                                         | 79                                                                   |

| 4.5                                                                                                  |                                                                                                                                                                                                                                                    | 80                                                                   |

| 4.6                                                                                                  | Formalisation du critère <i>Toutes les transitions</i>                                                                                                                                                                                             | 80                                                                   |

| 4.7                                                                                                  |                                                                                                                                                                                                                                                    | 81                                                                   |

| 4.8                                                                                                  |                                                                                                                                                                                                                                                    | 82                                                                   |

| 4.9                                                                                                  | Hiérarchie des critères de couverture des modèles SysML4MBT                                                                                                                                                                                        | 84                                                                   |

| 4.10                                                                                                 |                                                                                                                                                                                                                                                    | 85                                                                   |

|                                                                                                      |                                                                                                                                                                                                                                                    | 86                                                                   |

|                                                                                                      |                                                                                                                                                                                                                                                    | 86                                                                   |

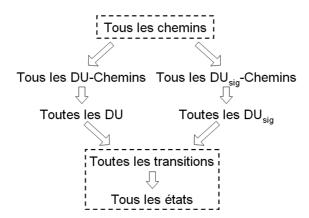

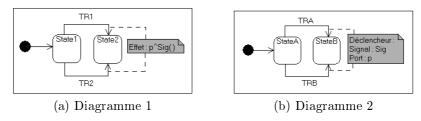

|                                                                                                      |                                                                                                                                                                                                                                                    | 88                                                                   |

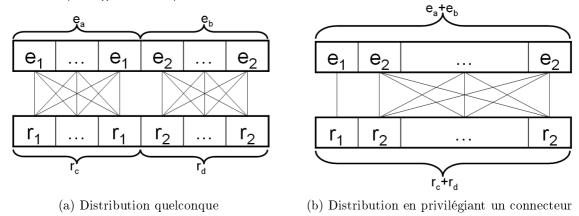

|                                                                                                      | Distribution des envois/réceptions de signaux sur deux connecteurs pour                                                                                                                                                                            |                                                                      |

|                                                                                                      |                                                                                                                                                                                                                                                    | 89                                                                   |

| 4.15                                                                                                 | Diagramme interne de bloc du modèle SysML4MBT de l'exemple fil rouge                                                                                                                                                                               | 93                                                                   |

| 4.16                                                                                                 | Diagramme d'états-transitions du bloc Ignition du modèle SysML4MBT                                                                                                                                                                                 |                                                                      |

|                                                                                                      | de l'exemple fil rouge                                                                                                                                                                                                                             | 93                                                                   |

| 4.17                                                                                                 | $Diagramme\ d'\'etats\text{-}transitions\ du\ bloc\ {\tt ControlPanel}\ du\ mod\`ele\ SysML4MBT$                                                                                                                                                   |                                                                      |

|                                                                                                      | 1                                                                                                                                                                                                                                                  | 93                                                                   |

| 4.18                                                                                                 | Diagramme d'états-transitions du bloc Lights du modèle SysML4MBT de                                                                                                                                                                                |                                                                      |

|                                                                                                      | l'exemple fil rouge                                                                                                                                                                                                                                | 94                                                                   |

|                                                                                                      |                                                                                                                                                                                                                                                    |                                                                      |

| 5.1                                                                                                  | Transformation des blocs SysML4MRT en classes SysML4MRT                                                                                                                                                                                            | <u>በ</u> 4                                                           |

| 5.1<br>5.2                                                                                           | Transformation des blocs SysML4MBT en classes SysML4MBT                                                                                                                                                                                            |                                                                      |

| 5.2                                                                                                  | Transformation des signaux SysML4MBT en classes UML4MBT 1                                                                                                                                                                                          | 05                                                                   |

| 5.2<br>5.3                                                                                           | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06                                                             |

| 5.2<br>5.3<br>5.4                                                                                    | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07                                                       |

| 5.2<br>5.3<br>5.4<br>5.5                                                                             | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07                                                 |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                      | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07                                                 |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                               | Transformation des signaux SysML4MBT en classes UML4MBT 19 Transformation des ports SysML4MBT en associations UML4MBT 19 Transformation d'un envoi de signal SysML4MBT en UML4MBT 19 Transformation d'une réception de signal SysML4MBT en UML4MBT | 05<br>06<br>07<br>07<br>09                                           |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                                        | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>09                                     |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                 | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>10                                     |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                         | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>10<br>12                               |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                 | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>09<br>10<br>12<br>13                   |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12                         | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>10<br>12<br>13<br>14<br>15             |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12                         | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>10<br>13<br>14<br>15<br>3 T            |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                 | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>09<br>09<br>12<br>13<br>14<br>15<br>3 T            |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                 | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>09<br>09<br>12<br>13<br>14<br>15<br>3 T            |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                 | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>10<br>12<br>13<br>14<br>15<br>17       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                 | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>10<br>12<br>13<br>14<br>15<br>17       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                 | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>10<br>12<br>13<br>14<br>15<br>3T<br>17 |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15 | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>10<br>12<br>13<br>14<br>15<br>3T<br>17 |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15 | Transformation des signaux SysML4MBT en classes UML4MBT                                                                                                                                                                                            | 05<br>06<br>07<br>07<br>09<br>10<br>13<br>14<br>15<br>3T<br>17<br>18 |

| 5.19 | Diagramme d'états-transitions du panneau de contrôle numéroté pour la réécriture de l'état historique | 122 |

|------|-------------------------------------------------------------------------------------------------------|-----|

| 5.20 | Diagramme d'états-transitions du panneau de contrôle après réécriture de                              |     |

| 9.20 | l'état historique                                                                                     | 123 |

| 5.21 | Diagramme d'états-transitions du panneau de contrôle après réécriture de                              |     |

|      | l'état composite                                                                                      | 123 |

| 5.22 | Diagramme d'états-transitions du démarreur après réécriture                                           |     |

|      | Diagramme d'états-transitions des lumières après réécriture                                           |     |

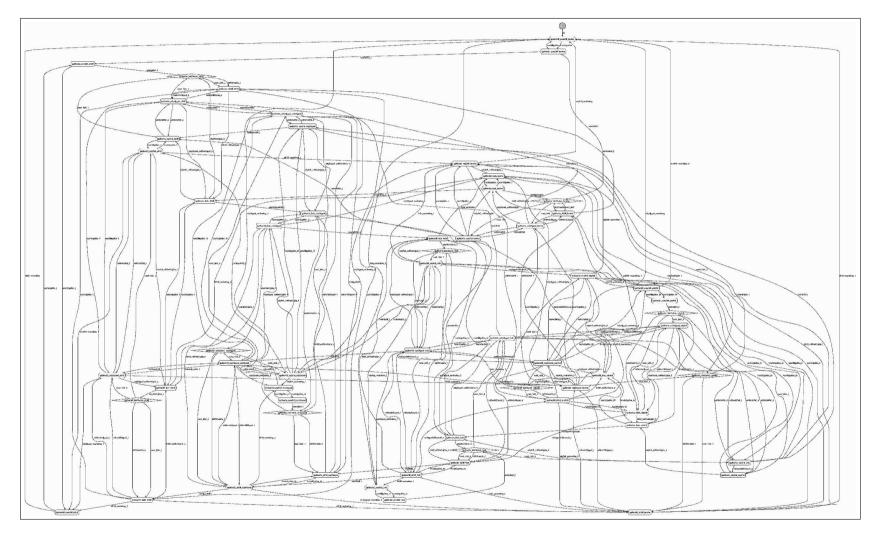

|      | Diagramme d'états-transitions résultant de la fusion des diagrammes des                               |     |

|      | figures 5.21, 5.22 et 5.23                                                                            | 125 |

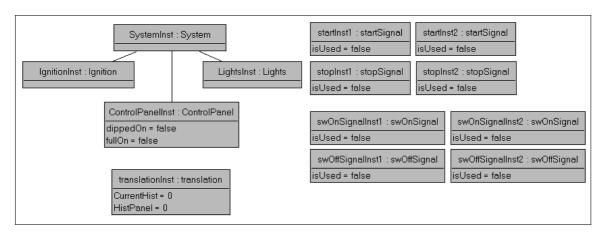

| 5.25 | Diagramme d'objets du modèle UML4MBT de l'exemple fil rouge                                           | 126 |

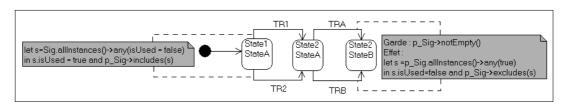

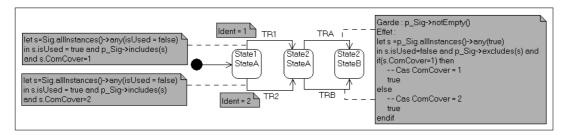

| 5.26 | Exemple de diagrammes d'états-transitions SysML4MBT                                                   | 127 |

| 5.27 | Diagramme d'états-transitions UML4MBT résultant de la réécriture des                                  |     |

|      | diagrammes de la figure 5.26                                                                          | 127 |

| 5.28 | Comparaison des tests générés avant et après transformation                                           | 127 |

| 5.29 | Diagramme d'états-transitions UML4MBT résultant de la réécriture sur-                                 |     |

|      | chargée pour Com<br>Cover des diagrammes des figures $5.26a$ et<br>$5.26b$                            | 128 |

| 5.30 | Plugin Topcased                                                                                       | 129 |

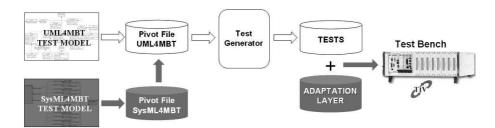

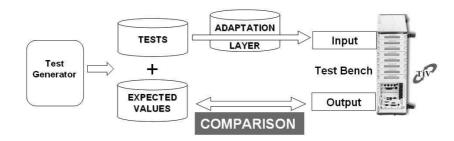

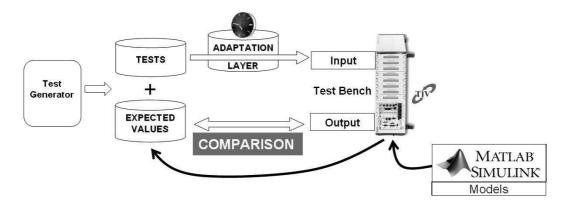

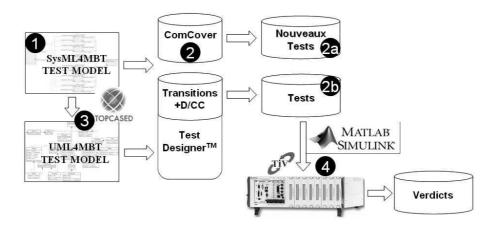

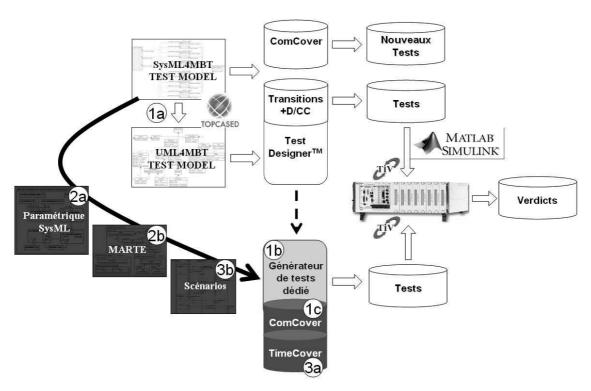

| 6.1  | Chaîne outillée VETESS                                                                                | 133 |

| 6.2  | Usage de la chaîne outillée VETESS pour les systèmes discrets                                         | 135 |

| 6.3  | Usage de la chaîne outillée VETESS pour les systèmes continus                                         | 136 |

| 6.4  | Schéma représentant le contrôle de siège                                                              | 137 |

| 6.5  | Diagramme d'exigences de contrôle de siège                                                            | 139 |

| 6.6  | Diagramme de bloc du contrôle de siège                                                                | 140 |

| 6.7  | Signaux et spécification de flux du diagramme de bloc du contrôle de siège                            |     |

| 6.8  | Diagramme interne de bloc du contrôle de siège                                                        | 142 |

| 6.9  | Diagramme d'états-transitions du bloc Command du contrôle de siège                                    | 142 |

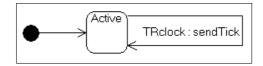

| 6.10 | Diagramme d'états-transitions du bloc Clock du contrôle de siège                                      | 143 |

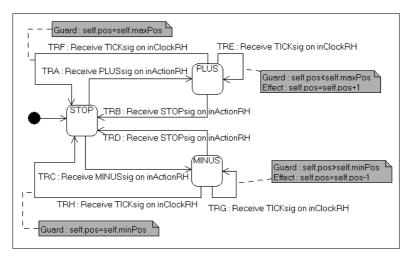

| 6.11 | Diagramme d'états-transitions du bloc RH du contrôle de siège                                         | 143 |

|      | Diagramme de bloc de FrontWiper                                                                       |     |

| 6.13 | Exécution des tests sur le modèle de simulation des essuie-glace                                      | 151 |

|      | Représentation schématique de la colonne de direction d'un véhicule                                   |     |

|      | Diagramme de bloc de la colonne de direction                                                          |     |

|      | Représentation graphique du test du tableau 6.4                                                       |     |

|      | Calculs concrets de la pente et du dévers pour la colonne de direction                                |     |

|      | Exemple de vecteur pour le cas de la colonne de direction                                             |     |

|      | Version simulée de la colonne de direction                                                            |     |

|      | Banc de test physique de la colonne de direction                                                      | 158 |

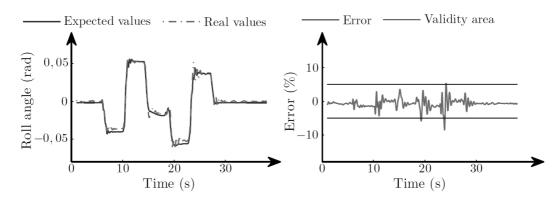

| 6.21 | Comparaison entre les valeurs attendues et les valeurs obtenues au niveau                             |     |

|      | du roulis                                                                                             |     |

|      | Chaîne outillée issue de nos travaux                                                                  |     |

| 6.23 | Perspectives de nos travaux                                                                           | 166 |

# Liste des tableaux

| SysML4MBT - Diagramme de bloc                                                                                        | 7                             |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------|

|                                                                                                                      | 7                             |

|                                                                                                                      | 8                             |

|                                                                                                                      | 8                             |

| Tests générés par la stratégie $Toutes$ $les$ $transitions + D/CC$ sur l'exemple                                     |                               |

| jouet                                                                                                                | 3                             |

| Tests générés par ComCover sur l'exemple jouet                                                                       | 1                             |

| Tests générés par la stratégie $\mathit{Toutes}$ les $\mathit{transitions} + \mathrm{D/CC}$ sur l'exemple            |                               |

| fil rouge                                                                                                            | 5                             |

| Tests générés par la stratégie ComCover sur l'exemple fil rouge 9                                                    | 6                             |

| Tests générés par la stratégie $Toutes$ les $transitions+D/CC$ sur l'exemple présenté sur la figure $5.29$           | 9                             |

| Tests générés par la stratégie $\mathit{Toutes}$ $\mathit{les}$ $\mathit{transitions} + \mathrm{D/CC}$ sur le cas du |                               |

| contrôle de siège                                                                                                    | 5                             |

| Tests générés par ComCover sur le cas du contrôle de siège                                                           | 5                             |

| Tests générés par la stratégie $Toutes$ $les$ $transitions+D/CC$ sur le cas des                                      |                               |

| essuie-glace                                                                                                         | 0                             |

| Exemple de test généré pour la colonne de direction                                                                  | 5                             |

| Valeurs de concrétisation pour la colonne de direction                                                               | 6                             |

| Résultats au niveau des différents cas d'étude                                                                       | 0                             |

|                                                                                                                      | SysML4MBT - Diagramme interne |

# Première partie Contexte, problématiques et état de l'art

# Chapitre 1

## Introduction

#### Sommaire

| 1.1 | Contexte                                                  | 4  |

|-----|-----------------------------------------------------------|----|

| 1.2 | Le projet VETESS                                          | 8  |

| 1.3 | Problématiques                                            | 12 |

| 1.4 | Structure du document                                     | 13 |

| 1.5 | Exemple fil rouge : système d'éclairage avant de véhicule | 14 |

|     |                                                           |    |

Ce mémoire de thèse présente une contribution à la génération de tests à partir de modèles pour la validation fonctionnelle des systèmes embarqués mis en œuvre dans le contexte automobile. L'objectif de ces travaux est la mise en place d'une chaîne outillée allant de la modélisation du système sous test à l'exécution des tests générés sur un banc de test. Dans ce contexte, la contribution des travaux présentés dans ce document se situe plus particulièrement au niveau de la définition d'un langage de modélisation adapté aux systèmes embarqués et à la définition de stratégies de génération de tests. L'implémentation des résultats théoriques obtenus a permis d'évaluer leur pertinence dans un contexte opérationnel, offrant l'assurance d'une qualité optimale de ce type de systèmes.

Ce chapitre présente le contexte et les objectifs de ces travaux ainsi que les éléments permettant de répondre aux problématiques soulevées. La section 1.1 présente le contexte général de ces travaux. La section 1.2 présente le projet VETESS, cadre dans lequel nos travaux se sont déroulés. La section 1.3 introduit les problématiques inhérentes à la mise en place d'un tel processus et la section 1.4 présente le plan de ce mémoire. Enfin, la section 1.5 décrit l'exemple fil rouge utilisé tout au long de ce document afin d'illustrer nos travaux.

#### 1.1 Contexte

Un système embarqué est un système électronique, piloté par un logiciel, qui est complètement intégré au système qu'il contrôle. Lorsque ce système comporte également une partie mécanique, on parle de système mécatronique [GB03]. Un des premiers systèmes modernes embarqués reconnaissables a été le système de guidage des missions lunaires du programme Apollo (AGC pour Apollo Guidance Computer) [Tom88]. De nos jours, les systèmes embarqués sont présents dans des domaines de plus en plus nombreux et variés tels que l'automobile, l'aéronautique, les télécommunications, le médical... En 2008, une étude du groupe VDC research <sup>1</sup> [VDC08] a évalué la taille du marché de l'embarqué à 46,8 M\$ avec une croissance de 20% pour la période 2007-2010, ce qui permettait d'estimer ce marché début 2012 à 100 M\$, en supposant que ce taux de croissance se soit maintenu en 2011. La complexité grandissante des systèmes embarqués, combinée aux contraintes constantes de qualité et aux délais de commercialisation de plus en plus courts, nécessite la mise en place de techniques toujours plus efficaces permettant de garantir la qualité du produit.

De nos jours, les véhicules contiennent un nombre élevé de systèmes embarqués. Les véhicules les plus complets peuvent contenir jusqu'à 70 ECU (unité électronique de contrôle). Chaque ECU est composée d'une couche physique et de plusieurs couches de logiciels embarqués. Les systèmes embarqués étant de plus en plus présents, de nouvelles normes ont été mises en place. La norme 26262 [26211], adaptée de la norme CEI 61508 [61510] sur la sécurité fonctionnelle, s'intéresse par exemple à la sécurité fonctionnelle des véhicules routiers. Cette norme décrit, entre autres, les étapes nécessaires au test pour garantir la conformité de ce type de systèmes tels que : inspection du code source, inspection du modèle, couverture de code, test basé sur les exigences...

Afin de pouvoir garantir la qualité d'un système, il faut connaître les exigences auxquelles le système doit répondre. Elles sont regroupées en deux grandes catégories. La première regroupe les exigences fonctionnelles. Elles décrivent les fonctionnalités du système et leurs caractéristiques : en d'autres mots, ce que le système doit être capable de faire. La seconde regroupe les exigences non fonctionnelles. Il s'agit des propriétés définissant la qualité des services proposés par le système. On peut citer par exemple la sécurité, la fiabilité, la performance, la maintenabilité, la portabilité. . . Ces exigences sont plus difficilement validables car, au contraire des exigences fonctionnelles, elles ne correspondent pas toujours à un cas d'utilisation précis du système. Pour ce genre d'exigences, le processus permettant de garantir qu'elles sont respectées par le système est plus complexe

<sup>1.</sup> http://www.vdcresearch.com/

et nécessite généralement une phase d'analyse afin d'identifier le sens concret de la propriété vis-à-vis du système réel [ATF09, HTES09]. Dans la suite de ce chapitre, nous nous intéresserons uniquement aux exigences fonctionnelles.

Dans le domaine du génie logiciel, les processus permettant d'évaluer la conformité du produit vis-à-vis des exigences peut se découper en deux grandes catégories : la validation et la vérification. La norme ISO 9000 [90005], relative à la gestion de la qualité, fournit les définitions suivantes à l'égard de ces termes :

- Validation : confirmation par l'examen et la fourniture de preuves objectives que les exigences, pour un usage ou une application voulue, ont été remplies.

- Vérification : confirmation par l'examen et la fourniture de preuves objectives que des exigences spécifiées ont été remplies.

La différence se situe donc au niveau des cas dans lesquels les exigences doivent être respectées. Dans le cas de la vérification, il faut montrer que les exigences sont respectées quel que soit le cas d'utilisation. Pour ce faire, il existe deux approches principales : le *Model-Checking* et la preuve. Le *Model-Checking* [Alu11, HLC+09] est une technique consistant à explorer de manière exhaustive tous les états atteignables ou toutes les exécutions d'un modèle et de vérifier, pour chacun d'entre eux, la validité d'un ensemble de propriétés. La preuve [Lan98] consiste à prouver avec des axiomes et des règles d'inférences que des formules sont valides pour une représentation donnée du système.

Dans le cadre de nos travaux, nous nous sommes intéressés à l'activité de validation, c'est-à-dire à montrer que les exigences sont remplies dans certains cas d'utilisation spécifiques du produit fini. Il existe plusieurs techniques de validation, formelles ou semiformelles, qui sont plus ou moins aisées à mettre en place rigoureusement dans un contexte industriel. Le prototypage [AHD11] consiste à réaliser une version incomplète du système sous test afin de contrôler par exemple que les entrées/sorties sont compatibles. Cette technique est généralement utilisée pour effectuer la validation d'un système en cours de développement ou expérimenter au plus tôt la viabilité du développement. Cela permet d'obtenir rapidement une maquette permettant de valider certaines exigences afin de confirmer au plus tôt les choix de conception et d'anticiper les mauvais choix d'implémentation. La simulation [WZEK10] est une activité consistant à exécuter un programme informatique reproduisant les fonctionnalités et les réactions du système réel et à contrôler que le système réel réagit de la même manière. C'est une technique très répandue dans le domaine automobile du fait de la complexité des systèmes. En effet, cette technique permet l'exécution et la validation d'un grand nombre de séquences d'exécution en un temps restreint. Le développement de la version simulée peut cependant prendre beaucoup de temps. Cette technique peut être couplée à du Model-Checking [KEP05] afin de vérifier

que la version simulée respecte bien certaines propriétés.

La technique de validation la plus répandue dans le domaine industriel est le test [KT09]. Un test consiste à exécuter un système ou une certaine partie de ce système en lui soumettant un ensemble de stimuli choisis, et d'observer son comportement pour déterminer si celui-ci est conforme aux spécifications et aux exigences initialement définies dans son cahier des charges. Toutefois, l'inconvénient du test, comme l'a souligné Dijkstra, est qu'il peut être utilisé pour détecter les bugs, mais jamais pour montrer qu'il n'y en a pas [Dij70]. En effet, l'explosion combinatoire couplée à l'infinité de scénarios potentiels empêche généralement de tester un logiciel de manière exhaustive. Le test participe donc à augmenter le niveau de confiance dans le logiciel lorsqu'aucun défaut ne se manifeste, tout en rendant possible la maîtrise des coûts de validation : la phase de test peut être interrompue à tout instant sans remettre en cause les résultats déjà obtenus. Le test est une activité primordiale pour l'obtention de logiciels fiables et c'est actuellement la principale technique utilisée dans le monde industriel pour certifier de la qualité d'un logiciel.

Le test permet aux entreprises de réaliser des économies substantielles s'il est correctement mis en œuvre. En effet, en 2002, une étude de l'Institut National (américain) des Normes et des Technologies (le NIST, National Institute of Standards and Technology) a montré que chaque année, 59.5 milliard de dollars américains sont perdus aux Etats-Unis à cause de problèmes de qualité au sein des applications logicielles et des systèmes embarqués. Ces problèmes tels que des produits qui ne correspondent pas aux besoins fonctionnels ou commerciaux, des erreurs, des interruptions de services, engendrent parfois de lourdes pertes financières [Tas02]. Par exemple, le 4 juin 1996, la fusée Ariane 5 a été détruite en plein vol, du fait d'un problème logiciel, engendrant une perte financière de plus d'un milliard de francs [Dow97, Nus97]. Cet événement a mis en lumière le manque de validation des systèmes embarqués. Cet incident n'a heureusement pas provoqué de perte humaine mais ce n'est pas toujours le cas. Citons l'exemple des défibrillateurs en libre service affichant un message d'erreur et empêchant leur fonctionnement au moment crucial [Har12]. Les systèmes embarqués sont des systèmes particulièrement complexes du fait de la combinaison de parties matérielles et logicielles. Les bugs sont parfois d'origines multiples et peuvent avoir des conséquences complexes comme dans l'exemple du vol 72 de la compagnie aérienne australienne Qantas qui a effectué de violents piqués à cause d'un problème d'origine combiné mécanique et logiciel [Qan08].

Ces différents incidents créent encore aujourd'hui un fort besoin pour le développement de nouvelles techniques de génération de tests. Cependant, dans le contexte du développement logiciel, le test est souvent mal perçu pour les raisons suivantes :

- C'est une variable d'ajustement : dans la dynamique d'un projet où les exigences au niveau des délais de livraison sont strictes, les phases de test sont souvent repoussées en fin de processus, lorsqu'il n'est plus possible d'attendre.

- C'est une punition : les équipes responsables de la phase de test sont souvent nommées par défaut et manquent souvent de connaissances et de compétences dédiées.

- Cela perturbe le développement : lorsque des dysfonctionnements sont signalés à l'équipe de développement, elle dépense un pourcentage croissant de son temps à corriger ces anomalies.

- Les délais sont variables : on ne peut pas prédire la fin et le résultat d'une phase de test. Est-ce que toutes les parties de l'application vont-être couvertes? Est-ce suffisant?

Ainsi, afin que cette tâche ait meilleure réputation et soit la plus efficace possible, il est nécessaire de définir des stratégies et des processus, adaptés à chaque situation, afin que chaque application/système puisse être testée avec un investissement contrôlable, une performance optimale, et des délais tenus. Des techniques de gestion de projet dites agiles [BBvB+01] (SCRUM, XP...) existent également afin de faciliter l'intégration des phases de test au sein du développement.

De façon générale, les techniques de test peuvent être répertoriées en plusieurs catégories suivant différents critères. Tout d'abord, en terme de visibilité du système, on discerne deux catégories. On parle de test boîte blanche lorsque que l'on accède et que l'on prend en compte le fonctionnement interne du système pour déterminer la suite de stimuli à exercer. C'est le cas lorsque l'on souhaite valider directement le code même du logiciel. Le test boîte blanche est généralement réalisé au cours du développement. En revanche, si l'on considère le système dans sa globalité, on parlera de test boîte noire. Dans ce cas, les seuls éléments pris en compte pour générer les tests sont les accesseurs disponibles à un niveau utilisateur du système. On parle parfois de test boîte grise lorsque l'on se positionne à un niveau global en ayant tout de même accès à certains éléments de fonctionnement interne. Idéalement, le test boîte blanche et le test boîte noire coexistent au sein d'un même projet [MSBT04]. Dans notre cas, nous nous intéressons au test boîte noire car notre but est de tester le produit fini, dans sa globalité.

On distingue également une classification des tests en fonction des quatre niveaux suivants. Le test de *composant* ou *unitaire* s'intéresse à la validation d'une portion de programme. Il s'agit d'une phase de test généralement réalisée au cours du développement afin de vérifier que chaque partie est correctement construite indépendamment des autres. Les tests d'intégration permettent de valider la mise en commun des différentes parties développées. Les tests système permettent de valider la globalité du système vis-à-vis des

exigences. Enfin, le test de *recette* correspond à l'étape durant laquelle le client valide le produit livré. Nos travaux se positionnent au niveau du test *système* permettant de valider le système dans sa globalité.

Les techniques de génération de tests sont nombreuses. Celles qui nous intéressent consistent à générer des tests à partir d'un modèle abstrait représentant le système sous test. Les réactions du système et du modèle sont alors comparées lors de l'exécution des tests. Mais la génération de tests peut se baser sur d'autres procédés comme l'utilisation de scénarios [AMS06] ou sur des techniques de vérification comme le Model-Checking [HLM+08, CSE96, FMS09a]. Les travaux présentés dans ce mémoire ont été réalisés dans le cadre du projet VETESS présenté dans la prochaine section.

## 1.2 Le projet VETESS

VETESS (vérification de systèmes embarqués VEhicules par génération automatique de TESts à partir des Spécifications) est un projet labellisé par le pôle de compétitivité Véhicule du Futur, financé par le FUI (Fonds Unique Interministériel), qui s'est déroulé du 1<sup>er</sup> septembre 2008 au 31 août 2010 [VET10a]. L'objectif stratégique du projet VETESS a été de produire des outils conceptuels, méthodologiques et techniques pour la vérification de systèmes mécatroniques embarqués dans les véhicules par génération automatique de tests à partir des spécifications.

Le projet VETESS s'inscrit dans le contexte de la montée en puissance de l'ingénierie dirigée par les modèles pour la conception de systèmes embarqués dans les véhicules. Il s'agit là d'un enjeu stratégique pour l'industrie automobile afin de maîtriser la fiabilité de systèmes embarqués de plus en plus complexes, mais aussi pour raccourcir le délai de la mise sur le marché des nouveaux modèles et de maîtriser les coûts de conception. L'ingénierie dirigée par les modèles constitue la colonne vertébrale de cette démarche continue et la génération de tests à partir des modèles un moyen pour garantir cette continuité. La chaîne outillée part de modèles représentant le fonctionnement attendu du système sous test et produit des tests exécutables sur les bancs de test dédiés à cette fonction. Les problématiques globales résolues par ce projet concernent l'optimisation des coûts et l'attestation de la fiabilité de systèmes mécatroniques complexes, en s'appuyant sur une continuité, basée sur les modèles, entre les phases de conception et les phases de qualification des équipements et des organes.

Pour remplir ces objectifs, le projet VETESS s'appuie sur un partenariat fortement complémentaire avec une expertise importante dans l'ingénierie dirigée par les modèles et la génération automatique de tests. Ce projet a regroupé les acteurs suivants :

- Smartesting, leader du projet, est une société basée à Besançon (Franche-Comté) qui développe et commercialise un logiciel de génération de tests à partir de modèles (Test Designer TM) reconnu entre autres dans le domaine des technologies de l'information.

- Clemessy, société basée à Mulhouse (Alsace), spécialisée dans le domaine de l'embarqué automobile, propose notamment la mise en place de bancs de test pour la validation de systèmes. La solution proposée par cette société contient une plateforme d'exécution de tests baptisée Test In View (TIV).

- Le laboratoire MIPS (Modélisation, Intelligence, Pocessus et Systèmes) de l'Université de Haute-Alsace est reconnu pour son expertise dans l'ingénierie dirigée par les modèles.

- Le laboratoire DISC (Département Informatique des Systèmes Complexes) de l'Université de Franche-Comté est reconnu pour son expertise dans la génération de tests à partir de modèles.

- PSA Peugeot-Citroën, constructeur automobile, a guidé nos travaux en fonction de ses besoins et a proposé les cas d'étude du projet.

Les travaux présentés dans ce mémoire de thèse correspondent majoritairement aux éléments de début du processus mis en place au cours du projet VETESS à savoir la modélisation du système sous test et la génération de tests qui y est appliquée. Les autres éléments de la chaîne (concrétisation et exécution des tests) sont brièvement introduits en fin de document. Du fait de la collaboration avec la société Smartesting, l'objectif a consisté à développer une chaîne outillée basée sur l'outil de génération de tests Test Designer  $^{TM}$  développé par cette société.

## Smartesting Test Designer $^{TM}$

La solution Smartesting propose un processus continu de génération de tests allant de la modélisation du système à la génération automatique de tests couvrant les comportements attendus du système sous test [BBC<sup>+</sup>06] en passant par la représentation des exigences fonctionnelles.

Cet objectif pose la problématique de la représentation des fonctionnalités d'une manière explicite et détaillée. Test Designer  $^{TM}$ , support logiciel de la solution Smartesting, permet de générer des cas de test à partir d'un modèle, spécifiant le système sous test, écrit avec un sous-ensemble de la notation UML baptisé UML4MBT [Sma09] (UML for Model-Based Testing). Le modèle de test doit être suffisamment complet et détaillé afin de permettre la génération de scénarios de test. L'outil Test Designer  $^{TM}$  propose de générer des tests à partir d'un tel modèle en assurant une couverture structurelle de celui-ci.

#### UML et UML4MBT

UML (Unified Modeling Language) est un langage graphique de modélisation des données et des traitements. Il résulte de la fusion de plusieurs méthodes d'analyse telles que OMT [RBP+90], OOSE [Jac92] et la méthode Booch [Boo93]. Au fil des années, UML a réussi à s'imposer et devenir le langage de modélisation objet le plus utilisé dans le monde. Il est standardisé par l'Object Management Group (OMG [OMG10]) depuis 1997; la version 2 d'UML a été adoptée par ce consortium en 2005 [RJB05]. UML est donc aujourd'hui le standard incontournable dans le domaine de la modélisation de logiciels. La notation UML 2 regroupe 13 types de diagrammes qui permettent de modéliser tout un système sous différentes vues (cas d'utilisation, logique, implémentation, processus et déploiement) [MG03]. Toutefois, chaque secteur d'activité possède ses propres règles et caractéristiques métier. Par rapport au formalisme UML standard, la notation UML laisse alors à chacun la possibilité de personnaliser les éléments de modélisation UML standards pour tenir compte de la spécificité de son domaine d'application au moyen de profils tels que SysML (System Modeling Language) [FMS09b], MARTE (Modeling and Analysis of Real-Time and Embedded Systems) [Gro07]...

Le logiciel Test Designer  $^{TM}$  utilise un sous-ensemble d'UML offrant des caractéristiques permettant la définition d'éléments de modélisation précis, nécessaires et suffisants à la représentation des comportements des systèmes d'information. Concrètement, un modèle UML4MBT utilise les 3 types de diagrammes suivants :

- Le diagramme de classes permettant de modéliser la structure statique du système sous test en décrivant une vue abstraite des entités du système (classes, attributs) et leurs dépendances (associations) ainsi que les actions proposées par le système (opérations).

- Le diagramme d'objets modélisant les objets concrets manipulés par les cas de test et l'état de ces entités dans l'état initial du système. Il s'agit d'une instanciation particulière du diagramme de classes associé. Les données de test représentées dans ce diagramme sont utilisées par l'outil Test Designer <sup>TM</sup> pour définir les valeurs d'entrée des paramètres ainsi que pour calculer les valeurs attendues. La création (resp. suppression) dynamique d'entités au sein du système est simulée par la création (resp. suppression) de liens entre les objets du modèle.

- Le diagramme d'états-transitions permettant de représenter une vue dynamique du système. Il spécifie l'effet des actions réalisées par l'utilisateur et par les composants extérieurs au système en terme de modifications des valeurs d'attributs des entités.

Le modèle de test représente de ce fait les comportements attendus des différentes actions qui impactent le système sous test.

La représentation dynamique est complétée par des contraintes OCL (Object Constraint Language) afin de formaliser les comportements attendus permettant une modélisation non ambigüe [BBH02, SIAB11].

#### OCL et OCL4MBT

OCL est un langage de modélisation orienté objet défini comme un standard ajouté à la notation UML et géré par l'OMG (*Object Management Group*). OCL sert généralement à préciser de manière formelle les comportements du système. Il permet d'exprimer des aspects essentiels qui ne peuvent pas être exprimés uniquement à l'aide de diagrammes. C'est pour cela que la combinaison d'OCL et d'UML est connue comme une solution appropriée à la modélisation des fonctionnalités d'un système.

Dans le cadre de l'outil Test Designer  $^{TM}$ , un sous-ensemble d'OCL (OCL4MBT pour OCL for Model-Based Testing) est utilisé. Cet ensemble apparaît comme suffisant pour la modélisation de comportements fonctionnels du système sous test. Les expressions OCL sont utilisées au sein du modèle UML4MBT pour décrire des gardes et des effets de transition. Une garde de transition est une contrainte permettant de spécifier les conditions devant être remplies pour que cette transition soit franchissable. Il s'agit d'une expression booléenne qui doit être évaluée à vrai pour que la transition puisse être franchie. Les effets de transition décrivent les modifications des états du système à travers la mise à jour des variables du système. OCL4MBT offre la syntaxe permettant l'expression de ce type d'action. En effet, afin de pouvoir exécuter les expressions OCL4MBT dans le cadre de la génération de tests, une interprétation opérationnelle spécifique d'OCL est utilisée. L'expression OCL self.attribute=true peut être interprétée de deux manières différentes : passive ou active. Le contexte passif permet d'exprimer une contrainte sur le système sous test alors que le contexte actif permet la représentation d'un changement d'état. Dans le cadre booléen (pour une garde de transition), elle sera interprétée de manière passive (comme nativement en OCL), c'est-à-dire que self. attribute sera comparé à true et une valeur booléenne sera retournée. Cependant, dans le cadre d'un effet de transition, cette expression aura pour action l'affectation de true à la variable self.attribute.

#### Génération de tests

Le modèle UML4MBT est ainsi suffisamment précis et l'absence d'ambiguïté permet la compréhension et la manipulation automatique par le générateur de tests des comportements modélisés. Cela rend possible la simulation de l'exécution du modèle et son utilisation tel un oracle permettant la prédiction des réactions du système sous test.

Les expressions OCL associées aux diagrammes d'états-transitions ajoutent un niveau de formalisation pour la génération de tests à partir de modèles. Le modèle réalisé, définissant tous les comportements à tester du système sous test, est exporté à partir du modeleur vers le générateur de tests. Le générateur de tests propose une couverture automatique de tous les comportements du modèle sous test. Chaque test correspond à une séquence d'actions à exécuter sur le système. Un test est composé de trois parties :

- 1. mise en contexte : séquence d'activations préliminaires permettant la mise en contexte du système afin d'accéder au comportement à tester,

- 2. invocation du comportement à tester, incluant la comparaison du résultat obtenu avec l'oracle,

- 3. retour à l'état initial afin qu'un autre test puisse être joué automatiquement.

Finalement, il est possible d'exporter les tests générés vers un dépôt de tests ou vers une plateforme d'exécution des tests.

## 1.3 Problématiques

Nos travaux sont motivés par la réalisation d'une chaîne outillée originale, de par la mise en collaboration d'outils performants utilisés généralement indépendamment et de par sa facilité d'utilisation au regard de la complexité des systèmes qu'elle permet de valider. En effet, elle doit permettre l'exécution des tests générés, aussi bien sur un banc de test physique que sur un simulateur et ce, quel que soit le type de système embarqué considéré (discret ou continu).

La définition d'une chaîne outillée, de génération de tests à partir de modèle, dédiée au domaine de l'embarqué pose plusieurs problématiques originales. Tout d'abord, il est nécessaire d'utiliser un langage de modélisation adapté à de tels systèmes. En effet, les systèmes embarqués ont des caractéristiques spécifiques telles que la présence de parallélisme au niveau de l'évolution des différents composants du système ou des connections avec des composants extérieurs. La première étape consiste donc en la définition d'un langage de modélisation adapté aux systèmes que l'on veut tester.

Ensuite, il faut définir une stratégie de génération de tests adaptée aux modèles ainsi réalisés. Le but est d'obtenir, par l'application de cette stratégie, une couverture adéquate et relevante du modèle réalisé apportant l'assurance d'une qualité optimale au regard des exigences du système testé.

Finalement, un élément stratégique dans le domaine du test industriel consiste en l'automatisation du procédé afin de faire face à la taille parfois conséquente des systèmes sous tests. La stratégie mise en place se doit donc d'être automatisable en impliquant un minimum d'intervention humaine. De plus, elle doit être adaptable aux différents systèmes afin de proposer un retour sur investissement significatif.

Afin de pouvoir expérimenter et utiliser les éléments permettant de répondre à ces problématiques, ils doivent être implémentés au sein d'une chaîne outillée. Dans le cadre du projet VETESS, l'outil de génération de tests choisi est Test Designer  $^{TM}$ . Il se pose alors le problème de l'adaptation de notre processus à cet outil prenant en entrée uniquement des modèles UML4MBT et proposant une couverture spécifique de ces modèles. Nos travaux se sont placés dans une optique de preuve de concept, nécessitant ainsi la mise en place de connecteurs pour une meilleure adaptation aux outils existants.

Finalement, l'efficacité du processus mis en place est alors évaluée par l'expérimentation de cette nouvelle chaîne outillée sur plusieurs cas d'étude. Le domaine de l'embarqué automobile étant vaste, nous avons sélectionné un panel de cas d'étude représentatifs.

La prochaine section présente le plan de ce mémoire en associant chaque partie aux problématiques auxquelles elle répond.

## 1.4 Structure du document

Tout d'abord, le chapitre 2 présente les travaux de la littérature en rapport avec les principaux éléments présentés dans ce mémoire. Après un aperçu des différentes techniques de validation des systèmes embarqués, ce chapitre fait un focus sur les techniques de génération de tests à partir de modèles appliquées au domaine de l'embarqué ainsi que sur les différentes techniques de modélisation.

Le chapitre 3 présente la solution que nous proposons à la problématique de la modélisation des systèmes embarqués. En l'occurrence, ce chapitre présente le langage SysML et l'utilisation qui en est faite.

Le chapitre 4 propose une stratégie de génération de tests adaptée aux modèles réalisés permettant une couverture efficace des comportements modélisés.

Le chapitre 5 présente une solution pour l'implémentation des éléments présentés dans les sections précédentes dans une optique de preuve de concept. Cette section décrit les algorithmes et les connecteurs mis en place pour la définition d'une chaîne outillée automatisée.

Enfin, les résultats de l'application de cette chaîne outillée sur trois cas d'étude sont présentés en chapitre 6. Ce chapitre permet ainsi de montrer les points forts et les limites de notre approche.

La dernière partie de ce document conclut ces travaux et présente d'éventuelles perspectives permettant d'améliorer le processus mis en place.

L'exemple fil rouge présenté dans la section qui suit permet d'illustrer les différentes parties de ce mémoire.

# 1.5 Exemple fil rouge : système d'éclairage avant de véhicule

Afin d'illustrer l'ensemble des éléments de ce document, nous définissons dans cette partie, la spécification d'un cas d'étude fil rouge. Cet exemple est réutilisé tout au long de ce mémoire afin d'illustrer les différents points de ce travail.

Ce cas d'étude concerne le système d'éclairage avant d'un véhicule. Dans le cas d'une voiture par exemple, la majorité des modèles possède un commodo, proche du volant (généralement sur la gauche), permettant d'allumer et d'éteindre les feux et les phares. Il est également possible, à l'aide de ce commodo, de réaliser des appels de phares. Basé sur ce cas *classique*, un cas particulier où le commodo serait remplacé par un écran tactile placé sur les bords du volant est considéré. La spécification détaillée est la suivante.