Année 2011

UNIVERSITE DE CERGY PONTOISE

# THESE

Présentée pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITE DE CERGY PONTOISE

Ecole doctorale: Sciences et Ingénierie Spécialité: Génie Electrique

Par

### Imen BAHRI

# **Contribution of FPGA-based System-on-Chip controllers for embedded AC drive applications**

#### JURY

| Rapporteurs         | : | Prof. Guillaume Gateau<br>Dr. Daniel Chillet          | Université de Toulouse<br>Université de Rennes |  |

|---------------------|---|-------------------------------------------------------|------------------------------------------------|--|

| Examinateurs        |   | Prof. François Verdier<br>Prof. Ilhem Slama Belkhodja | Université de Nice<br>Université de Tunis      |  |

|                     |   | Prof. Bruno Allard                                    | Université de Lyon                             |  |

|                     |   | Mr. Régis Meuret                                      | Expert Safran Power                            |  |

| Directeur de thèse  | : | Prof. Eric Monmasson                                  | Université de Cergy Pontoise                   |  |

| <b>Co-directeur</b> | : | Dr. Mohamed El Amin Ben khelifa                       | Université de Cergy Pontoise                   |  |

Laboratoire SATIE - UCP/UMR 8029, 1 rue d'Eragny, 95031 Neuville sur Oise France

# Contribution of FPGA-based System-on-Chip controllers for embedded AC drive applications

Imen BAHRI

November 13, 2011

# Contents

| N        | omen           | clature                                                                   | iv              |

|----------|----------------|---------------------------------------------------------------------------|-----------------|

| Al       | bstra          | ct                                                                        | vi              |

| Ré       | ésum           | é                                                                         | iii             |

| Ge       | enera          | l Introduction                                                            | x               |

| 1        | Stat<br>tem    | e of art of FPGA-based System-on-Chip for embedded control sys-           | 2               |

|          |                |                                                                           |                 |

|          | 1.1            | Introduction                                                              | 2               |

|          | 1.2            | Aircraft application constraints                                          | 3               |

|          | 1.3            | Hardware architectures                                                    | 4               |

|          |                | 1.3.1 ASICs                                                               | 5               |

|          |                | 1.3.2 ASIPs                                                               | 6               |

|          |                | 1.3.3 FPGAs                                                               | 7               |

|          |                | 1.3.4 System-on-Chip $\ldots$                                             | 8               |

|          |                |                                                                           | 10              |

|          |                |                                                                           | 11              |

|          | 1.4            | FPGA-SoC design flow                                                      | 12              |

|          | 1.5            | Interest of the SoC approach for AC drive applications                    | 13              |

|          | 1.6            | Co-design methodology                                                     | 15              |

|          |                | 1.6.1 Modeling                                                            | 15              |

|          |                | 1.6.2 Partitioning                                                        | 15              |

|          |                | 1.6.3 Modeling tools for Co-design                                        | 16              |

|          | 1.7            | Proposed Co-design methodology for electrical drives                      | 16              |

|          | 1.8            | • 0 00                                                                    | 19              |

|          |                |                                                                           |                 |

| <b>2</b> | Des            | ign and validation of FPGA-based motor drive for High-Temperature         |                 |

|          | $\mathbf{env}$ | ronment                                                                   | 21              |

|          | 2.1            | Introduction                                                              | 21              |

|          | 2.2            | Application overview                                                      | 22              |

|          | 2.3            |                                                                           | $\overline{23}$ |

|          |                | 2.3.1 Control algorithm design and functional validation                  | 24              |

|          |                | 2.3.2 Architectural design and modular verification of the control archi- |                 |

|          |                | _                                                                         | 31              |

|          |                |                                                                           | 36              |

|          | 2.4            |                                                                           | 40              |

|          | 2.5            | -                                                                         | 45              |

| 3 | $\mathbf{Spe}$ | cifications and algorithm development-Time delay impact       | 47         |

|---|----------------|---------------------------------------------------------------|------------|

|   | 3.1            | Introduction                                                  | 47         |

|   | 3.2            | Specifications                                                | 47         |

|   |                | 3.2.1 Power stage                                             | 48         |

|   |                | 3.2.2 Measurement boards                                      | 49         |

|   |                | 3.2.3 Digital Control Unit                                    | 49         |

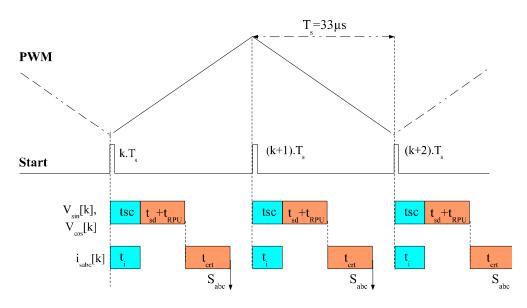

|   | 3.3            | Sources of time delay                                         | 49         |

|   |                | 3.3.1 Computation time delay                                  | 49         |

|   |                | 3.3.2 Sample-and-Hold effect of the PWM                       | 50         |

|   | 3.4            | Stator current controller                                     | 52         |

|   |                | 3.4.1 Current controller synthesis                            | 52         |

|   |                | 3.4.2 Speed controller                                        | 59         |

|   |                | 3.4.3 Rotor speed and position observer using EKF algorithm   | 60         |

|   |                | 3.4.4 Discretization and fixed-point data setting             | 64         |

|   | 3.5            | Conclusion                                                    | 66         |

| 4 | Co-            | design methodology: HW-SW partitioning                        | 68         |

| - | 4.1            | Introduction                                                  | 68         |

|   | 4.2            | First stage of experimental validation                        | <b>6</b> 9 |

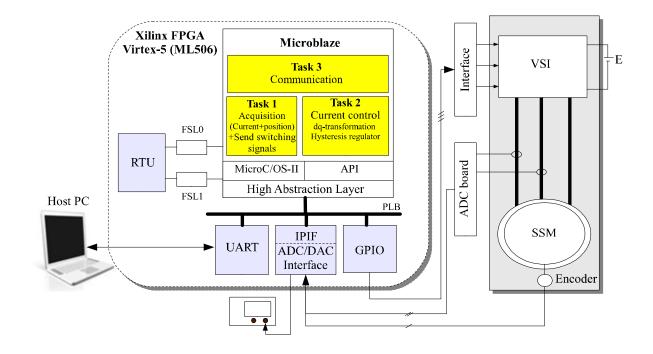

|   |                | 4.2.1 Digital platform                                        | 70         |

|   |                | 4.2.2 Overview of the experimental set up                     | 73         |

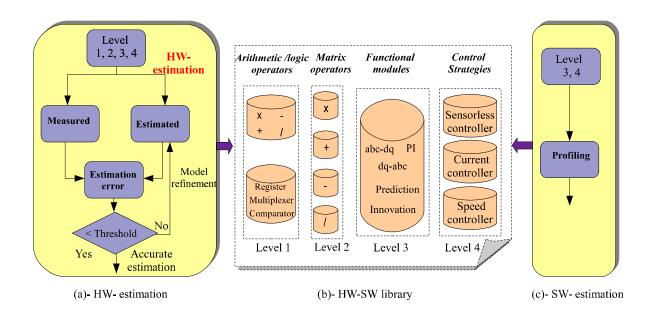

|   | 4.3            | Performance estimation                                        | 76         |

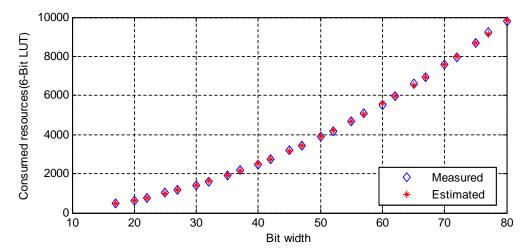

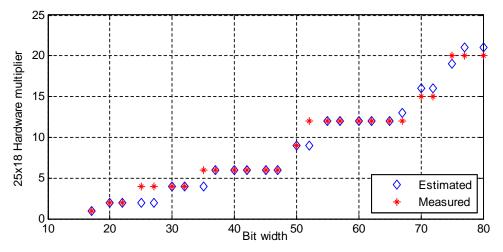

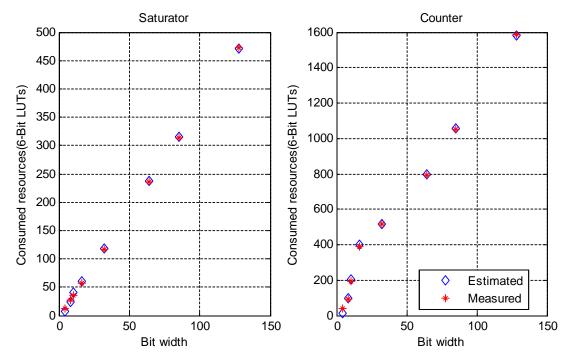

|   | 4.4            | Fine granularity library                                      | 77         |

|   | 4.5            | Medium granularity library                                    | 79         |

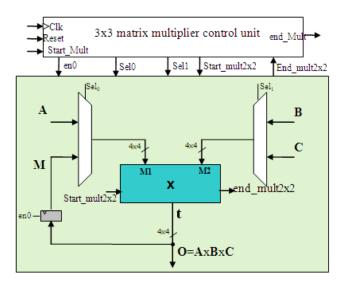

|   | 4.6            | Coarse granularity library                                    | 81         |

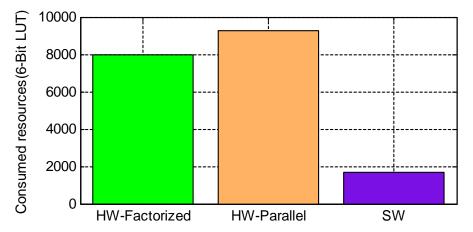

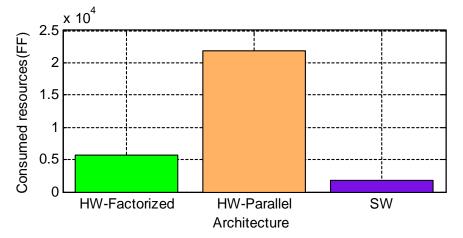

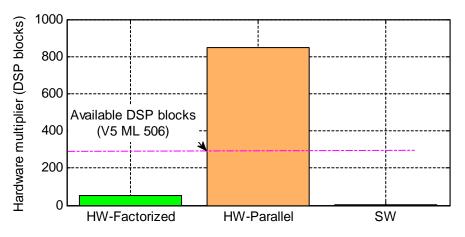

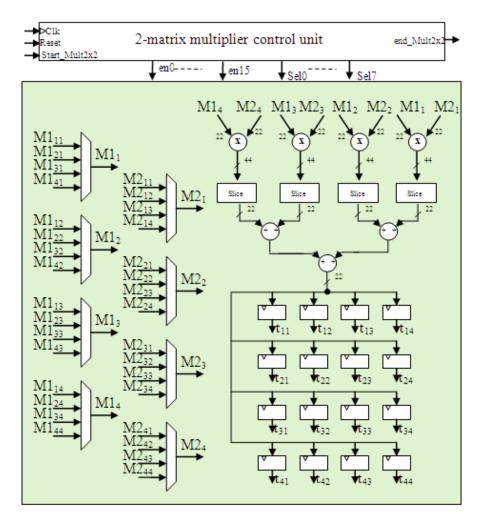

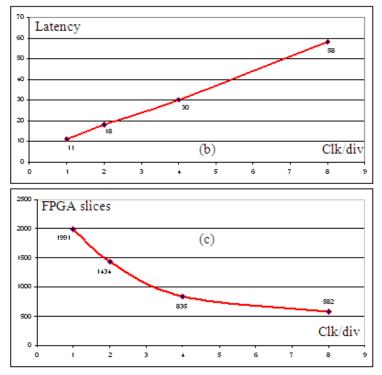

|   |                | 4.6.1 Area estimation                                         | 82         |

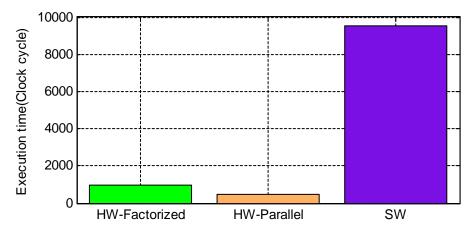

|   |                | 4.6.2 Time estimation $\ldots$                                | 84         |

|   |                | 4.6.3 Memory use                                              | 86         |

|   |                | 4.6.4 Parallelism parameter                                   | 86         |

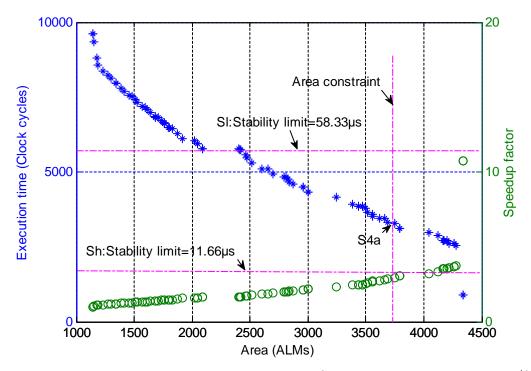

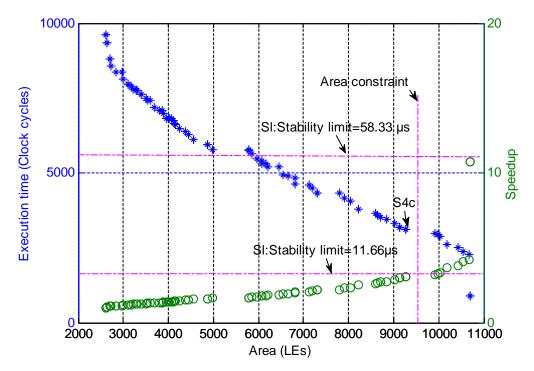

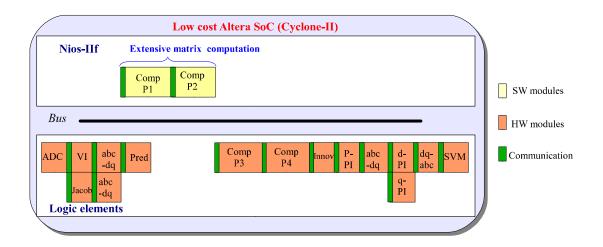

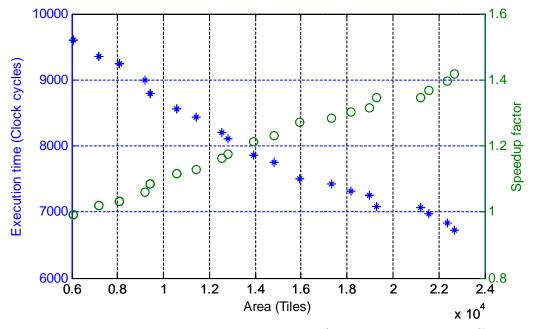

|   |                | 4.6.5 Benchmark: EKF Sensorless speed controller              | 87         |

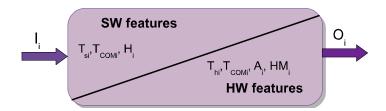

|   | 4.7            | HW-SW partitioning                                            | 92         |

|   | 4.8            | Formalization of the HW-SW partitioning problem               | 93         |

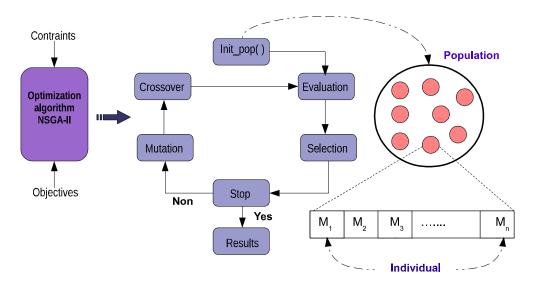

|   | 4.9            | Genetic Algorithm : NSGA-II                                   | 95         |

|   |                | 4.9.1 Principle                                               | 96         |

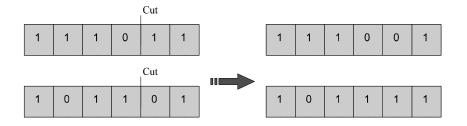

|   |                | 4.9.2 NSGA-II configuration                                   | 97         |

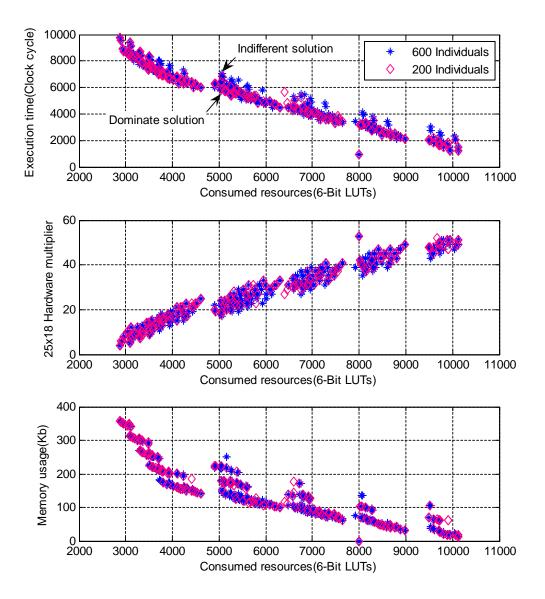

|   | 4.10           | HW-SW partitioning results                                    | 98         |

|   |                |                                                               | .09        |

| 5 | Boa            | I-Time Operating System for HW-SW controllers: Application to |            |

| 5 |                |                                                               | 11         |

|   | 5.1            | Introduction                                                  | 11         |

|   | 5.2            |                                                               | 12         |

|   | 5.3            |                                                               | 12         |

|   | 5.4            |                                                               | 14         |

|   | 5.5            |                                                               | 16         |

|   | 5.6            |                                                               | 18         |

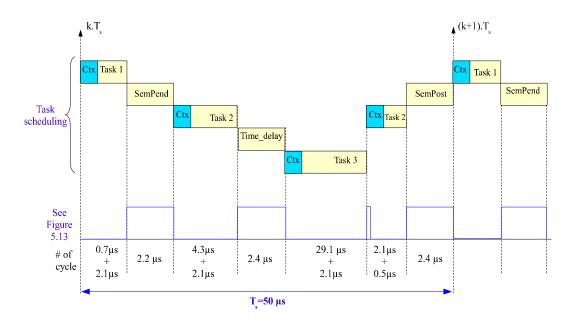

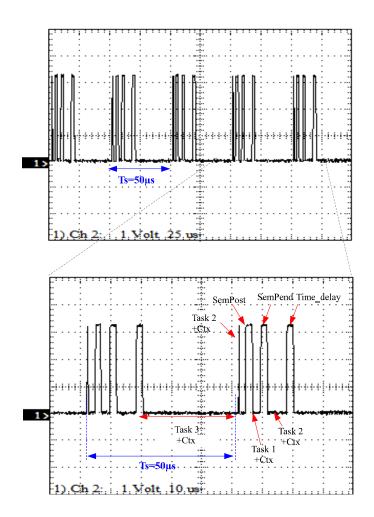

|   |                | -                                                             | 18         |

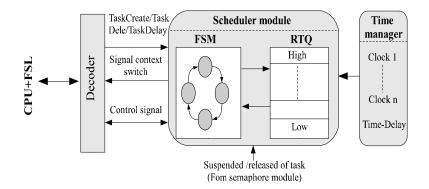

|   |                | 5.6.2 Scheduler and Time manager Modules                      | 19         |

| 6 | Gen | neral co | onclusion                  | 126   |

|---|-----|----------|----------------------------|-------|

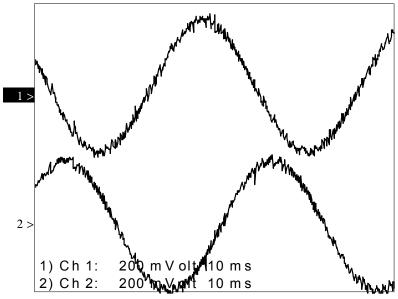

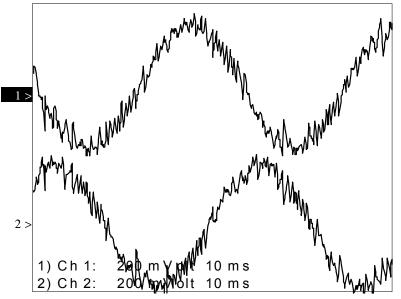

|   | 5.8 | Conclu   | usion                      | . 125 |

|   | 5.7 | Bench    | mark: motor control        | . 122 |

|   |     | 5.6.4    | Area and time performances | . 121 |

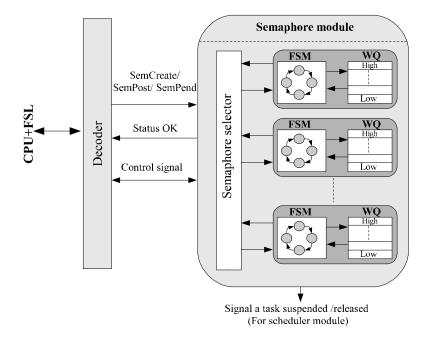

|   |     | 5.6.3    | Semaphore Manager          | . 120 |

# Nomenclature

# List of abbreviations

| $A^3$ ATO                 | : Algorithm Architecture Adequation<br>: Angle Tracking Observer |

|---------------------------|------------------------------------------------------------------|

| ADC                       | : Analog Digital Converter                                       |

| ASIP                      | : Application Specific Integrated Processor                      |

| ASIC<br>CD DWM            | : Application Specific Integrated Circuit                        |

| CB-PWM<br>CFG             | : Carrier Based Pulse Width Modulation<br>: Control Flow Graph   |

| DAC                       | : Digital Analog Converter                                       |

| DAC<br>DSP                | : Digital Signal Processor                                       |

| DSI                       | : Data Flow Graph                                                |

| EKF                       | : Extended Kalman Filter                                         |

| ECU                       | : Embedded Control Unit                                          |

| FPGA                      | : Field Programmable Gate Array                                  |

| FF                        | : Flip-Flop                                                      |

| HAL                       | : Hardware Abstraction Layer                                     |

| $\operatorname{HF}$       | : High Frequency                                                 |

| IGBT                      | : Insulated Gate Bipolar Transistor                              |

| LUT                       | : Look Up Table                                                  |

| MEA                       | : More Electrical Aircraft                                       |

| NSGA-II                   | : Non-Dominated Sorting Genetic Algorithm                        |

| PI                        | : Proportional Integral regulator                                |

| PMSM                      | : Permanent Magnet Synchronous Machine                           |

| PLB                       | : Processor Local Bus                                            |

| $\mathrm{P_{c}}$          | : Crossover rate                                                 |

| $\mathrm{P}_{\mathrm{m}}$ | : Mutation rate                                                  |

| RTOS                      | : Real Time Operating System                                     |

| $\operatorname{RTU}$      | : Real Time Unit                                                 |

| RPU                       | : Resolver Processing Unit                                       |

| SEU                       | : Single Event Upsed                                             |

| SEFORA                    | : Smart MEA For Operating in Rough Atmospheres                   |

| SPI                       | : Serial Peripheral interface                                    |

| SVM                       | : Space Vector Modulation                                        |

| VHDL                      | : Very High speed integrated Hardware Description Language       |

| VSI                       | : Volatage Source Inverter                                       |

# List of symbols

| Start      | : Start signal                                                         |

|------------|------------------------------------------------------------------------|

| $\theta$   | : Electrical position                                                  |

| $\Gamma_e$ | : Electromagnetic torque                                               |

| $\Gamma_L$ | : Load torque                                                          |

| J          | : Inertia                                                              |

| p          | : Pairs of poles of a motor                                            |

| $\omega_e$ | : Electrical speed (rad/s)                                             |

| E          | : DC link                                                              |

| R          | : Resistor                                                             |

| V          | : Voltage                                                              |

| Ι          | : Current                                                              |

| $T_s$      | : Sampling period                                                      |

| $T_{sw}$   | : Switching period                                                     |

| x          | : State space vector                                                   |

| u          | : Input vector                                                         |

| y          | : Output vector                                                        |

| w, v       | : System and measurement disturbances                                  |

| K          | : Kalman matrix                                                        |

| $P, P_0$   | : State error covariance matrix, Initial state error covariance matrix |

| Q, R       | : Covariance state noise and covariance measurement noise matrices     |

| s          | : Laplace operator                                                     |

|            |                                                                        |

# Indexes

| d-q              | : Rotating reference frame indexes   |

|------------------|--------------------------------------|

| $\alpha - \beta$ | : Stationary reference frame indexes |

| a, b, c          | : 3-phase reference frame index      |

| *                | : Reference quantity                 |

| ^                | : Estimated quantity                 |

| k                | : Sampling index                     |

| k/k-1            | : Predicted quantity                 |

k/k : Optimal estimated quantity

### Abstract

Designing embedded control systems becomes increasingly complex due to the growing of algorithm complexity, the rising of industrials requirements and the nature of application domains. One way to handle with this complexity is to design the corresponding controllers on performing powerful and open digital platforms.

More specifically, this PhD deals with the use of FPGA System-on-Chip (SoC) platforms for the implementation of complex AC drive controllers for avionic applications. These latter are characterized by stringent technical issues such as environment conditions (pressure, high temperature) and high performance requirements (high integration, flexibility and efficiency).

During this thesis, the author has contributed to design and to test a digital controller for a high temperature synchronous drive that must operate at 200°C ambient. It consists on the Flux Oriented Controller (FOC) for a Permanent Magnet Synchronous Machine (PMSM) associated with a Resolver sensor. A design and validation method has been proposed and tested using a FPGA ProAsic<sup>Plus</sup> board from Actel/Microsemi Company. The impact of the temperature on the operating frequency has been also analyzed.

A state of the art FPGA SoC technology has been also presented. A detailed description of the recent digital platforms and the constraints in link with embedded applications was investigated. Thus, the interest of a SoC-based approach for AC drives applications was also established.

Additionally and to have full advantages of a SoC based approach, an appropriate HW-SW Co-design methodology for electrical AC drive has been proposed. This method covers the whole development steps of the control application from the specifications to the final experimental validation. One of the main important steps of this method is the HW-SW partitioning. The goal is to find an optimal combination between modules to be implemented in software and those to be implemented in hardware. This multi-objective optimization problem was performed with the Non-Dominated Sorting Genetic Algorithm (NSGA-II). Thus, the Pareto-Front of optimal solution can be deduced. The illustration of the proposed Co-design methodology was made based on the sensorless speed controller using the Extended Kalman Filter (EKF). The choice of this benchmark corresponds to a major trend in embedded control of AC drives.

Besides, the management of SoC-based architecture of the embedded controller was allowed using an efficient Real-Time Operating System (RTOS). To accelerate the services of this operating system, a Real-Time Unit (RTU) was developed in VHDL and associated to the RTOS. It consists in hardware operating system that moves the scheduling and communication process from software RTOS to hardware. Thus, a significant acceleration has been achieved. The experimentation tests based on digital current controller were also carried out using a laboratory set-up. The obtained results prove the interest of the proposed approach.

# Keywords

- Field Programmable Gate Array

- AC drive controller

- Resolver sensor

- Sensorless controller

- High temperature

- System-on-Chip

- Hardware-Software Co-design

- Optimization

- Genetic algorithm

- Operating system

- Scheduler

### Résumé

La conception des systèmes de contrôle embarqués devient de plus en plus complexe en raison des algorithmes utilisés, de l'augmentation des besoins industriels et de la nature des domaines d'applications. Une façon de gérer cette complexité est de concevoir les contrôleurs correspondant en se basant sur des plateformes numériques puissantes et ouvertes.

Plus précisément, cette thèse s'intéresse à l'utilisation des plateformes FPGA Systemon-Chip (SoC) pour la mise en œuvre des algorithmes d'entraînement électrique pour des applications avioniques. Ces dernières sont caractérisées par des difficultés techniques telles que leur environnement de travail (pression, température élevée) et les exigences de performance (le haut degré d'intégration, la flexibilité).

Durant cette thèse, l'auteur a contribué à concevoir et à tester un contrôleur numérique pour un variateur de vitesse synchrone qui doit fonctionner à 200 °C de température ambiante. Il s'agit d'une commande par flux orienté (FOC) pour une Machine Synchrone à Aimants Permanents (MSAP) associée à un capteur de type résolveur. Une méthode de conception et de validation a été proposée et testée en utilisant une carte FPGA ProAsic<sup>Plus</sup> de la société Actel/Microsemi. L'impact de la température sur la fréquence de fonctionnement a également été analysé.

Un état de l'art des technologies basées sur les SoC sur FPGA a été également présenté. Une description détaillée des plateformes numériques récentes et les contraintes en lien avec les applications embarquées a été également fournie. Ainsi, l'intérêt d'une approche basée sur SoC pour des applications d'entrainements électriques a été démontré.

D'un autre coté et pour profiter pleinement des avantages offertes par les SoC, une méthodologie de Co-conception matériel-logiciel (hardware-software (HW-SW)) pour le contrôle d'entraînement électrique a été proposée. Cette méthode couvre l'ensemble des étapes de développement de l'application de contrôle à partir des spécifications jusqu'à la validation expérimentale. Une des principales étapes de cette méthode est le partitionnement HW-SW. Le but est de trouver une combinaison optimale entre les modules à mettre en œuvre dans la partie logicielle et ceux qui doivent être mis en œuvre dans la partie matérielle. Ce problème d'optimisation multi-objectif a été réalisé en utilisant l'algorithme de génétique, Non-Dominated Sorting Genetic Algorithm (NSGA-II). Ainsi, un Front de Pareto des solutions optimales peut être déduit. L'illustration de la méthodologie proposée a été effectuée en se basant sur l'exemple du régulateur de vitesse sans capteur utilisant le filtre de Kalman étendu (EKF). Le choix de cet exemple correspond à une tendance majeure dans le domaine des contrôleurs embraqués pour entrainements électriques.

Par ailleurs, la gestion de l'architecture du contrôleur embarqué basée sur une approche SoC a été effectuée en utilisant un système d'exploitation temps réel. Afin d'accélérer les services de ce système d'exploitation, une unité temps réel a été développée en VHDL et associée au système d'exploitation. Il s'agit de placer les services d'ordonnanceur et des processus de communication du système d'exploitation logiciel au matériel. Ceci a permis une accélération significative du traitement. La validation expérimentale d'un contrôleur du courant a été effectuée en utilisant un banc de test du laboratoire. Les résultats obtenus prouvent l'intérêt de l'approche proposée.

# Mots clefs

- Réseaux de portes programmables sur site Field Programmable Gate Array

- Contrôle d'entraînement électrique

- Capteur de position Resolveur

- Commande sans capteur mécanique

- Haute temperature

- Système sur puce

- Co-conception matériel-logiciel

- Optimisation

- Algorithme génétique

- Système d'exploitation

- Ordonnanceur

# **General Introduction**

During these last decades, the More-Electric Aircraft (MEA) has solicited the interest of both academic and industrial communities. The main objectives consist in increasing the scope of electrical energy sources instead of the mechanical and pneumatic ones [2], [16].

It is true that the adoption of the MEA allows numerous benefits such as the performance optimization, the decrease of maintenance costs, the reduction of  $CO_2$  gas emission and the weight gains. However, this trend comes along serious technical issues such as environment conditions (pressure, high temperature) and high performance requirements (high integration, flexibility and efficiency) [3].

In this context, this PhD thesis deals with the development of embedded control system for embedded AC drive used in aircraft applications. The design of aircraft applications embedded control systems is an interesting challenge due to the growing of control algorithm complexity, environment conditions and the rising of aircraft requirements and specifications. Moreover, high control reactivity and large bandwidth are essential for aircraft applications. This can be ensured based on mature technologies such as Field Programmable Gate Array (FPGA) digital platforms.

The FPGAs present a great interest to implement such complex algorithms [6]-[7]. Indeed, FPGAs provide high integration density and modularity. They also offer the possibility to design very powerful dedicated parallel architectures which can dramatically reduce the execution time. For a challenging aircraft embedded control system, the development of FPGA-based Intellectual Property (IP) modules is well convenient. It provides portability of modules between different targets. Consequently, it avoids losing time in development and certification which decreases the whole cost development system. Besides, for these critical applications, where the safety is of prime importance, the configuration must be kept against the SEU (Single Event Upset) radiations and even when power is off [76]. In this sense, FPGA Flash RAM technology has also demonstrated its efficiency in terms of reliability.

The evaluation of FPGA-based AC drives for electrical applications has been the focus of many researches. Providing a well-structured design methodology was their main concern [93],[11]. The evaluation of FPGAs has been extended to see how much it can be suitable for the implementation of complex AC drive controllers. A full hardware sensorless controller for a synchronous AC drive has been implemented [113]. It is based on the Extended Kalman Filter (EKF) which estimates the rotor position and speed. Other sensorless techniques based on high frequency carrier injection have also been

tested with Brushless Synchronous Starter Generator (BSSG) and successfully tested under an actual aircraft testbench [8].

Recently, FPGAs have integrated several heterogeneous natures of cores on a single chip. This approach, called System-On-Chip (SoC), consists of varied components like one or several processors, memories, matrix of programmable logic elements and interfaces, all in the same chip. This heterogeneous system allows taking a lot of advantages by the combination of software and hardware which provides more density integration and more flexibility [12],[10]. In this case, Hardware/Software (HW/SW) Co-design methodology becomes a strategic trend to optimally design embedded control systems.

Furthermore, with the ever increasing complexity of control algorithms, the management of the SoC-based embedded controllers can take advantages using a Real-Time Operating System (RTOS). This will provide an abstracted environment in order to simplify and to coordinate the behavior of the system. However, the overhead of RTOS services cannot be neglected especially for severe time constrain applications [29].

#### Thesis objectives and contributions

In the frame of the more electric aircraft domain, this PhD thesis is a contribution to the design of FPGA-based controllers for AC drives embedded applications. Based on a SoC approach, this work aims to optimally design the controllers. This is performed using a HW-SW Co-design methodology and a task manager. In the following, thesis objectives and author's contribution are detailed,

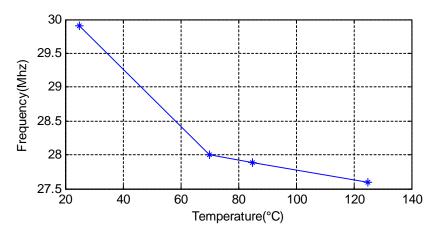

- In the frame of SEFORA project (Smart MEA For Operations in Rough Atmospheres), author has contributed to design and to test a digital controller of a high temperature synchronous drive. A design and validation methodology for FPGA-based digital controller was proposed. As first stage of validation, the proposed design method was tested on the ProAsic<sup>Plus</sup> board from Actel/Microsemi. The impact of the temperature on the operating frequency was also studied. In future, an ASIC board will be synthesized by another partner of the project [17],[10].

- A HW-SW Co-design methodology for AC drives has been proposed. Taken into account functional and architectural constraints, this method presents a guidance to optimally implement control modules between HW and SW. It is ranging from the early specifications of the system to the final experimental validation. The illustration of the proposed Co-design methodology was made based on the sensorless speed controller using the Extended Kalman Filter (EKF). The choice of this benchmark corresponds to a major trend in embedded control of AC drives [115], [129].

- The "Non-dominated Sorting Genetic Algorithm (NSGA-II)" was chosen to deal with the considered multi-objectives optimization. It aims to find the Pareto-Front of optimal solutions minimizing the SoC consumed resources and the execution time. Thus, a significant speedup gain has been reached compared to the pure SW solution.

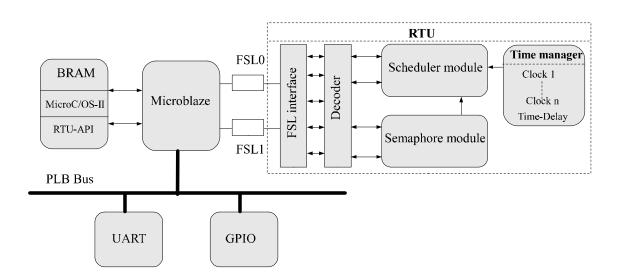

- The management of the SoC-based embedded controller was provided using an efficient Real-Time Operating System (RTOS). To accelerate the services of this

operating system, a Real-Time Unit (RTU) was developed in VHDL and associated to the RTOS. It consists in hardware operating system that moves the scheduling and communication process from software RTOS to hardware. The proposed design takes only 4.3% of the FPGA available resources which is very few compared to the obtained acceleration benefits.

#### Thesis outline

This thesis consists of five main chapters, described as follows.

Chapter 1 presents the background of this thesis. Then, the state of art of the digital platforms (FPGAs, ASIPs, ASICs, SoCs) used in embedded control systems is described. The interest of the SoC-based approach for AC drive applications is also discussed. Thus, a HW-SW Co-design methodology for electrical AC drives is proposed.

Chapter 2 deals with the design and validation of FPGA-based synchronous drive for high temperature environment. The designed controller is based on the Field Oriented Control (FOC) principle. The controlled system consists on the Permanent Magnet Synchronous Machine (PMSM) associated to a load and a resolver position sensor. As first stage of validation, the proposed method was performed using the ProAsic<sup>Plus</sup> board from Actel/Microsemi Company. These tests allow the preparation of the first-time-right corresponding silicon ASIC board.

Chapter 3 details the specifications and algorithm development steps of the Co-design methodology. Thus, hardware specifications of the controlled system, chosen switching period and control parameters are detailed. The adopted control strategy consists on the sensorless speed controller based on the Extended Kalman Filter (EKF). During algorithm development, the impact of time delay on the control bandwidth and stability margin is analyzed and time delay limits were defined.

Chapter 4 presents the architectural development step. It consists in two main steps: the performance estimation (area, time, memory size) and the HW-SW partitioning. The aim is to find an optimal partitioning of control modules between HW and SW in terms of area, execution time and memory size. The Non-dominated Sorting Genetic Algorithm (NSGA-II) was used to deal with this multi-objective optimization.

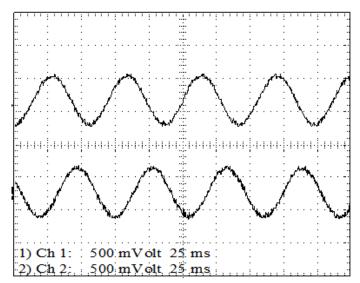

Chapter 5 describes the development of a HW-SW RTOS to provide the management of the controller tasks. To have a more deterministic RTOS, a hardware Real Time Unit (RTU) was developed using VHDL and was associated to the RTOS. It consists in hardware operating system that moves the scheduling and the communication process from software RTOS to hardware. The scheduler and the semaphore services were implemented in hardware. An experimental validation based on current controller was carried out using a laboratory set-up. The obtained results give proof of the interest of the proposed approach.

Finally, conclusions are drawn and perspectives are given.

Chapter 1 State of art of FPGA-based System-on-Chip for embedded control systems

### Chapter 1

# State of art of FPGA-based System-on-Chip for embedded control systems

#### 1.1 Introduction

Nowadays, Embedded Control Systems (ECSs) are becoming more and more sophisticated. This is a direct consequence of the growing complexity of control algorithm and the rising of industrial requirements [3],[2]. These requirements are not just limited to new algorithm concepts or a high level of performances. Indeed, flexibility, cost and time-to-market reduction are also of prime importance.

More specifically, the implementation of complex AC drives controller for avionic applications, which is the target application of this PhD, is a good example of these trends. In addition to the above mentioned requirements, these applications target always more reliable, efficient and most of all compact systems. In this context, the proximity of the digital control platforms from higher temperature heating sources, like the engines, are now investigated. This presents a serious technical issue. To cope with all these challenges, the use of efficient design methodologies which take benefits of the main advantages of the current digital technologies becomes crucial.

Among these technologies, the Field Programmable Gate Arrays (FPGAs) present a great interest for implementing such complex algorithms [4]-[9]. Their high integration rate and their ability to exploit the inherent parallelism of the algorithm to be implemented make them very advantageous compared to pure software solutions such as microcontrollers or Digital signal processors (DSPs).

Besides, it is now usual to implement processor cores within FPGAs. Hence, FPGA can be considered as full System-On-Chip (SoC) solutions that make them very attractive for implementing embedded control systems. However, an optimal implementation of control algorithm based on a SoC approach requires the use of a rigorous Hardware-Software Co-design methodology. Indeed, an efficient partitioning of the control algorithm between software and hardware parts must be established [13].

Furthermore, the use of Real-Time Operating Systems (RTOS) may provide a better management of the control tasks. It allows also embedded controllers to be designed, modified and expanded more easily.

In this chapter, the background related to this thesis is presented. Firstly, aircraft

application constraints are presented. Then, the available digital technologies used for implementing embedded control systems are presented. The interest of using FPGA and SoC approaches in the AC drive domain is also established and the needs to have a Co-design expertise is emphasized. Finally, a Hardware-Software (HW-SW) Co-design methodology for AC drives is proposed. It provides a full design flow ranging from specifications to the final FPGA implementation.

### **1.2** Aircraft application constraints

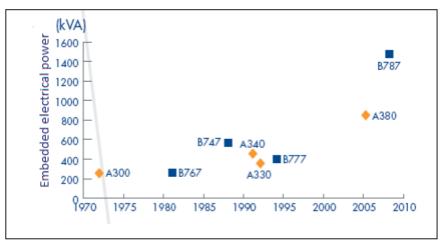

The More Electrical Aircraft (MEA) trend aims to increase the electricity part over the other types of energy on board of an aircraft [14]-[16]. This is mainly motivated by the expected gains in terms of weight, volume and cost. The inherent financial benefits have prompted aircraft manufacturers to integrate more and more power electronics systems in recent aircrafts. Figure 1.1 illustrates the progressive evolution of the embedded electrical power in recent aircrafts. As an example, the Electro Hydraulic Actuators (EHA) project aims to replace the initial hydraulic actuators by the Electro-Hydraulic ones. This system was successfully integrated into the airbus A320. The Electrical Thrust Reverser Actuation System (ETRAS), developed by Hispano-Suiza Company, has been also successfully used in the airbus A380.

Figure 1.1: Evolution of the embedded electrical power in the aircraft domain[15].

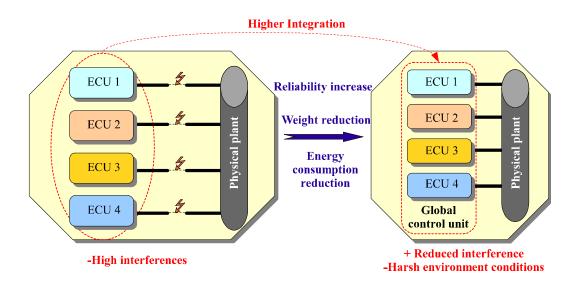

Along this trend and focusing on digital controller, the main objective is a better integration of the digital controller. Before, complex control algorithms were performed using several Electronic Control Units (ECUs) that ensure the control of a physical plant, as depicted by Figure 1.2.

Main challenges in designing embedded control systems are:

- Flexibility: This issue is related to the possibility to adjust or to modify a function without having to re-design the whole controller.

- Modularity: It consists in dividing the whole control algorithm in functional modules. These functional modules are stored in a library, called Intellectual Property (IP) module library. The elements of this library can be re-used during the development of new projects, thus capitalizing the knowledge of the design team.

Figure 1.2: Trends of the Embedded Control Systems.

- High integration: The deployment of heterogeneous functions into one system, called global control unit, needs a high level of integration. As depicted Figure 1.2, this will lead to a more compact system with a significant reduction of wires, a reduced Electronic Magnetic Interference (EMI) impacts and a more reliable system.

- Testability: Once the controller is implemented, it is of great importance to be able to test it easily.

However and even if the assets of employing more power electronics in aircraft are demonstrated, these gains are conjointly associated to new challenges such as environment conditions (high temperature, high pressure). The search for ever more compact systems and their location in harsh environment impact seriously the reliability of the devices. This is the case of Smart MEA For Operation in Rough Atmosphere (SEFORA) project study which deals with the development of ECSs working at a range of temperatures from -55 to  $200 \,^{\circ}C[17]$ . Part of our thesis work deals with this high temperature challenge. More details are provided in the next chapter.

#### **1.3** Hardware architectures

As said before, Embedded Control Systems (ECSs) are playing an increasingly important role in real-time control applications. Typical requirements are the development of small, reliable, and multi-functional system. In the same time, the continuous progress of CMOS technology and the increasing demands of new products have led to the integration of more and more transistors within a single chip, with respect of Moore's law.

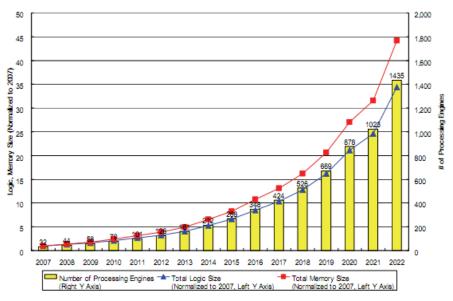

Moore's law states that the number of transistors on a chip is doubling every 18–24 months. As a result, more computing capacity and higher integration level are provided to deal with the growing complexity of applications. According to the regular International Technology Roadmap for Semiconductors (ITRS)[22], Figure 1.3 presents the rythm of growth of the number of computing cores and of the memory size integrated in a single chip.

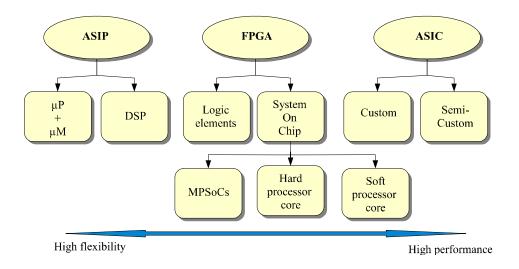

All these advances in digital electronics technologies lead to more efficient digital control units that take several forms. As shown in Figure 1.4, three main technologies are available: The ASICs, the FPGAs and the ASIPs.

Figure 1.3: The growing of the computing cores numbers and the growing of the memory size integrated on a single chip [22].

Figure 1.4: Hardware architectures used for embedded control systems

#### 1.3.1 ASICs

The Application-specific integrated circuits (ASICs) are divided into two main groups: the circuits designed for custom applications (custom) and the pre-characterized circuits (semi-custom). ASICs are characterized by a high level of integration, predictable and good timing, reliability, high performances and low power consumption. All these characteristics make them very suitable for operation in harsh environments. However, these circuits are well known for their high design cost and long development cycle. Hence, designer must follow a strict design methodology and leads rigorous verifications to ensure that there will be no functional nor timing problems on the final component. Moreover, these components are not used in the prototyping environment because they offer no programmability by the end user.

#### **1.3.2** ASIPs

Application-Specific Instruction-set Processors (ASIPs) are processes dedicated to a given field of algorithm and for specific applications. ASIPs can be seen as dedicated microprocessors that also have additional peripherals (such as general purpose input/output, timer, counter...) and communication interfaces (I2C, CAN, SPI...) to interact in real time with their environment. This high integration ability makes this type components well suitable for signal processing and control systems.

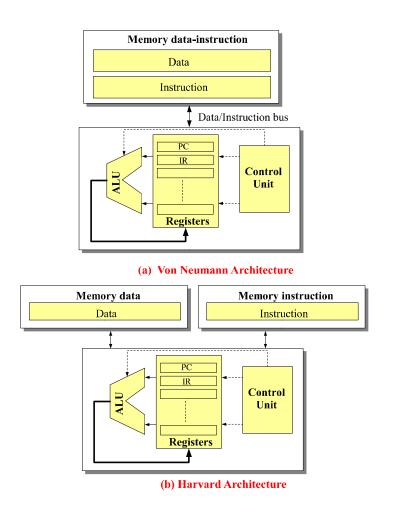

The earliest ASIP's architectures were based on Von Neumann principle, shown Figure 1.5.a. They used a single bus to transfer data and instructions from the memory to the CPU. Two improvements have emerged with the Harvard architecture (shown Figure 1.5.b) : the use of two separate memories and the use of pipeline. The first memory is used for data storage and the second one to store instructions. Thanks to pipeline, parallel processing can also be performed. These features allow faster processing and high data throughputs.

Figure 1.5: ASIPs architectures, (a) Von Neumann architecture, (b) Harvard architecture.

These ASIPs technologies have been used to perform a wide range of applications. Their main advantages are great flexibility and low cost. However, the use of these components is limited especially in applications demanding high computation performances. This is due to the fixed internal architecture which implies a serialization of the treatment.

#### 1.3.3 FPGAs

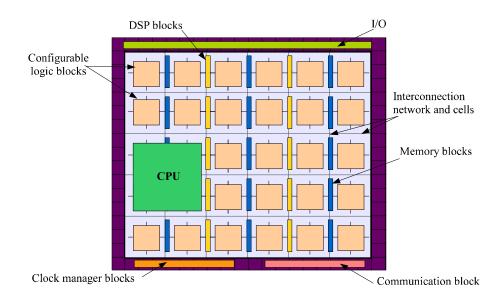

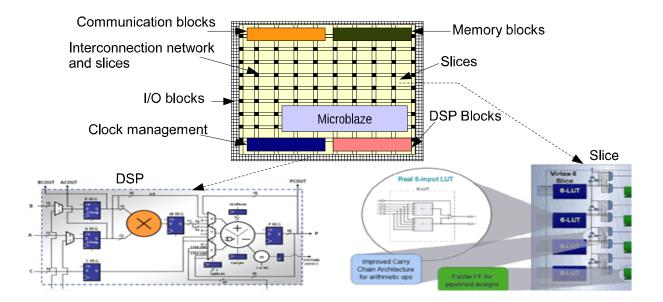

The FPGAs technology is a good compromise between the flexibility of ASIPs and the performances of ASICs. As shown in Figure 1.6, FPGAs are based on a sea of logic blocks dedicated to treatment and on elements of interconnection between these blocks. Coarser grain hardware elements such as DSP blocks, Hard/Soft processor cores, memories and clock manager are also provided in most of the recent FPGA platforms [73].

FPGAs offer the possibility to design very powerful dedicated parallel architectures which can dramatically reduce the execution time of the control algorithm to be implemented. For embedded control system, the development of a library of FPGA-based Intellectual Property (IP) modules is convenient. This provides portability of the corresponding modules between different targets.

Figure 1.6: Generic structure of a FPGA.

In the following, we will present briefly the most popular FPGA technologies:

- SRAM technology: It is mainly proposed by the Xilinx and Altera Companies. The advantages of this technology are its high density and its rapid reconfiguration. Moreover, these circuits can be dynamically reconfigured partially or entirely. This process is named dynamic reconfiguration. But, the main drawback of SRAM-based FPGA is the use of standard memory loaded at initialization because they use CMOS technology. So, the use of this technology is limited in case of critical-safety applications such as aircraft and automotive fields [73],[75].

- Antifuse technology: The principle of this technology is based on the injection of a high current or a laser that heats and then melts the silicon layer between endpoints

so as to make connections. So, the configuration is maintained even after power is off. However, it is a One-Time-Programmable technology. This makes it impractical in the case of prototyping environments.

• Flash technology: The configuration of this technology is based on flash connections that keep the configuration state when the power is off. Its immunity against the Single Event Upset (SEU) radiations and its reduced static power consumption make this technology attractive for embedded systems. However, the main disadvantages of this technology are the limitation of the available internal resources and the limited number of reconfiguration cycles [76].

#### 1.3.4 System-on-Chip

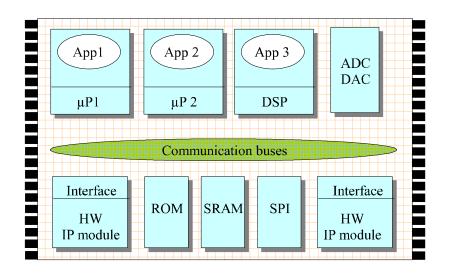

More recently, new architectures, called System-On-Chip (SoC) have emerged. A SoC architecture integrates within a single chip various components like one or more processors, analog circuitry, memories, a matrix of programmable logic elements (see Figure 1.7). By combining software and hardware, these solutions provide a better integration density, a reduced communication overheads and a good level of flexibility. All these assets prove that these solutions present a promising interest for control applications.

In SoC-based approaches, two types of processor cores can be considered, the "Hard processor core" and the " soft processor core".

Figure 1.7: Generic System-on-Chip architecture.

#### 1.3.4.1 Analog Device

Actel/ Microsemi Fusion family is a mixed-signal FPGA platform integrating processor and configurable analog. It offers a new level of integration by allowing the designer to implement an Analog-Digital converter (ADC) within the chip. It consists on a 12-bit ADC successive approximation. These features make these devices suitable for control applications [76], [10], [24].

#### 1.3.4.2 Hard processor cores

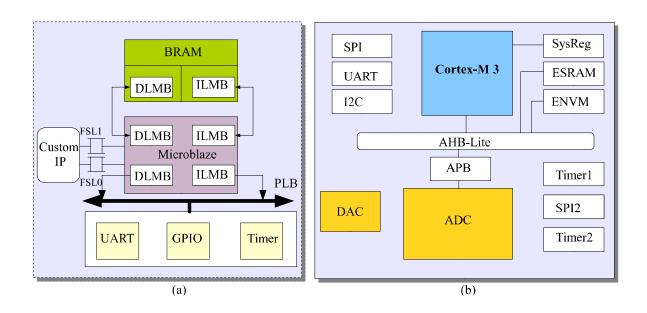

The hard processor cores are non-synthesized processors. They are characterized by a custom layout using VLSI which is integrated within the FPGA with other internal resources. To communicate with its external environment, this processor needs the use of some peripherals and buses that consume resources from the FPGA matrix such as communication buses, memories, timer and so on. These processor cores offer fast processing and communication advantages. For example, Altera provides an ARM9 processor in its series EPXA10 which are marketed as Excalibur <sup>TM</sup> device [75]. Xilinx proposes also a PowerPC 440 hard-wired on-chip [73]. Recently, Actel launched a Cortex-M3 integrated into a smart-Fusion FPGA [76]. The architecture of the Cortex-M3 is presented by Figure 1.8.b.

#### 1.3.4.3 Soft processor cores

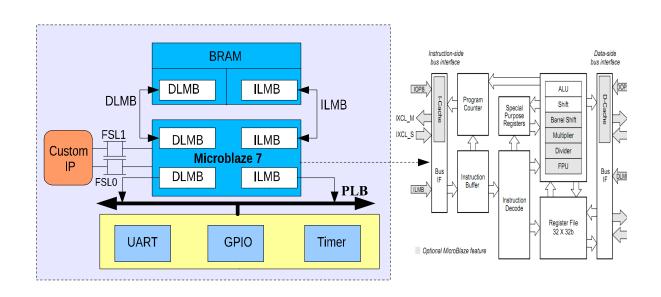

The soft processor cores are synthesized processors. The FPGA configurable logic cells are used to implement these processor cores. The main advantage is the possibility to choose the configuration options. Hence, designer can choose the processor functionalities that correspond to the final application. An example of soft processor core is the Xilinx Microblaze. Its architecture is presented Figure 1.8.a.

Figure 1.8: Processor architectures (a) Xilinx Microblaze soft processor core, (b) Actel/Microsemi SmartFusion Cortex-M3 hard processor core.

Table 1.1 presents a comparison between a standard DSP controller device and several SoC processor cores (Xilinx PowerPC hard core, Actel/Microsemi Cortex-M1 and Altera NIOS II/f soft processor core).

| Features             | Xilinx                            | Actel                                                                                                | Altera                    | Texas                            |

|----------------------|-----------------------------------|------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------|

| reatures             | Virtex - 5                        | Fusion1                                                                                              | Stratix III               | Intruments                       |

| CPU                  | PowerPC 440                       | Cortex-M1                                                                                            | NIOS II/f                 | DSP C28x                         |

| Frequency(MHz)       | 400                               | 60                                                                                                   | 290                       | 150                              |

| Bit Number           | 32 b                              | 16/32 b                                                                                              | 32 b                      | 32 b                             |

| Pipeline<br>stages   | RISC<br>superscalar<br>7 – stages | $\begin{array}{c} RISC \\ 3-stages \end{array} \qquad \begin{array}{c} RISC \\ 6-stages \end{array}$ |                           | DSP<br>8 - stages                |

| 32x32 Multiplier     | Hardware<br>(1 cycle)             | $Synthesizable \\ standard(3cycles) \\ small(33cycles)$                                              | $Hardware \\ (1 \ cycle)$ | $Hardware \ (1 \ cycle)$         |

| ADC                  |                                   | SAR - 12b<br>rate: 600Ksps                                                                           |                           | Pipeline - 12b<br>rate: 12.5Msps |

| Logic cells<br>Usage |                                   | 4353                                                                                                 | 1020                      |                                  |

| Synthesizable        | No                                | Yes                                                                                                  | Yes                       | No                               |

| Configurability      |                                   | ++                                                                                                   | ++                        | _                                |

| Performance          | ++                                | +                                                                                                    | +                         | ++                               |

Table 1.1: Features of processor cores for SoCs

A recent study made by Texas Instruments compares the indicated architectures to some other popular architectures [23]. Table 1.2 presents the summary of the presented report. The comparison is based on time-to-market, performance, price, development easiness, power consumption and flexibility.

|            | Time-to-market | Performance | Price     | Power     | Flexibility |

|------------|----------------|-------------|-----------|-----------|-------------|

| ASIC       | Poor           | Excellent   | Good      | Excellent | Fair        |

| DSP(ASIP)  | Excellent      | Fair        | Good      | Good      | Excellent   |

| FPGA       | Good           | Excellent   | Poor      | Poor      | Fair        |

| MCU(ASIP)  | Excellent      | Fair        | Excellent | Fair      | Excellent   |

| RISC(ASIP) | Good           | Fair        | Fair      | Fair      | Excellent   |

Table 1.2: Architectures comparison [22]

#### 1.3.5 Multi-Processor System-on-Chip

Real-time applications are becoming increasingly complex. This explains the motivation towards the use of Multi-Processor in System-On-Chip architectures (MPSoC). This offers a higher level of performance over a single processor, especially in terms of computation performances [25]-[26].

However, the main MPSoC design challenges are the communication infrastructure. Indeed, most of these communication models are based on dedicated channels or shared

buses. Unfortunately, scalability is limited by serialization of multiple requests to access to the bus. One promising approach is the concept of network-on-Chip (NoC). It consists in a set of routers that compose a network, which allows all the nodes connected to it (containing system resources and cores) to communicate with each others [27],[28]. This promises higher communication bandwidth than standard buses and more reusability.

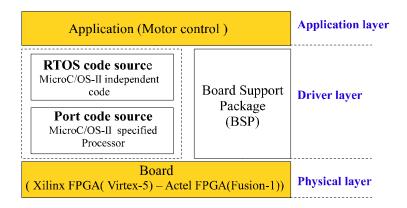

#### 1.3.6 Multi-layer software architecture

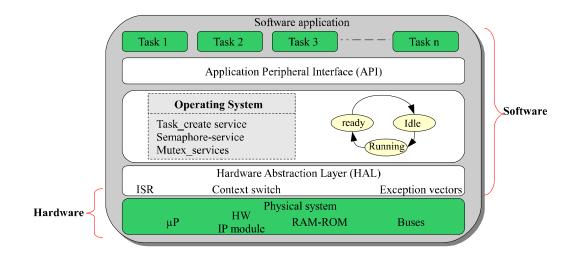

To deal with the rising complexity of control applications, the use of an operating system allowing the management of tasks and hardware resources is becoming necessary [29]. As far as the software part is concerned, different levels of abstraction between the application and the hardware that runs it can be established. Figure 1.9 shows the different layers between the physical system and the application.

Figure 1.9: Multi-layer software architecture.

- Software application: It integrates one or more functional tasks to be executed. This part depends on the studied application.

- Application peripheral interface (API): It is also called middleware. It provides the mapping between the RTOS services and the application. The advantage of using common API is to provide the portability of the application to other standard-based operating systems.

- Operating system: It includes all the RTOS initialization functions and services (scheduler, semaphore\_service, Mutex\_service...) that allow the management of the available resources. Using a single processor, the system can implement pseudo-parallelism in the software part by multiplexing the resources.

- *Hardware Abstraction Layer (HAL):* This part was defined to overcome the disadvantages of dependency of the RTOS on the used hardware architecture. Using the HAL (including ISR, Context switch, exception vectors..), the RTOS can be used regardless the physical system on which it is executed. This can be provided using a low level interface which is dependent on the used processor. Generally, it is developed using assembly code.

• *Physical system:* It represents all the available hardware resources of the system. In the case of SoC approach, it consists in one or several processors, memories blocks, logic elements and so on.

### 1.4 FPGA-SoC design flow

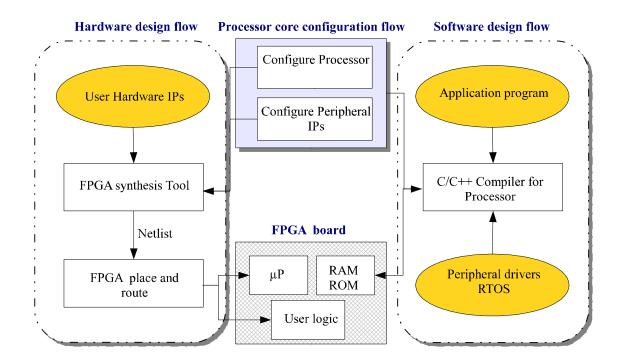

Designing SoCs requires the use of appropriate tools. Thus, FPGA companies provide development tools for software and hardware parts. Figure 1.10 shows the standard design flow for SoC application development. This design flow consists of two main procedures: the hardware design flow and the software design flow. The first flow includes hardware design and verification tools (VHDL/Verilog editor, synthesizer, place/route and implementation and simulation tools). The second flow offers a user-friendly interface that allows the designer to customize the processor for a specific project. After its configuration, the processor core is generated in the form of an HDL file (in the case of Altera and Actel tools) or a netlist file (in the case of Xilinx tools) [73], [75], [76]. Then, this file can be associated to custom user logic and integrated within the hardware design flow to be synthesized, placed and routed. The FPGA can be configured with the resulting bitstream file. Then, the program which will be integrated on the soft processor core can be compiled with the associated library files and C header files. A  $C/C^{++}$  compiler targeted for this processor is also provided. For example, Xilinx provides the Embedded Development Kit (EDK) platform, Altera provides the Embedded Design Suite (EDS) platform and Actel/Microsemi provides the SoftConsole platform.

Figure 1.10: FPGA-SoC design flow.

### 1.5 Interest of the SoC approach for AC drive applications

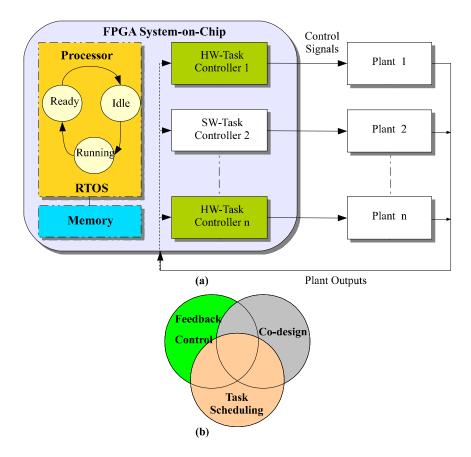

As shown in Figure 1.11.(b), designing embedded control systems based on a SoC approach involves three main fields: feedback control, task scheduling and Co-design process. Hence, the whole control performance is not only related to how control algorithm was assessed, but it also relies on the scheduling policy and the Co-design procedure. Unfortunately, the development of embedded control systems is generally done by separated teams. Thus, control designers may consider that digital platforms are sufficiently deterministic to deal with the periodic treatment of control algorithms. These latter are often associated to severe timing constraints which can affect control performances once violated. Therefore, the scheduling of these real-time control applications presents a key issue since it is strongly related to the system performances.

One solution is to combine Feedback control scheduling and Co-design processes. Thus, the goal will be the optimal use of the digital platform resources and the maximization of the performances of the whole control system. Consequently, there is an increasing need to consider simultaneously the control performances and the digital design in order to develop cost efficient control application. This can be reached based on HW-SW Co-design methodology for AC drive which promotes the cooperative development of the control assessment and the task scheduling-design step in a single design flow. Figure 1.11.(a) presents the use of SoC-based approaches for multitasking control applications. The principle is to control several plants by adjusting the timing attributes of controller tasks. This is a quite interesting approach because it allows the centralization of the control process for multi drive applications. The control tasks can be implemented indifferently in software or in hardware. All tasks can be scheduled using a RTOS.

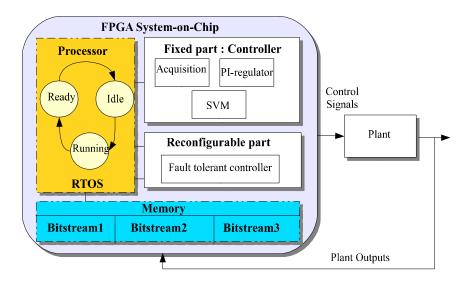

Figure 1.12: Reconfigurable control architecture.

Furthermore, reconfigurable FPGA platforms offer an interesting potential for use in the embedded control systems. It provides the possibility to be reconfigured or even better to reconfigure itself totally or partially without affecting the rest of the architecture. Therefore, the flexibility is no longer restricted to software [30]. Hence, in the case of control strategy change or monitoring process, the controller can be reconfigured in few microseconds while the system is continuing to work properly [31],[32]. This could be greatly appreciated especially for health monitoring control applications and robotics applications.

The reconfiguration can also improve FPGA fault tolerant in the case of SEU problems (case of SRAM technology). An overwriting of the existing configuration can be made while keeping the board in active operation mode [33], [34]. Figure 1.12 shows an example of FPGA partial reconfiguration. Under faulty condition, a fault tolerant controller can be downloaded in the reconfiguration part. This will allow the continuity of control function and avoid the system degradation. The reconfiguration process is provided using a RTOS and the Bitstream is saved in the memory. More than one Bitstream can be used to perform several configuration processes.

Now as the interest of SoC-based approach for embedded control systems is presented, a full HW-SW Co-design methodology for AC drives applications will be presented in this Ph.D. work. A brief description of the proposed Co-design methodology is now given. Details will be given in chapter 3 and 5.

### 1.6 Co-design methodology

"Hardware-Software Concurrent Design" , also called "HW-SW Co-design", is generally based on two important steps: modeling and partitioning that are strongly related.

#### 1.6.1 Modeling

The modeling presents a key issue to handle the growing complexity of Co-design approaches. Thus, a variety of models has been developed to represent heterogeneous systems. These models are related to the nature of application domains. For example, real-time systems will be modeled on a timing basis while data base-systems will be modeled on a data exchange flow basis.

In the following, author presents briefly the main representation models that were used in the field of Co-design.

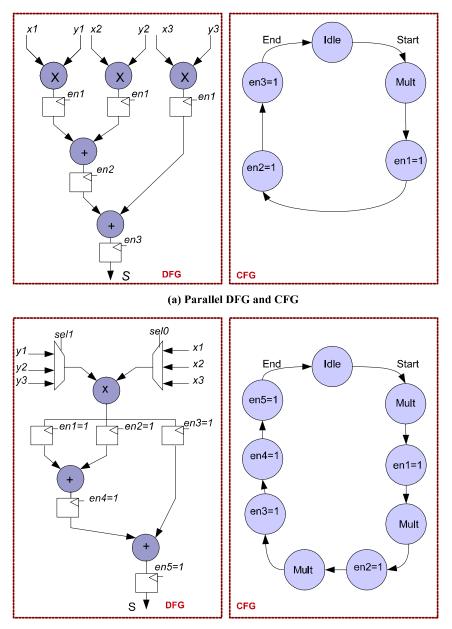

- *Model based on data flow graph*: It is often used to model systems characterized by strong data dependency. Thus, these models consist of nodes representing operations and edges representing data transfer between operations. The execution of a node is possible only if all its input data are available [37].

- *Model based on communication process competing*: This model is characterized by its ability to describe the parallelism of an application. Systems are modeled as a set of processes that run independently. Thus, all the processes are strongly decoupled to promote the parallelism and flexibility of system modeling. This type of modeling is very suitable for applications in the field of telecommunication [38].

- Model based on *Petri net*: It is a graphical representation of system behavior based on causal relationship between events affecting the system (transition, data transfer). Time is explicitly associated with these representations in order to build realistic models [36].

- Model based on Finite state machines (FSM) : The classical FSM is considered the best known model describing control systems. This model consists of a set of states, a set of input / output. The main disadvantage of this approach is the significant growth of states depending on the complexity of the application [35].

- *Reactive synchronous model* : This model is able to describe complex control applications characterized by strong competition between tasks. Often, the timing characteristics of these models allow the description of real-time systems using concurrent processes. This approach is based on parallel and asynchronous communications [39].

In the present work, the proposed Co-design methodology is based on the data flow graph model since it reflects accurately the characteristics of the control algorithm to be implemented (see chapter 4).

#### 1.6.2 Partitioning

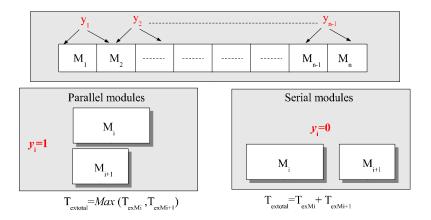

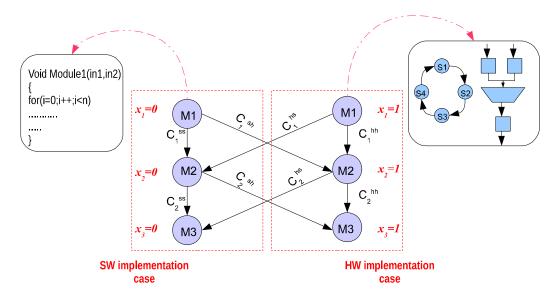

One of the main steps of Co-design methodologies is the HW-SW partitioning. Indeed, the goal is to find the optimal partitioning of application tasks between SW and HW in terms

of area allocation, time scheduling and memory use. The efficiency of the partitioning step depends on two main parts: the considered granularity level for tasks description and the used optimization algorithm.

The granularity level deals generally with two level : fine and coarse. The first one considers basic arithmetic operators such as (subtraction, addition, multiplication...). The second one presents more complex functions using several basic operators.

The optimization algorithm deals with the scheduling and the allocation of tasks. The focus here is to achieve objectives considering constraints. Several optimization algorithms were used to solve this kind of problem. These algorithms are genetic algorithm [106]-[107], branch-and-bound algorithm [98], Integer Linear Programming (ILP) algorithm [99]. More details will be given in section 4.7.

#### 1.6.3 Modeling tools for Co-design

The literature concerning HW-SW Co-design methodologies is very rich and several approaches with different partitioning techniques were proposed. The main tools are briefly discussed below.

- SystemC : It consists on C <sup>++</sup>class library. The integration of timing characteristics of the system and the competition between tasks are possible. This language was successfully used to model heterogeneous HW-SW systems. Tests based on the modeling of operating systems were also performed [40].

- *Polis* : It consists in a complete development class C (modeling, verification and simulation tool). This tool deals with control oriented applications. Thus, it is based on FSMs that are well suitable especially for the control applications. But, the use of this tool is not adapted for applications dominated by data processing [41].

- *Ptolemy* : It is a design environment developed at the University of Berkeley. It provides modeling, simulation, and design of concurrent tasks. It is mainly based on DFG and FSM modeling.[45].

- Syndex : This tool presents a system level CAD software based on the algorithm architecture adequation  $(A^3)$  methodology. It is generally used for rapid prototyping and aims to optimize the allocation of the available resources [43].

### 1.7 Proposed Co-design methodology for electrical drives

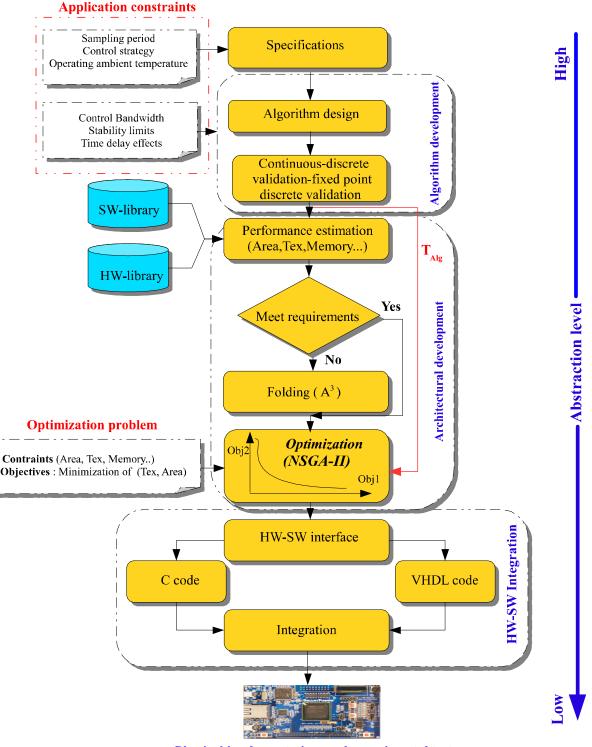

The proposed Co-design methodology aims to link the assessment of control performances and the HW-SW partitioning of control modules, at early stage of the development. As shown in Figure 1.13, this method is decomposed into four main steps: specifications, algorithm development, architectural development and HW-SW integration.

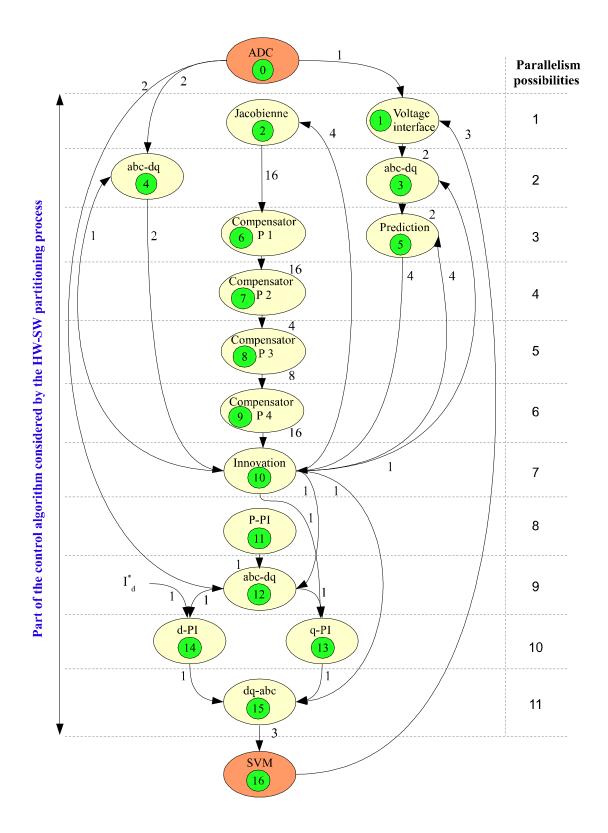

This method has been illustrated using a speed sensorless controller based on an Extended Kalman Filter (EKF). The details of the proposed benchmark are presented in the rest of this PhD report (Chapters 3, 4 and 5).

A-Specifications

The development of an AC drive application begins always by the specifications of the whole control application. This includes the definition of the used physical system and of the control parameters. The specification of the physical system consists in choosing the AC motor, the digital control unit, the Analog to Digital (ADC) and the Digital to Analog Conversion (DAC) interfaces. The environment conditions (high/low/ambient temperature) should be also defined since it affects the whole control performances.

In our case, a speed sensorless controller based on a EKF is considered. The EKF is used to estimate the position and speed of the rotor. It is characterized by its high level of complexity, including matrix multiplications and inversion. Two switching frequency rates are also considered: 20 kHz (presenting an example of a constrained switching frequency applications) and 100 kHz (presenting an example of an high demanding application). This part is developed in chapter 3.

#### **B-Algorithm** development

The Algorithm development process aims to the design and the validation of the control algorithm. Firstly, a modular partitioning is adopted. It consists in dividing the whole control algorithm into independent and reusable modules. In our cases, we consider functional modules (transformation, regulator, acquisition...). Then, continuoustime functional simulations are performed using Matlab-Simulink Tools. This allows the verification of the correct functionality of the considered control system.

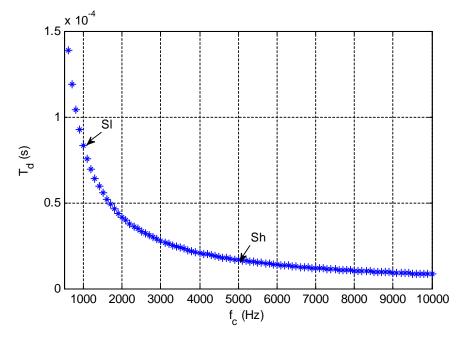

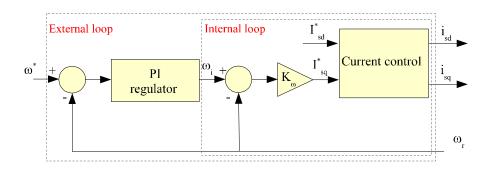

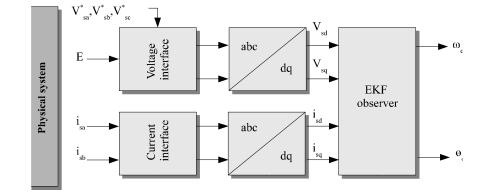

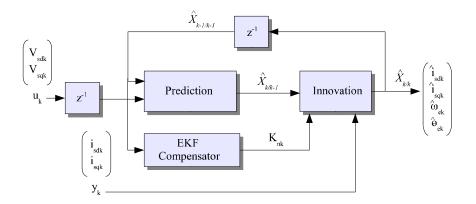

Then, the time delay impact is quantified. Its effect on the control performances is analyzed in time and frequency domains. Thus, the maximum allowable time delay regarding the specified phase margin and bandwidth is obtained. The maximum allowable time delay will be further considered as a timing constraint during the HW-SW partitioning process.

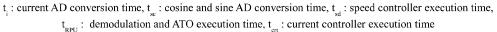

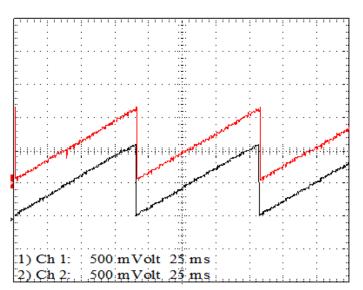

Next step of the algorithm development consists in the discretization and the normalization of the whole control algorithm. Here, a digital re-design approach is considered. Firstly, the control is synthesized in continuous time domain. Then, a discrete version of the control algorithm is derived using Euler transformation method. Then, a normalization is applied and a fixed-point discrete equivalent control algorithm is obtained.

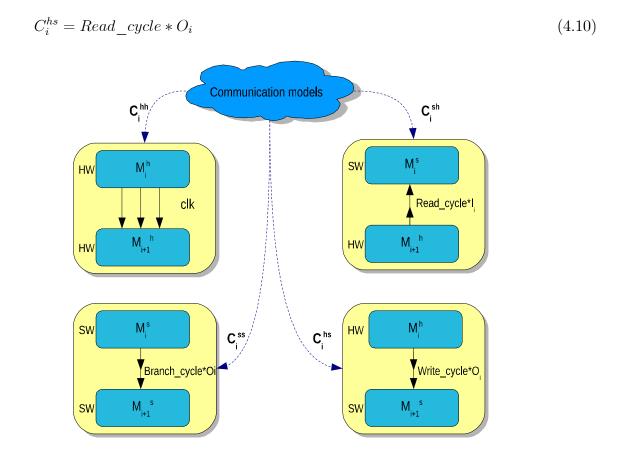

#### C-Architectural development

Once the control algorithm to be implemented has been validated, the designer can undertake the architectural development phase. It consists in optimizing the HW and SW resources allocation when implementing the control algorithm. This requires a proper space exploration method based on two main steps: the performance estimation and the HW-SW partitioning. The first step allows the estimation of area, time and memory size for each control modules. In the favorite case where the application doesn't violate the architectural constraints especially the area one, designer can go directly to the partitioning step, otherwise designer must perform a Folding step. This latter is achieved based on the  $A^3$  methodology [44].

Then, the HW-SW partitioning of the control algorithm is performed. The target is to minimize area, time and memory size with respect to the functional constraints ( $T_{Alg}$ which is the maximum allowable execution time derived from the algorithm development step) and to the architectural constraints (available resources). It is clear that it is a multi-objectives optimization problem. To deal with, the Non-dominated Sorting Genetic Algorithm (NSGA-II) was adopted. This optimization algorithm aims to find the Paretooptimal solutions satisfying both the functional and the architectural constraints. More details are provided in chapter 4.

Physical implementation and experimental tests

Figure 1.13: Co-design methodology for AC drive.

#### **D-HW-SW** integration

Once the HW-SW partitioning is performed, designer begins the HW-SW integration step of the chosen optimal solution. It consists in the development of the VHDL code

of the control modules to be implemented in HW and the development of the C code of the ones to be implemented on the SW. The communication between the two parts is allowed using the HW-SW communication interfaces. The integration of all these parts presents the next step. According to the design flow given in Figure 1.10, the physical implementation process can be performed and the Bitstream downloaded. Finally, the experimental validation of the chosen solution can be realized.

### 1.8 Conclusion

In this chapter, author has presented the background of this thesis. The new trends and the associated issues regarding embedded control systems have been given. A brief presentation of the available architectures (FPGAs, ASIPs, ASICs, SoCs) used in embedded control systems was firstly presented. Then, the interest of the SoC approach for AC drive applications has been discussed. Finally, the proposed Co-design methodology for electrical drives has been investigated. It consists on well-structured steps providing guidance for the SoC-based control applications. This method covers the whole development chain ranging from the specifications to the FPGA-based experimentation validation.

# Chapter 2

# Design and validation of FPGA-based motor drive for High-Temperature environment

### Chapter 2

# Design and validation of FPGA-based motor drive for High-Temperature environment

#### 2.1 Introduction

Among embedded system trends, the one concerning More Electrical Aircraft (MEA) is probably one of the most challenging for electrical engineers. Indeed, even if the expected gains in terms of weight and volume due to the ever increasing part of electricity over the other types of energy on board of an aircraft are really significant, one cannot ignore the technical issues that come along [1]. The search for ever more compact systems and their location in harsh environment impacts seriously the reliability of the devices. The SEFORA project on which the author has contributed during her PhD is a good illustration of this problematic. The goal of the SEFORA project (Smart MEA For Operations in Rough Atmospheres) is to build a demonstrator of a full synchronous drive that is able to operate at 200 C° ambient. The corresponding actuator and its associated electronics are intended to be located near the reactor. As can be seen, electronics able to work at high temperature is of prime importance in this case [46]-[48].

More specifically, author has contributed to design and to test the digital controller of this high temperature synchronous drive. The designed controller is based on the Field Oriented Control (FOC) principle.

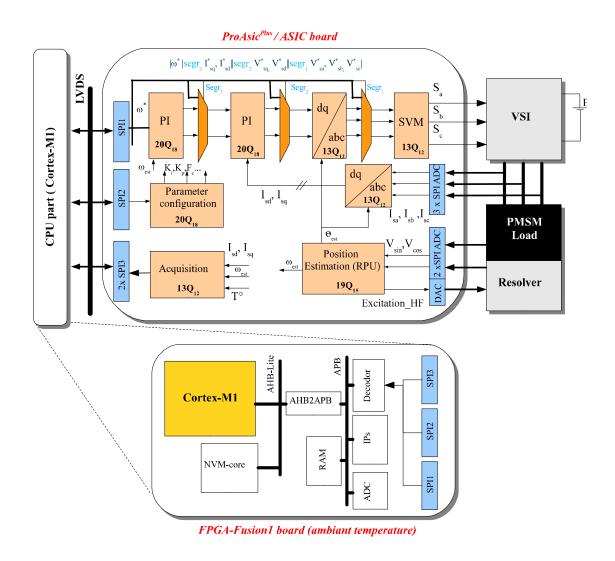

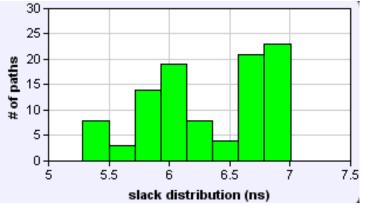

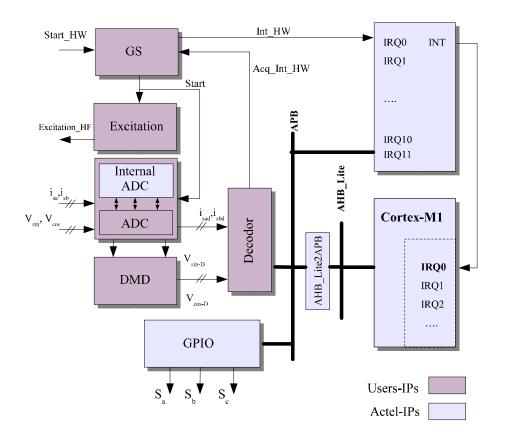

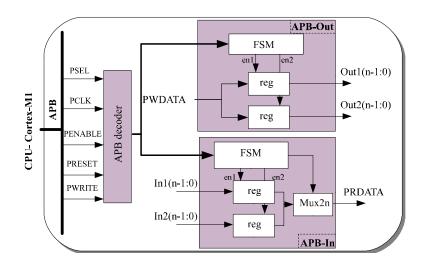

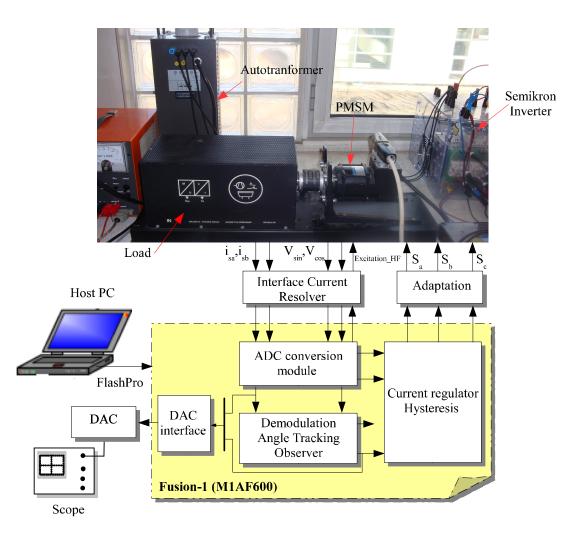

In this chapter, author proposes a design and a validation method for digital control architecture working in high temperature environment. To this purpose, two control boards were considered: an ASIC (CMOS  $0.35 \,\mu$ m) and a ProAsic<sup>Plus</sup> (AP1000) from Actel-Microsemi Company. However, as first stage of validation, the proposed design method was only tested on the ProAsic<sup>Plus</sup> board, knowing that the ASIC board will be synthesized later by another partner of the project. The impact of the temperature on the operating frequency was also studied. Then, the architecture has been implemented at a frequency of 24 MHz with a junction temperature of 125 °C. Besides, a fault tolerant design strategy was also provided using segregation scenarii. This allows segregating the architecture of the controller in several operating zones. As a consequence, the risk of design issues when synthesizing the ASIC is minimized. The segregation control signals are controlled by a secure processor working at ambient temperature (soft processor core "Cortex-M1" implemented in a Actel/Microsemi Fusion-1 FPGA ).

Regarding validation, a modular approach was chosen for testing the different control modules. As a final validation step, the whole controller was tested in real-time with an FPGA-based emulator of the drive.

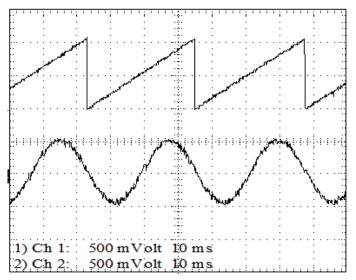

Finally, having in mind in the future a system-on-chip solution for embedded drive control, this chapter ends by an evaluation of a full software implementation of a current controller for AC drives in the Cortex-M1. Thus, the ability of a soft processor core to implement a motor control is examined and its limits is given.

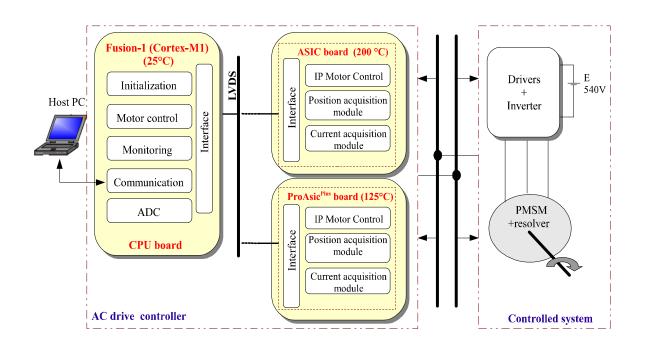

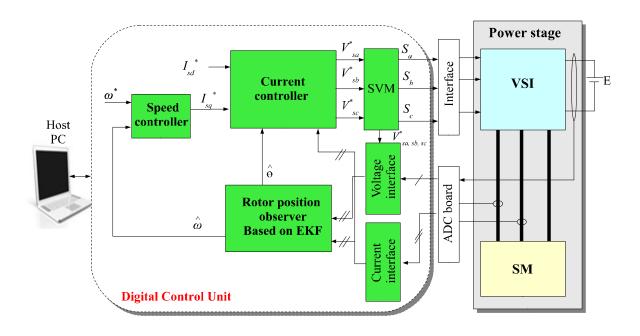

#### 2.2 Application overview

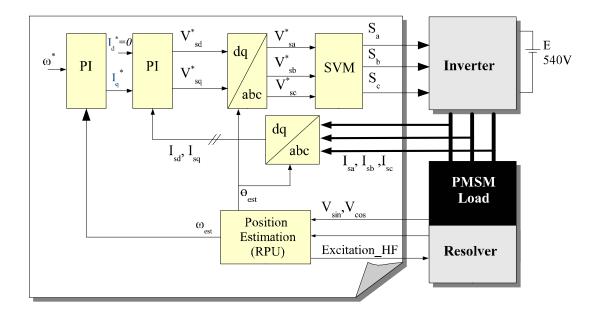

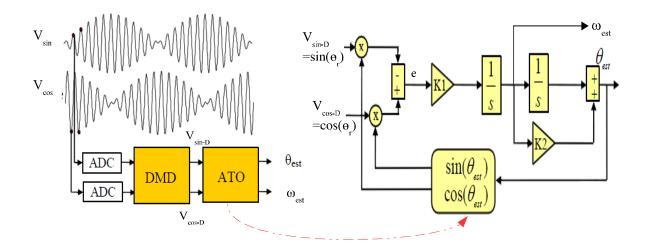

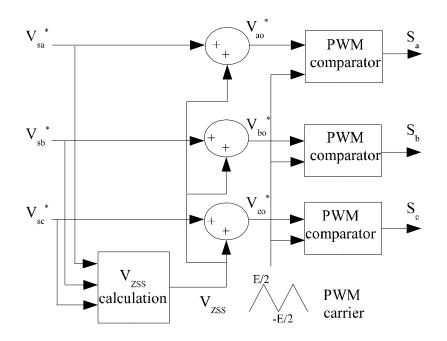

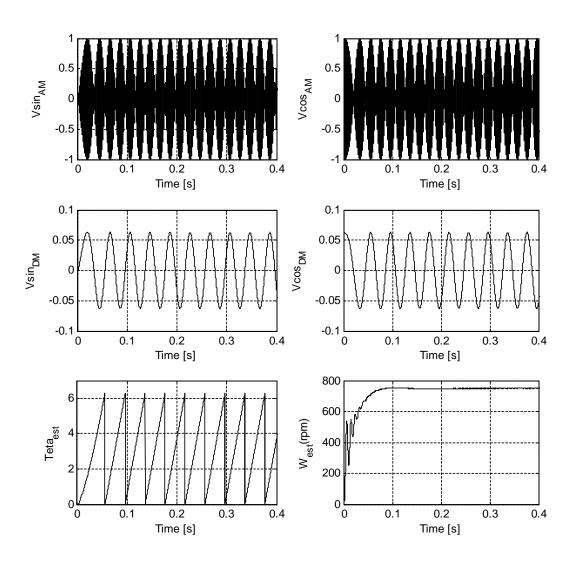

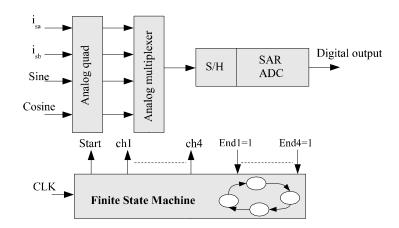

The electrical control system considered in SEFORA project is presented Figure 2.1. It consists of a Permanent Magnet Synchronous Machine (PMSM) associated to a load and a resolver position sensor. This PMSM is supplied by a Voltage Source Inverter (VSI). The switching signals of the VSI are provided by the control algorithm which ensures two functions: the current control and the speed control of the PMSM. The position is estimated via a resolver. The corresponding treatment is achieved using a Resolver Processing Unit (RPU). The whole controller is based on the Field Oriented Control (FOC) principle.

Figure 2.1: The synoptic of the actuator control board (SEFORA project).

Placed near the engine, the controller is faced to new constraints in link with high temperature. Therefore, the control algorithm was implemented using two boards: an ASIC and a FPGA. The ASIC, located in the high temperature zone (200 °C), contains the modules of motor control ( abc-dq transformation, dq-abc transformation, PI regulator, SVM...) and the RPU module. In ambient temperature zone (25 °C), the SoC Fusion-1 from Actel family embedded the Cortex-M1 soft processor core was chosen. It implements the initialization, the monitoring modules and the communication process between the control boards and the Host PC.

The communication between the two boards is ensured by the use of Low Voltage Differentiate Signals (LVDS). This presents a safe method to transfer information for a long distance (separation between harsh and ambient environment) which is the case of our application.

For security reason, the control system was duplicated to ensure system redundancy and more safe control in the case of faulty conditions. Thus, the first control system is based on a FPGA Fusion-1 board associated to the ASIC one. The second control system is based on FPGA Fusion-1 board associated to the ProAsic<sup>plus</sup> (APA1000) one.

In this chapter, two objectives are considered. The first one aims to the development and the validation of control algorithm under high temperature environment. The CMOS-ASIC technology  $0.35 \,\mu\text{m}$  presents an interesting solution. However, it is widely known that ASICs are difficult to design and require significant costs and development effort [49]. Therefore, all tests were first carried out using FPGA ProAsic<sup>plus</sup> APA1000 board. This was performed based on a rigorous validation methodology. Thus, these development and verification steps present the first stage of validation of the final ASIC board. This latter will be designed by IDMOS Company.

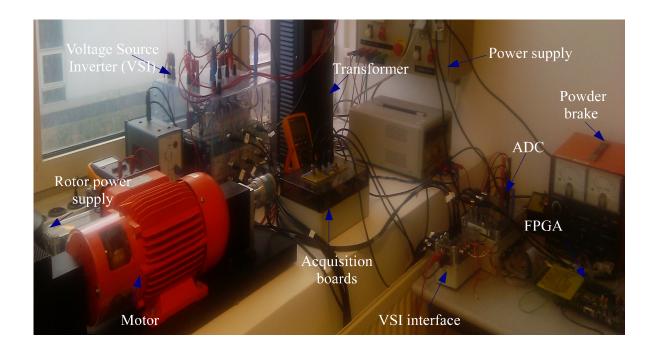

The second objective is the evaluation of SoC performances for real time control applications. To this purpose, the FPGA-Fusion1 board was chosen. It is characterized by mixed signal elements such hardware architecture (FPGA logic elements), internal Analog Digital Converter (ADC) and soft processor core (Cortex-M1). As testbench, a single current controller based on ON/OFF algorithm was considered. Such simple algorithm allows a first evaluation of the chosen SoC performances .

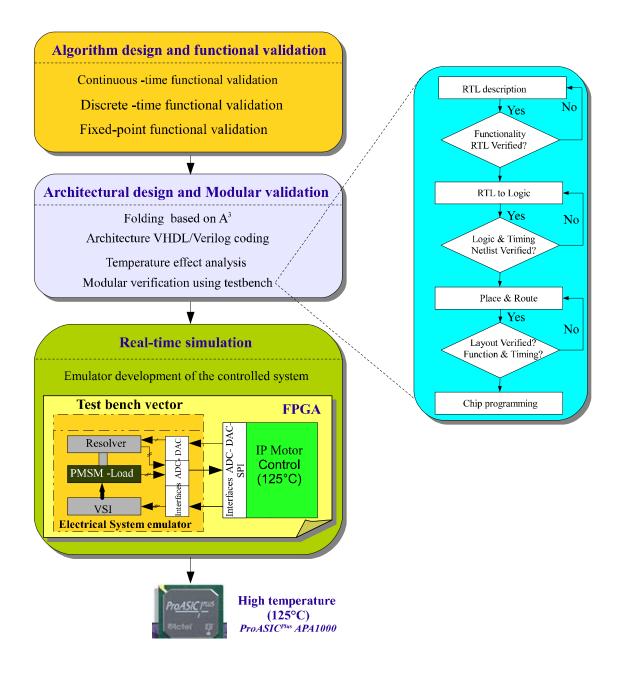

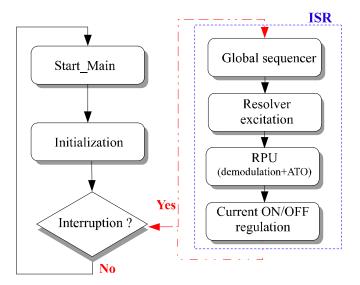

# 2.3 Design and validation methodology

The proposed methodology to validate the control algorithm is presented in Figure 2.2. This method is composed by three main steps [17].

A- Algorithm design and functional validation: It consists of designing and validating the control algorithm under Matlab-Simulink environment. The continuous-time, the discrete-time and the fixed-point discrete-time simulations are respectively performed [65].

*B-* Architectural design and modular verification : This step deals with the architecture development and its validation. Based on the  $A^3$  methodology, the folding procedure is applied to the greediest operators in terms of consumed resources [44]. After that, a design verification flow, similar to the ASIC one, is used. It includes synthesis, place and route, timing analysis steps for each control block. Analysis regarding the temperature environment is also carried out to determine its impact on the designed architecture.

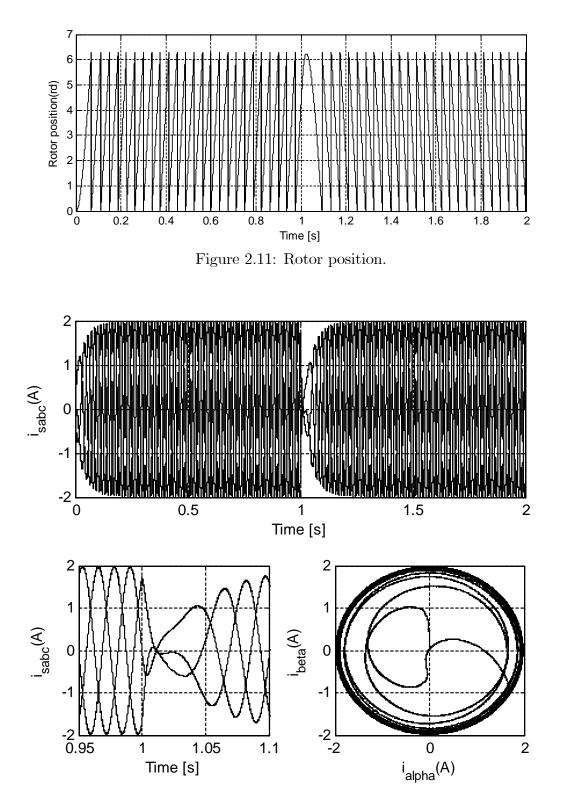

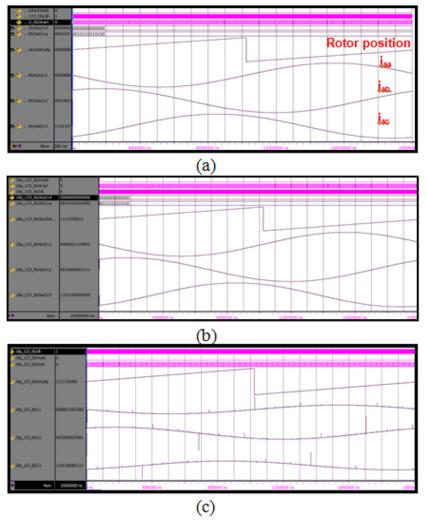

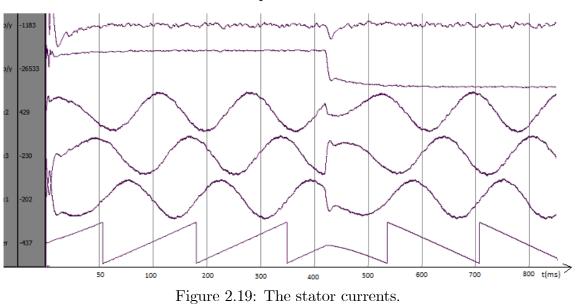

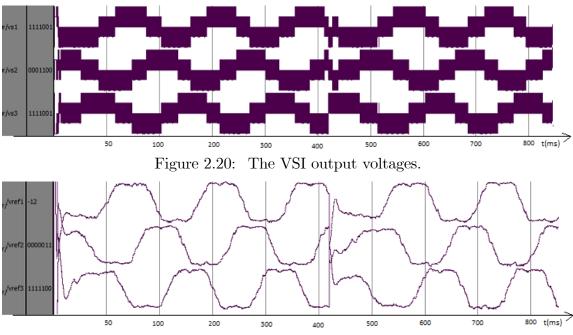

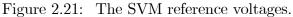

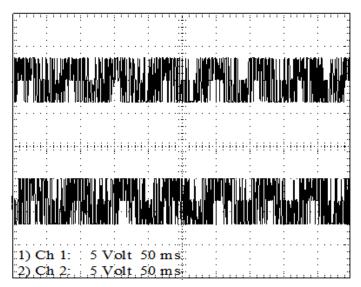

*C- Real-time simulation* : As global verification procedure, a Real-Time Simulation (RTS) of the electrical system, written in VHDL and implemented in FPGA, is used. It allows the validation of the controller before its application to the actual system allowing the analysis of the drive under several operating conditions [50], [51]. The developed emulator consists of power elements (Voltage Source Inverter "VSI", Permanent Magnet Synchronous Machine "PMSM") and AD interfaces (Analog Digital Converters "ADC", Digital Analog Converters "DAC"). Each of the indicated steps will be described in more details in the following sections.

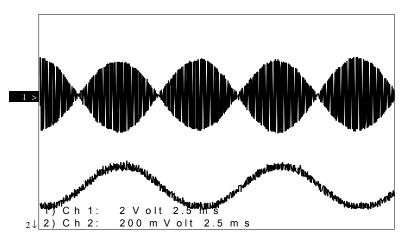

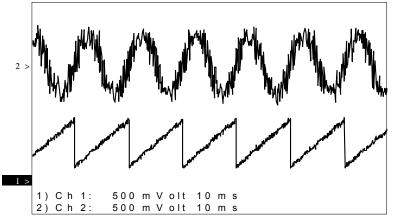

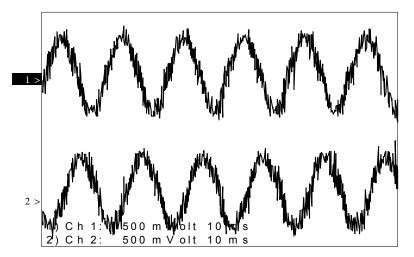

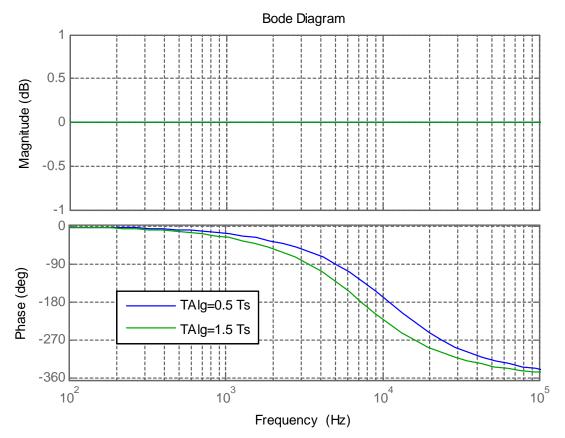

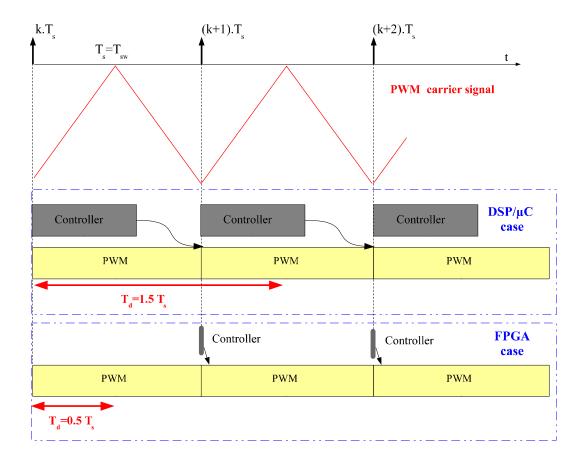

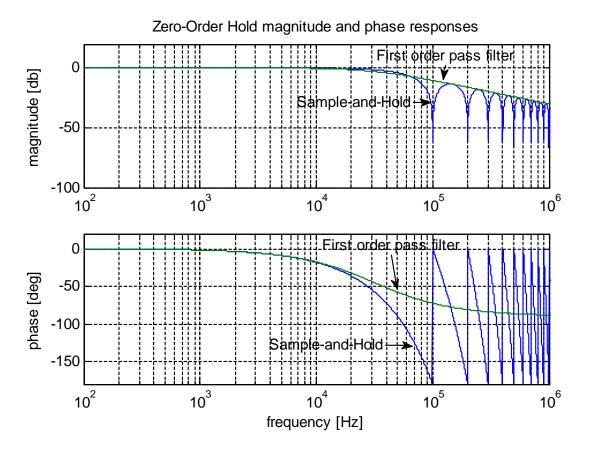

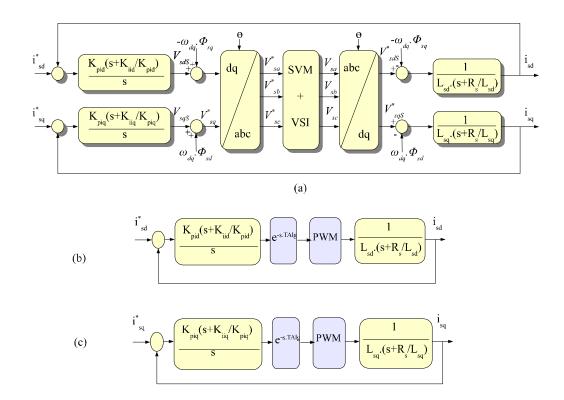

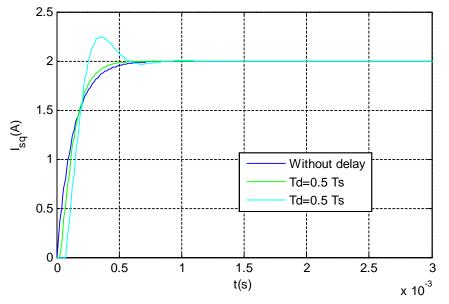

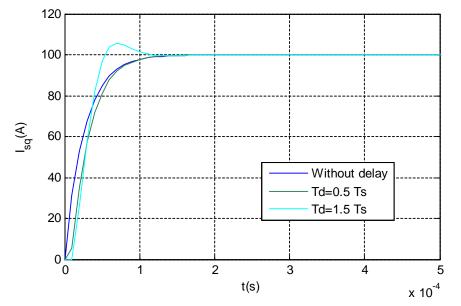

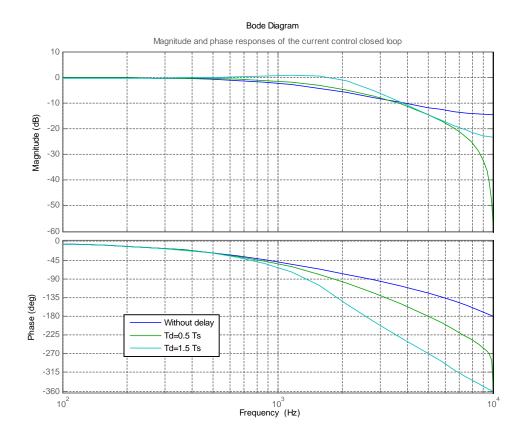

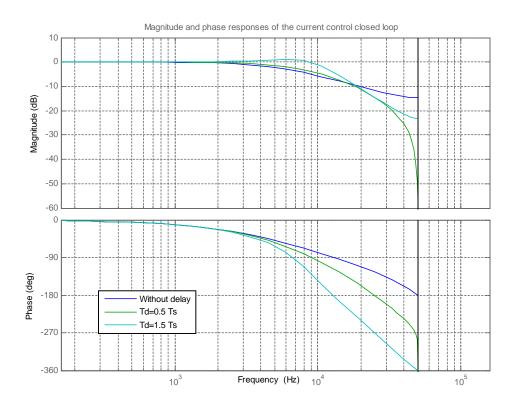

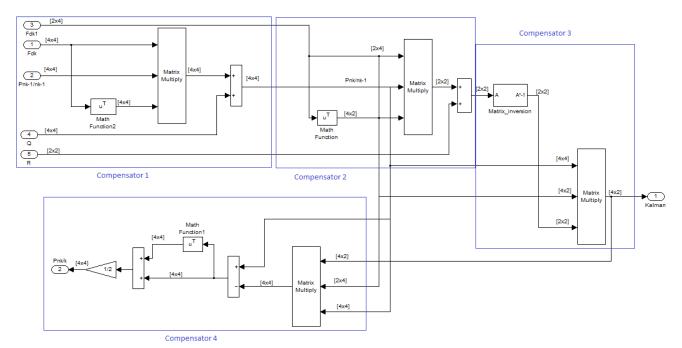

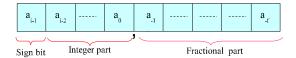

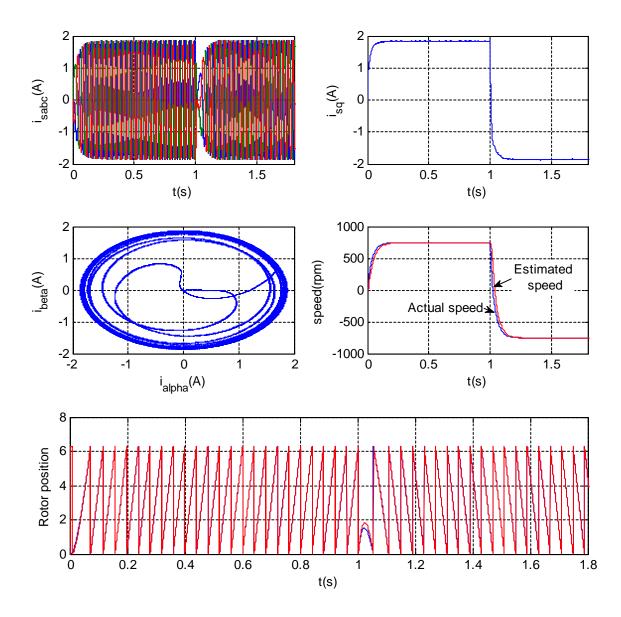

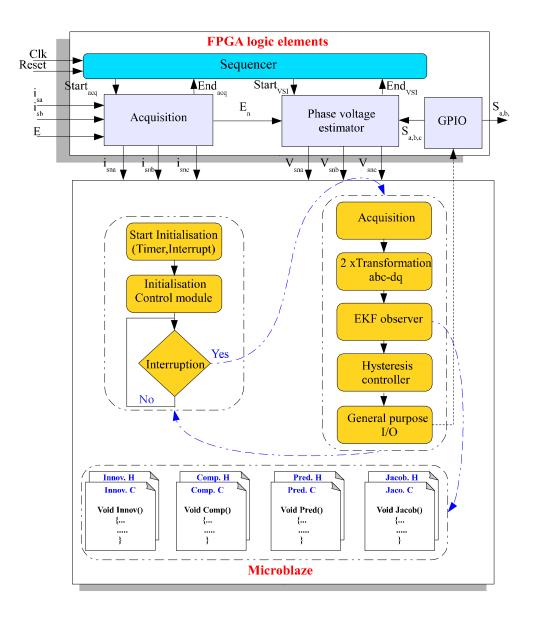

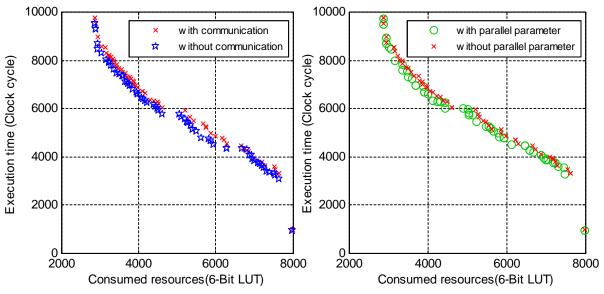

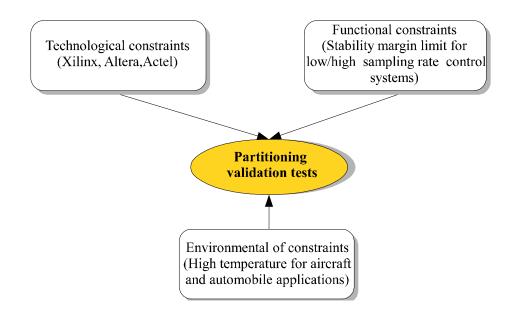

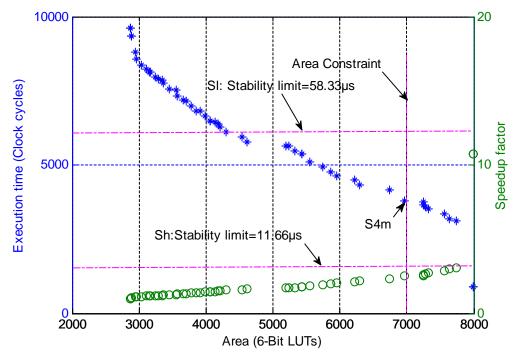

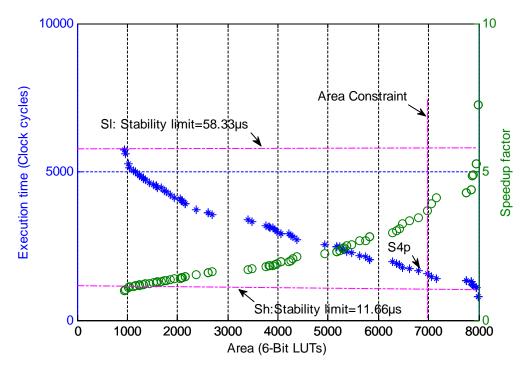

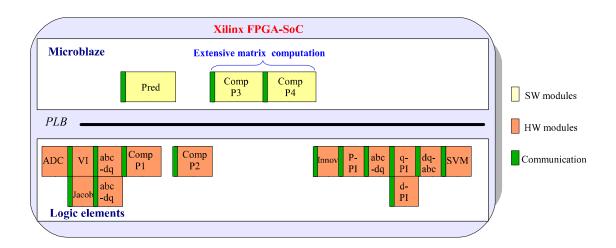

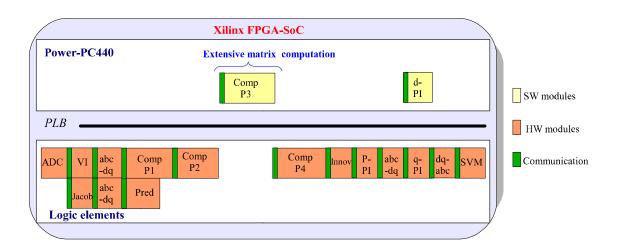

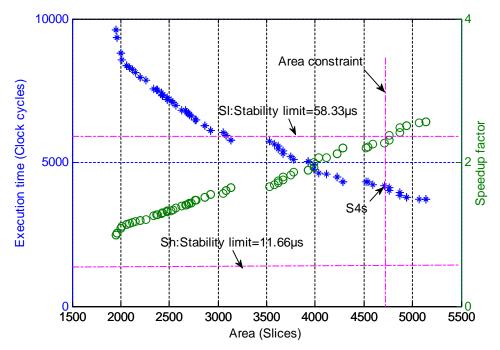

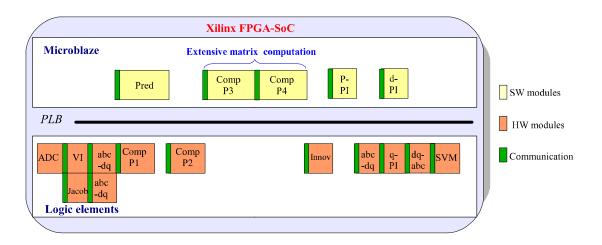

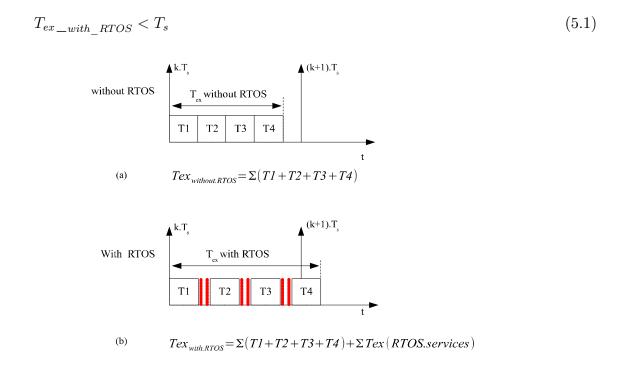

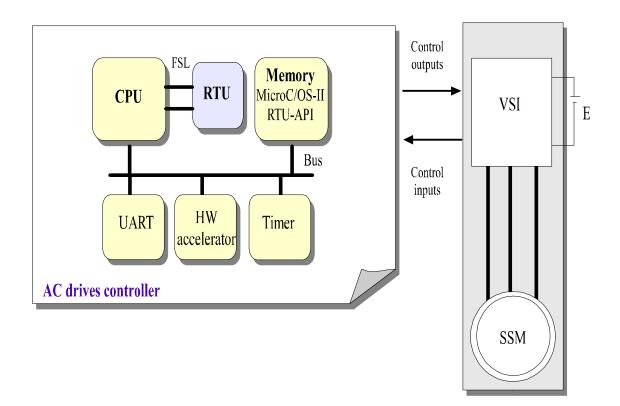

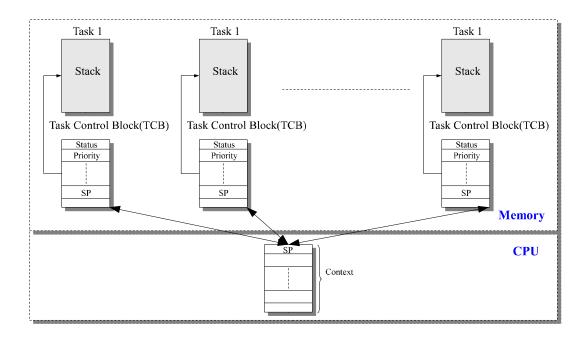

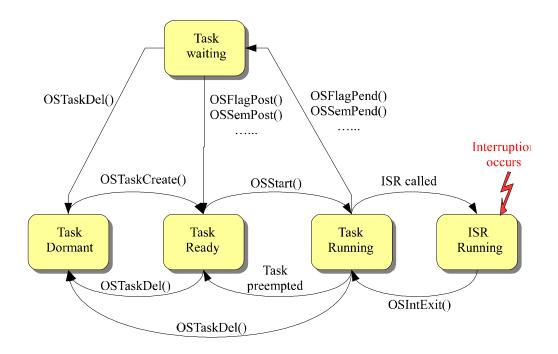

Figure 2.2: Design and validation methodology.