N° d'ordre: 4284

# THÈSE

#### PRÉSENTÉE A

## L'UNIVERSITÉ BORDEAUX 1

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGENIEUR

Par Raffaele Roberto SEVERINO

POUR OBTENIR LE GRADE DE

**DOCTEUR**

SPÉCIALITÉ: ELECTRONIQUE

### Design Methodology for Millimeter Wave Integrated Circuits: Application to SiGe BiCMOS LNAs

Soutenue le : 24 juin 2011

Après avis de :

MM. D. ZITO Professeur, University College Cork, Tyndall National Institute

S. MIRABBASI Professeur, University of British Columbia, Vancouver

Rapporteur Rapporteur

Devant la commission d'examen formée de :

MM. D. ZITO Professeur, University College Cork, Tyndall National Institute

S. MIRABBASI Professeur, University of British Columbia, Vancouver

D. BELOT Ingénieur, STMicroelectronics, Minatec, Grenoble

D. DUBUC Maitre de Conférences, LAAS, Toulouse

Y. DEVAL Professeur, ENSEIRB, Bordeaux

$E.\ KERHERVE\ Professeur,\ ENSEIRB,\ Bordeaux$

J-B. BEGUERET Professeur, Université de Bordeaux 1

T. TARIS Maître de Conférences, Université de Bordeaux 1

Rapporteur

Rapporteur

Examinateur

Examinateur

Président

Examinateur

Directeur de thèse

Co-Directeur de thèse

## **Table of Contents**

| In | ntroduction                                                                                                              | 5                    |

|----|--------------------------------------------------------------------------------------------------------------------------|----------------------|

| Cl | hapter 1 - Millimeter wave Integrated Circuits: Applications and Architectures                                           | 9                    |

|    | 1.0 Introduction                                                                                                         | 11                   |

|    | 1.1 Millimeter wave Applications at 60GHz                                                                                | 12                   |

|    | 1.1.1 Overview                                                                                                           | 12                   |

|    | 1.1.2 Standards and Regulations for 60GHz WPAN applications                                                              | 13                   |

|    | 1.2 Millimeter wave Automotive Radar sensors                                                                             | 18                   |

|    | 1.2.1 Overview                                                                                                           | 18                   |

|    | 1.2.2 Automotive Radar Regulation                                                                                        | 21                   |

|    | 1.2.3 VeLo Project                                                                                                       | 24                   |

|    | 1.3 Millimeter wave imaging in the 94GHz band                                                                            | 26                   |

|    | 1.3.1 Overview                                                                                                           | 26                   |

|    | 1.3.2 Direct detectors for Imaging systems                                                                               | 28                   |

|    | 1.4 Building blocks and design solutions for the implementation of millimeter wave systems                               |                      |

|    | 1.4.1 Possible architectures for integrated transceiver: fundamental concepts                                            |                      |

|    | 1.4.2 Low Noise Amplifier (LNA)                                                                                          |                      |

|    | 1.4.3 Mixer                                                                                                              |                      |

|    | 1.4.4 Frequency Synthesizer                                                                                              | 35                   |

|    |                                                                                                                          |                      |

|    | 1.4.5 Power Amplifier (PA)                                                                                               | 35                   |

|    | 1.4.5 Power Amplifier (PA)  1.5 Examples of millimeter wave integrated transceivers in CMOS and SiGe BiCMOS technologies | ;                    |

|    | 1.5 Examples of millimeter wave integrated transceivers in CMOS and SiGe BiCMOS                                          | 35                   |

|    | 1.5 Examples of millimeter wave integrated transceivers in CMOS and SiGe BiCMOS technologies                             | 35<br>42             |

| Cl | 1.5 Examples of millimeter wave integrated transceivers in CMOS and SiGe BiCMOS technologies                             | 35<br>42<br>45       |

| Cl | 1.5 Examples of millimeter wave integrated transceivers in CMOS and SiGe BiCMOS technologies                             | 35<br>42<br>45<br>49 |

|    | 2.2 The BiCMOS9MW technology                                             | 54  |

|----|--------------------------------------------------------------------------|-----|

|    | 2.2.1 General features of The BiCMOS9MW technology                       | 54  |

|    | 2.2.2 0.13μm BiCMOS Heterojunction Bipolar Transistor                    | 55  |

|    | 2.2.3 Models of the High Speed Heterojunction Bipolar Transistor         | 60  |

|    | 2.2.4 Corrections for transistor model                                   | 64  |

|    | 2.2.5 Transmission Lines                                                 | 65  |

|    | 2.2.6 RF Pads                                                            | 69  |

|    | 2.2.7 MIM Capacitors                                                     | 71  |

|    | 2.2.8 Resistors                                                          | 73  |

|    | 2.2.9 Lumped Inductors                                                   | 74  |

|    | 2.3 Lumped or Distributed Approach                                       | 76  |

|    | 2.4 Inductor design                                                      | 77  |

|    | 2.4.1 Design strategy                                                    | 77  |

|    | 2.4.2 Equivalent-circuit models for lumped inductors                     | 81  |

|    | 2.4.3 Overview of the design flow                                        | 84  |

|    | 2.4.4 Examples of inductor design                                        | 84  |

|    | 2.5 Interconnection modeling                                             | 87  |

|    | 2.6 Overview of the Design Flow for mm-Waves building blocks             | 88  |

|    | 2.7 Tips for measurement de-embedding                                    | 89  |

|    | 2.7.1 Open-source                                                        | 89  |

|    | 2.7.2 Split-thru                                                         | 90  |

|    | 2.7.3 Comparison between open-short and split-thru de-embedding          | 92  |

|    | 2.7.4 Contact resistance                                                 | 94  |

|    | 2.8 Conclusion                                                           | 97  |

|    | Bibliography                                                             | 99  |

|    | napter 3 - Millimeter Wave Low Noise Amplifiers: Design and Experimental | 4   |

| Ch | naracterization                                                          |     |

|    | 3.0 Introduction                                                         |     |

|    | 3.1 General guidelines for LNA design                                    |     |

|    | 3.1.1 Topology                                                           |     |

|    | 3.1.2 Cascode Amplifier with Intersgtage Matching                        | 108 |

| 3.1.3 Design strategy for Noise optimization                            | 111   |

|-------------------------------------------------------------------------|-------|

| 3.1.4 Matching of the real part of the Noise impedance                  | 113   |

| 3.1.5 Real impedance matching with inductive degeneration               | 115   |

| 3.1.6 Tuning of the imaginary part of the input and noise impedances    | . 117 |

| 3.1.7 Design of the output network                                      | . 119 |

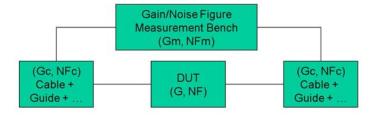

| 3.2 Experimental characterization for millimeter wave LNAs              | . 121 |

| 3.2.1 Small and large signal measurement                                | . 121 |

| 3.2.2 Measurement of Noise Figure                                       | 123   |

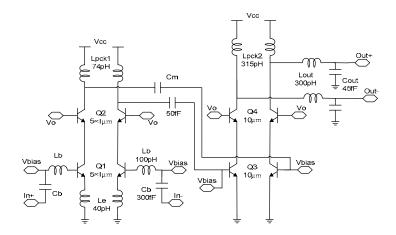

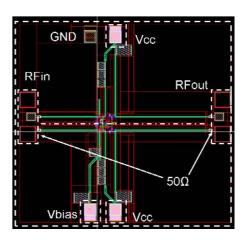

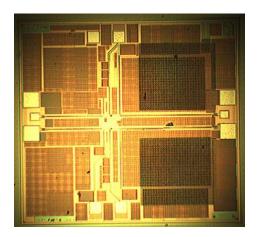

| 3.3 Two-stage cascode differential LNA for 60GHz WPAN                   | . 124 |

| 3.3.1 Theoretical design and circuit implementation                     | 124   |

| 3.3.2 Experimental Results                                              | 127   |

| 3.4 Two-stage LNA for 80GHz applications                                | 130   |

| 3.4.1 Theoretical design and circuit implementation                     | 131   |

| 3.4.2 Experimental Results                                              | 132   |

| 3.5 Single-stage LNA for imaging applications at 94GHz                  | . 134 |

| 3.5.1 Theoretical design and circuit implementation                     | 135   |

| 3.5.2 Experimental Results                                              | 136   |

| 3.6 Single-stage 80GHz LNA: Comparison between lumped and distributed   |       |

| implementations                                                         |       |

| 3.6.1 Theoretical design and circuit implementations                    |       |

| 3.6.2 Experimental Results                                              |       |

| 3.7 Comparison with the State of Art                                    |       |

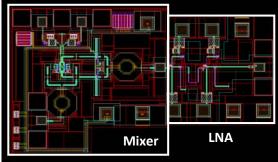

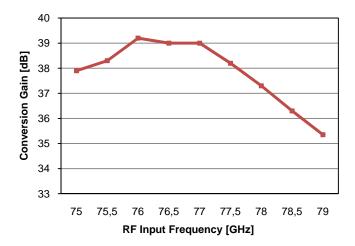

| 3.8 An application of a millimeter wave LNA: a 80GHz receiver Front-end | . 147 |

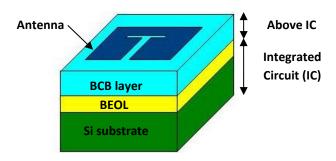

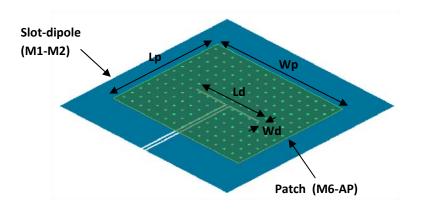

| 3.9 LNA and Antenna co-integration                                      | 152   |

| 3.10 Conclusion                                                         | . 154 |

| Bibliography                                                            | . 157 |

| Conclusion and Perspectives                                             | . 161 |

| Publications                                                            |       |

| Glossary                                                                | 169   |

| Annexe 1 - Equivalent Model of Lumped Inductors                         | . 175 |

| Annexe 2 - Definition of S parameters and reflection coefficients       | 179   |

| Annexe 3 - Definition of Noise parameters                                           | 183 |

|-------------------------------------------------------------------------------------|-----|

| Annexe 4 - Considerations on the effects of inductive degeneration on optimum noise |     |

| resistance                                                                          | 187 |

The development of microelectronic industry involves an incessant search for new technological applications capable to intensify the economic exploitation of existing market segments and to establish new business areas.

For this reason, the interest towards millimeter waves has rapidly increased during the last few years, leading to the development of a large number of potential applications in the millimeter wave band, such as WPANs and high data rate wireless communications at 60GHz, short and long range radar at 77-79GHz, and imaging systems at 94GHz.

Historically, the millimeter-waves market segment has been dominated since decades by the III-V semiconductors, thus relegating these applications into some niche market, because of the high manufacturing cost and reduced integration scale of the III-V solutions. Recently, improvements in silicon-based technologies have led to a significant extension of the upper frequency limit of silicon integrated devices. The very high frequency performances of silicon active devices (bipolar and CMOS) have dramatically increased, featuring both  $f_T$  and fmax close to or even higher than 200GHz. As a consequence, modern silicon technologies can now address the demand of low-cost and high-volume production of systems and circuits operating within the millimeter wave range.

However, even if the latest CMOS and BiCMOS technology nodes can support millimeter wave operation, nevertheless the augmentation of the operative frequencies and bandwidths entails considerable difficulties. The implementation of active and passive devices becomes more complex because the frequency augmentation unavoidably implies the degradation of device performances. In addition, the equivalent electromagnetic wavelength on silicon substrates at millimeter wave is comparable with the physical dimension of integrated circuits. Therefore, the influence of parasitics on the performance of intrinsic devices cannot be neglected, and a special effort is demanded in developing devices' models. Consequently, millimeter wave design still requires special techniques and methodologies to overcome a large number of constraints which appear along with the augmentation of the operative frequency.

The aim of this thesis is to define a design methodology for integrated circuits operating at millimeter wave and to provide an experimental validation of the methodology, as exhaustive as possible, focusing on the design of low-noise amplifiers (LNAs) as a case study.

The first chapter is dedicated to a brief description of the most important millimeter wave applications and standards. Also, several state-of-the-art architectures of millimeter wave building blocks and transceivers are briefly reviewed.

Chapter 2 reports a detailed study of all the key elements needed for successful design of millimeter wave integrated circuits based on the BiCMOS9MW technology by STMicroelectronics. Starting from a detailed insight on the design facilities provided by the technology, a complete design methodology is presented. Both the lumped and distributed design approaches are considered.

In chapter 3, the proposed methodology is applied to the practical case of LNAs design. Examples concerning the most common application standards are presented, at 60GHz, 80GHz and 94GHz. In particular, the design and the experimental characterization of a two-stage cascode 60GHz LNA dedicated to WPAN applications, of a two-stage LNA operating at 80GHz, and of a single-stage 94GHz amplifier for imaging applications are reported. Then a comparative analysis of lumped and

distributed approach is made, based on two different implementations of a single-stage 80GHz LNA using, respectively, distributed transmission lines and lumped inductors.

Finally, in the last part of the chapter, the design of an 80GHz front-end and the co-integration of an LNA with an integrated antenna are also considered, opening the way to the implementation a fully integrated receiver.

## Chapter 1

Millimeter Wave Integrated Circuits: Applications and Architectures

#### 1.0 Introduction

The expression *millimeter waves (mm-Waves or mmW)* designates a radio frequency band having a wavelength of ten to one millimeter.

According to the International Telecommunications Union (ITU) radio regulations resumed in Table 1, it corresponds to the region of extremely high frequency (EHF: 30GHz to 300GHz).

| Nr | Symbols | Designation              | Frequency Range   | Wavelength Range     |

|----|---------|--------------------------|-------------------|----------------------|

| 1  | ELF     | extremely low frequency  | 3Hz to 30Hz       | 100000km to 10000 km |

| 2  | SLF     | super low frequency      | 30Hz to 300Hz     | 10000km to 1000km    |

| 3  | ULF     | ultralow frequency       | 300Hz to 3000Hz   | 1000km to 100km      |

| 4  | VLF     | very low frequency       | 3kHz to 30kHz     | 100km to 10km        |

| 5  | LF      | low frequency            | 30kHz to 300kHz   | 10km to 1km          |

| 6  | MF      | medium frequency         | 300kHz to 3000kHz | 1km to 100m          |

| 7  | HF      | high frequency           | 3MHz to 30MHz     | 100m to 10m          |

| 8  | VHF     | very high frequency      | 30MHz to 300MHz   | 10m to 1m            |

| 9  | UHF     | ultrahigh frequency      | 300MHz to 3000MHz | 1m to 10cm           |

| 10 | SHF     | super high frequency     | 3GHz to 30GHz     | 10cm to 1cm          |

| 11 | EHF     | extremely high frequency | 30GHz to 300GHz   | 1cm to 1mm           |

Table 1. IUT Radio Bands.

In the context of microelectronics it is more useful to consider the wavelength in a silicon oxide layer that is roughly half the wavelength in open space, according to the well-known relation:

$$\lambda_{Ox} = \frac{1}{f\sqrt{\varepsilon_{Ox}\varepsilon_0\mu_0}} = \frac{1}{f\sqrt{\varepsilon_{Ox}\sqrt{\varepsilon_0\mu_0}}} = \frac{c}{f\sqrt{\varepsilon_{Ox}}} = \frac{\lambda_0}{\sqrt{\varepsilon_{Ox}}} \cong \frac{\lambda_0}{1.9}$$

where the relative permittivity of silicon oxide  $\varepsilon_{Ox}$  is assumed to be equal to 3.6 and frequency-independent.

A more appropriate placement of the millimeter wave band is therefore in the 15-158 GHz range. In particular, we will consider as millimeter waves the electromagnetic spectrum between 60 and 110GHz.

As a matter of fact, electronics at lower frequencies (at least up to 20-30GHz) can rely over the traditional radiofrequency design methods and techniques. On the contrary, as it will be explained in the next chapter, design of silicon-based integrated circuits operating in the 60-110GHz range, requires the development of a dedicated methodology capable to address the numerous difficulties emerging along with the frequency increase.

Very recently the same design methodology has been gradually extended to higher frequency known as sub-millimeter wave or Terahertz radiation, opening the way to the so-called Terahertz-electronics that however will not be considered in this thesis.

During the last few years, the interest towards millimeter waves has rapidly grown, leading to the development of a large number of potential applications. As well, the recent improvements in silicon-based technologies like CMOS and BiCMOS processes have made it possible to realize low-cost implementations of microelectronic systems operating in the millimeter wave band.

Without any pretention of being exhaustive, the next three sections give an overview of the most common applications in a millimeter wave technology such as WPANs and high data rate wireless communications at 60GHz, short and long range radar at 77-79GHz, and imaging systems at 94GHz. Then, in section 1.4, the main features and the most common parameters concerning the radio-frequency building blocks are briefly reviewed. Finally, some examples of integrated transceivers taken from the present-day state-of-the-art are briefly illustrated in section 1.5.

#### 1.1 Millimeter wave Applications at 60GHz

#### 1.1.1 Overview

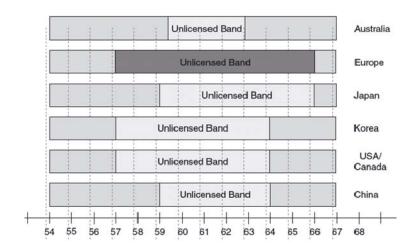

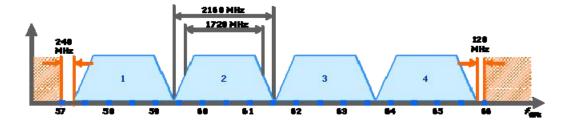

The 60GHz band [1]-[2] has attracted the interest of researchers in the past several years, as it offers ample and license-free bandwidth. This advantage becomes more evident when considering that the availability of about 7GHz of unlicensed bandwidth is guaranteed in many countries worldwide, as shown in Fig. 1. For example, the range from 57 to 64 GHz is currently available in the US, while 59 to 66 GHz are available in Japan. Furthermore 60GHz band is less restrict in terms of power limits when compared to other concurrent wideband systems, like ultra-wideband (UWB), for instance. These characteristics make 60GHz technology particularly suited for gigabit wireless applications that currently are technically constrained at lower frequency.

Fig. 1. Worldwide frequency allocation for 60 GHz band and operation.

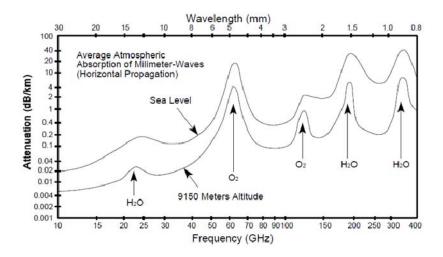

As depicted in Fig. 2, the atmospheric absorption presents a peak at 60GHz due to oxygen absorption that puts a severe limit on the distance that 60GHz transmissions can handle – at least in the case of low-power applications – limiting it to close-range communications. In home-space, however, oxygen absorption is not a big problem, so 60GHz is beginning to look like a useful way to provide dramatic speed-ups over traditional wireless local area networks (WLANs) and is particularly indicated for

wireless personal area networks (WPANs). A WPAN is designed to provide short-range (<10m), very-high-speed (>2Gb/s) multi-media data services to computer terminals and consumer appliances located in rooms, office space, "hot spots" and kiosks. Wireless PANs will provide higher data rates, and shorter range, than comparable WLANs but sufficient to cover the size of most offices, medium-size conference rooms, and rooms in personal home. Various electronic devices could be interconnected, including laptops, cameras, and monitors. Potential applications include wireless display, wireless docking station, and wireless streaming of data from one device to the other. A 60GHz link could be used to replace various cables used today in the office or home, including gigabit Ethernet (1Gbps), USB 2.0 (480Mbps), or IEEE 1394 (~800Mbps). Currently, the data rates of these connections have precluded wireless links, since they require so much bandwidth. While other wireless standards are evolving to address this market (802.11n and UWB), 60GHz is still a viable candidate.

Fig. 2. Atmospheric absorption of millimeter waves.

Besides oxygen absorption in open-space, different materials affect the propagation of 60GHz signals in different ways and, whereas plasterboard or drywall absorption is not much greater than in the case of 2.4GHz signals, other materials, on the contrary, cause a big fall-off in signal strength. Also human skin, for instance, absorbs 60GHz radiation pretty efficiently and crossing a link between a computer and a media player synchronized over a 60GHz system would break it.

To reduce the effect of absorption loss, many solutions such as directional antennas or beamforming techniques are currently investigated. If sufficient directionality is guaranteed in transmission, then atmospheric and material properties could also prove more of a benefit than a limitation, since they can prevent the signal from leaking into adjacent environment, reducing the risk of interference and enhancing security.

#### 1.1.2 Standards and Regulations for 60GHz WPAN applications

Several attempts of standardization have been recently proposed or are still in course of definition. For example, the IEEE 802.15 Task Group 3c is working since 2005 on the wireless personal area network (WPAN), leading to the definition of the IEEE 802.15.3c standard in September 2009 [3]-[4].

Besides, Wireless HD [5], the Wireless Gigabit Alliance (WiGig) [6], the IEEE 802.11ad working group [7] and the ECMA-387 [8] have been also making standardization efforts on the 60 GHz frequency band. A detailed description of these documents is beyond the interest of this text; however the most important features of the IEEE and the ECMA standards are briefly described hereafter.

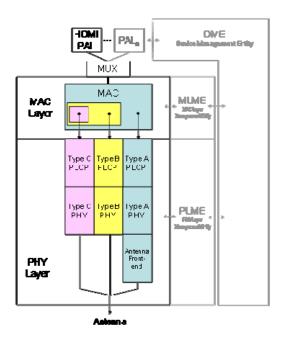

IEEE Std 802.15.3c is an amendment to IEEE Std 802.15.3 that defines an alternative physical layer (PHY) operating in the millimeter wave band and the necessary modifications to the medium access control (MAC) changes to support this PHY.

The PHY defines three operational modes as follows:

- Single carrier (SC) mode optimized for low power and low complexity.

- High-speed interface (HSI) mode optimized for low-latency bidirectional data transfer.

- Audio/video (AV) mode optimized for the delivery of uncompressed, high-definition video and audio.

For devices that implement the mm-Wave PHY, at least one of the three PHY modes is required. In addition, to promote coexistence and interoperability, a common mode signaling (CMS) is defined based on a low data rate SC PHY mode.

The single carrier mode in mm-Wave PHY (SC PHY) provides three classes of modulation and coding schemes targeting different wireless connectivity applications. As summarized in Table 2, Class 1 is specified to address the low-power low-cost mobile market while maintaining a relatively high data rate of up to 1.5Gb/s; Class 2 is specified to achieve data rates up to 3Gb/s; Class 3 is specified to support high performance applications with data rates in excess of 3Gb/s.

Table 2. Modulation and Coding Schemes Classes in the SC PHY.

| Class | Categorization               |  |

|-------|------------------------------|--|

| 1     | Data rates < 1.5Gb/s         |  |

| 2     | 1.5Gb/s < Data rates < 3Gb/s |  |

| 3     | Data rates > 3Gb/s           |  |

The SC PHY supports a wide range of modulations,  $\pi/2$  BPSK,  $\pi/2$  QPSK,  $\pi/2$  8-PSK,  $\pi/2$  16-QAM, precoded MSK, pre-coded GMSK, on-off keying (OOK), and dual alternate mark inversion (DAMI). It operates on four RF channels, as defined in Table 3. A compliant implementation shall support at least 1 channel from the channels allocated for operation by its corresponding regulatory body.

Table 3. RF Channels for millimeter wave PHY.

| Channel ID | Start Freq [GHz] | Center Freq [GHz] | Stop Freq [GHz] |

|------------|------------------|-------------------|-----------------|

| 1          | 57.24            | 58.32             | 59.40           |

| 2          | 59.40            | 60.48             | 61.56           |

| 3          | 61.56            | 62.64             | 63.72           |

| 4          | 63.72            | 64.80             | 65.88           |

The high speed interface mode of mm-Wave PHY (HSI PHY) is designed for devices with low-latency, bidirectional high-speed data and uses orthogonal frequency division multiplexing (OFDM). HSI PHY supports a variety of modulation and coding schemes (MCSs) using different frequency-domain spreading factors, modulations, and LDPC block codes.

The Audio/Visual (AV) PHY is implemented with two PHY modes, the high-rate PHY (HRP) and low-rate PHY (LRP), both of which use orthogonal frequency domain multiplexing (OFDM). The data rates supported by the HRP and the LRP are defined in Table 4 and Table 5, respectively.

Table 4. AV HRP data rates.

| HRP mode index | Modulation | Data rate [Gb/s] |

|----------------|------------|------------------|

| 0              | QPSK       | 0.952            |

| 1              | QPSK       | 1.904            |

| 2              | 16-QAM     | 3.807            |

| 3              | QPSK       | 1.904            |

| 4              | 16-QAM     | 3.807            |

| 5              | QPSK       | 0.952            |

| 6              | QPSK       | 1.904            |

Table 5. AV LRP data rates.

| LRP mode index | Modulation | Data rate [Mb/s] |

|----------------|------------|------------------|

| 0              |            | 2.5              |

| 1              | BPSK       | 3.8              |

| 2              |            | 5.1              |

| 3              |            | 10.2             |

Different PHYs are a result of demands of different market segments. For example, one usage model is for kiosk applications. This usage model requires 1.5Gb/s at a 1m range. The SC-PHY can provide such a data rate at that short range with less complexity thus lower cost than an OFDM PHY. Another usage model is required by the streaming of uncompressed video. Due to the nature of uncompressed video signals, a special PHY, the AV PHY, was selected to provide high throughput. A third usage model involves an ad-hoc system to connect computers and devices around a conference table. In this usage model, all of the devices in the WPAN will have bidirectional, NLOS high speed, low-latency communication, which is provided for by the HSI PHY.

Besides the suggestions for MAC and physical level, IEEE standard specifies also an optional beam forming protocol that can support a multitude of antenna configurations such as single antenna element, sectored antennas, switched antennas, and one-dimensional (1-D) and two-dimensional (2-D) beam forming antenna arrays.

The ECMA 387 standard defines three device types as follows:

- A type A device offers video streaming and WPAN applications in 10m range line of sight/not line of sight multipath environments. It uses high gain trainable antennas. This device type is considered as the 'high end' high performance device.

- A second type, type B device offers video and data applications over shorter range (1-3 m) point to point line of sight links with non-trainable antennas. It is considered as the 'economy' device and trades off range and not line of sight performance in favor of low cost implementation and low power consumption.

- The third type, type C device is positioned to support data only applications over point to point line of sight links at less than 1m range with non-trainable antennas and no QoS guaranties. This type is considered as 'bottom end' device providing simpler implementation, lowest cost and lowest power consumption.

The A, B, and C devices can interoperate with their own types independently and can coexist and interoperate with the other types leading to the implementation of heterogeneous network solution that provides interoperability between all device types. As depicted in Fig. 3, each one of the three device types corresponds to a different organization of the PHY layer. The three PHYs converge into a single MAC level based on the ECMA-368 standard, with the necessary changes to support directional communication in 60GHz band.

Fig. 3. Protocol Structure of ECMA standard.

The Type A PHY includes two general transmission schemes, namely Single Carrier Block Transmission (SCBT), also known as Single Carrier with Cyclic Prefix, and OFDM; the Type B PHY has been designed using a simplified single carrier transmission scheme with a common beaconing mode based on differentially encoded BPSK modulation (DBPSK), thus allowing for both simple coherent and non-coherent demodulation and minimizing the implementation overhead to support interoperability with type A devices; the Type C PHY uses the simplest single carrier transmission scheme based on the Amplitude-Shift-Keying (ASK) modulation scheme.

The standard specifies four frequency channels each with a symbol rate of 1.728Giga-Symbols/second and with a separation of 2.160GHz, as suggested in Fig. 4. All device types follow the same frequency plan.

Fig. 4. Frequency plan of ECMA standard.

European regulation of WLAN and WPAN system operating in the 60GHz band is provided by the European Telecommunications Standards Institute (ETSI). The technical characteristics of these applications are described in [9] and the specific technical requirements are defined in [10]. The most important features can be summarized as follows:

- frequency band is defined from 57 to 66 GHz;

- the maximum spectral power density shall be limited to 13dBm/MHz by indoor usage and to -2dBm/MHz by indoor/outdoor;

- the maximum output power level (effective isotropic radiated power, EIRP) shall be limited to 40dBm by indoor usage and to 25dBm by indoor/outdoor;

- the limit level of unwanted emissions in the spurious domain for transmitter are reported in Table 6 (measured with OdBi antenna gain);

- the limit level of unwanted emissions in the spurious domain for receiver are reported in Table 7 (measured with 0dBi antenna gain);

- the use of an integral antenna (that is an antenna designed as a fixed part of the equipment, without the use of an external connector and that, therefore, cannot be disconnected from the equipment by a user with the intent to connect another antenna) is required, to provide interference protection;

- a medium access protocol shall be implemented by the equipment and shall be active under all circumstances, in order to facilitate spectrum sharing with other devices in the wireless network.

Table 6. Transmitter spurious emissions.

| Frequency band  | Measurement bandwidth | Field Strenght at 3 m (dBµV/m) |

|-----------------|-----------------------|--------------------------------|

| 30MHz to 1GHz   | 100kHz                | 59                             |

| 1GHz to 132 GHz | 1MHz                  | 65                             |

Table 7. Receiver spurious emissions.

| Frequency band  | Measurement bandwidth | Field Strenght at 3 m (dBμV/m) |

|-----------------|-----------------------|--------------------------------|

| 30MHz to 1GHz   | 100kHz                | 38                             |

| 1GHz to 132 GHz | 1MHz                  | 48                             |

#### 1.2 Millimeter wave Automotive Radar sensors

#### 1.2.1 Overview

The first experimental applications of radar in the automotive industry date back to the 1950s and yet in 1970s automotive radars were the object of systematic investigations [11]-[12].

Years after years, safety has been one of the main concerns in the development of car industry, leading to several structural improvements capable to reduce the consequences of accidents on the driver and the passengers. In such a context, the introduction of radars represents a disruptive event, focusing on accident avoidance and prevention that, undeniably, are preferred to any system of crash protection.

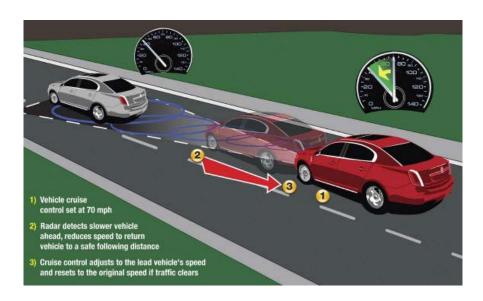

Nowadays, the so-called autonomous or adaptive cruise control (ACC) is probably the most common application of automotive radar and is used to assist the driver and to augment its comfort.

Fig. 5. Schematic example of Adaptive Cruise Control (ACC) operation.

Practically speaking, a radar sensor is mounted behind the front bumper of a vehicle at a height of less than 1m, where it is able to interrogate the road ahead and the adjacent traffic lanes forward of the vehicle's location. Using this radar, the control system within the vehicle adjusts the cruise speed in response to a slower vehicle in a merging lane, or when following a vehicle in the same lane, in order to maintain the driver's selected minimum separation distance behind the other vehicle. An ACC system can constantly provide the driver with information about traffic situation in the environment, making driving less strenuous, especially in flowing traffic and in critical context like on motorways or dual carriageways.

ACC today uses long-range radar (LRR) operating between 76GHz and 77GHz with a maximum bandwidth of 1GHz. It uses distance scanning, which requires an operating range of approximately 150m and is used at vehicle velocities not below 30km/h. One or multiple narrow lobes control or

scan the driving path in front of the car to determine the distance to the vehicle driving ahead for maintaining a constant minimum safety distance.

In 1999 Mercedes-Benz has been the first car manufacturer who introduced radar-based ACC system in its S-class vehicles [13]. Since then, radar based ACC systems are available in many high and mid-class models such as BMW 7 series, Jaguar (XKR, XK6), Cadillac (STS, XLR), Audi A8, VW Phaeton, Mercedes E, CL, CLK, SL class, BMW 5 and 6 series, Audi A6, Nissan (Cima, Primera), Toyota (Harrier, Celsior), Lexus (LS, GS), Honda (Accord, Inspire, Odyssey) and their functionality have been gradually extended, including also pre-crash sensing and collision mitigation.

Besides radar-based equipments, also competing and complementing technologies in vehicular surround sensing and surveillance like Lidar, ultrasonics, and video-cameras have been tested since the first 1990s to implement parking aid, collision warning, and ACC as well. However, radar seems still to be the key technology for driver assistance and safety applications, due to its inherent advantages like weather independence and direct acquisition of range and velocity especially when compared to alternative sensors like video, laser, and ultrasonics.

Fig. 6. DISTRONIC radar sensor mounted on Mercedes Benz S-class vehicles.

More recently, in 2003 – whereas European car manufacturers offer radar systems only for ACC systems so far – their Japanese competitors Honda and Toyota introduced an active brake assist for collision mitigation (in addition to ACC) based on 77GHz long range radar (LRR) technology. In contrast to the only smooth deceleration capability of an ACC system (because ACC is only marketed as a comfort feature), the active brake assist provides much higher braking forces for deceleration, when a threatening situation is identified and the driver starts braking but maybe not as strong as it would be necessary to avoid a crash. This shows the trend from "comfort only" functions to active safety systems with radar sensing technologies that serve both the comfort and the safety domain.

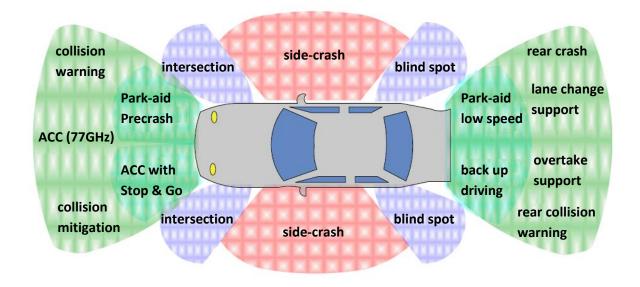

As a matter of fact, car companies and suppliers are currently working on the development of the next generations of LLR at 77GHz that will show improvements with respect to maximum and minimum range, wider field of view, improved range and angular resolution and accuracy, self alignment and blockage detection capability. In addition to forward-looking LRR, ultra-wideband (UWB) short range radar (SRR) sensors with coverage up to 30m are under development for a variety of further applications that will result in significant improvements of road safety.

Short range radar and ultra-wideband sensors can enable a variety of applications such as:

- Support of ACC with Stop&Go functionality

- Collision warning

- Collision mitigation

- Blind spot monitoring

- Parking aid

- Lane change assistant

- Rear crash collision warning

LRR and SRR devices can be used to combine their functionalities creating a protection wall all around the vehicle that is referred to in the literature as a "safety belt" for cars.

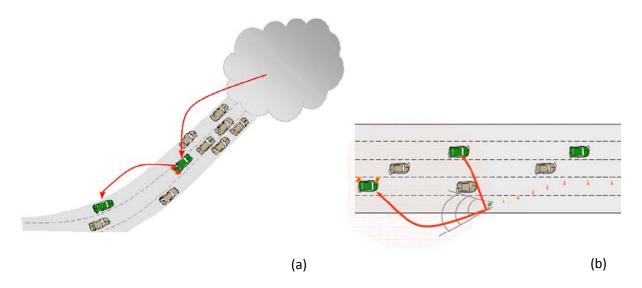

Fig. 7. Possible applications for automotive radars.

Beside LRR and SRR systems, a complementary branch of potential applications of millimeter wave technology to the automotive industry is given by the next-generation road vehicle communication. Many companies are currently working on the implementation of millimeter wave sensors capable to support inter-vehicle (IVC) and/or vehicle to roadside (and roadside to vehicle) communication (RVC). Next-generation cars will be able to exchange data – concerning, for example, their relative position or information and warning about weather and traffic status – with the surrounding vehicles and with beacons placed on the roadside at regular intervals along all inter-urban trunk routes and at strategic location (e.g. junctions) on more minor roads and in urban areas.

A huge number of applications of inter-vehicle and roadside to vehicle communication can be realized and are investigated by various project and groups; some examples are:

- Traffic information

- Collision avoidance

- Work zone safety warning

- Vehicle and cargo tracking

- Electronic license plate

- Repair-service record

- Parking, fuel, or fast food payment

- Disaster and emergency warning and control

More in general, IVC and RVC systems can be considered as part of a wider context, concerning the so-called Intelligent Transportation Systems (ITS) which represent the application of information and communications technology to transport infrastructure and vehicles, in an effort to manage factors that typically are at odds with each other, such as vehicles, loads, and routes to improve safety and reduce vehicle wear, transportation times, and fuel consumption.

Fig. 8. An example of IVC: the alarm for an accident is transmitted from a vehicle to another (a). An example of RVC: a warning revealing the presence of a work zone is transmitted to transiting vehicles (b).

An exhaustive description of all the potential applications of millimeter wave to the automotive industry is beyond the aim of this paragraph. Nevertheless, in conclusion of this brief overview, it is important to remark that the applications currently available, as the examples discussed here above, are substantially based on compound-semiconductors technologies. The considerably elevated cost of these technologies has therefore prevented the large diffusion of automotive radar equipments so far, relegating them to the high and mid-class market segments. Moreover, in the particular case of inter-vehicle communication, implementation cost is a concern, as it prevents an adequate diffusion of inter-communicating devices. Nowadays, thanks to the recent improvements in silicon-based technologies it is possible to realize low-cost and high-volume production of systems and circuits for automotive radar operating at millimeter wave frequencies.

#### 1.2.2 Automotive Radar Regulation

The regulation activity for automotive radar started already in the 90s with the allocation of the 76-77 GHz band for LRR systems. Then in 2001, the Federal Communications Commission (FCC) started the regulation for 24GHz SRR sensors in the US, setting their operation in the range of 22-29 GHz with a maximum mean power density of -41.3dBm/MHz, using directional antennas on terrestrial

transportation vehicles and requiring that the center frequency of the emission and the frequency at which the highest radiated emission occurs are higher than 24.075GHz.

Almost at the same time, more than 30 mainly European car manufacturers and suppliers founded the Short range Automotive Radar frequency Allocation consortium (SARA) with the objective to support UWB regulation in the 24GHz band for the European market. The use of the 21.65-26.65 GHz range was adopted by the European Commission for UWB SRR for the short-term period from 2005 to 2022. As a long term solution, in order to avoid interference with other 24GHz communications system, the 77 – 81 GHz band was allocated and made available since 2005.

The current European regulation for automotive radar is reported in the European Telecommunications Standards Institute (ETSI) standard documentation [14]-[17]. The functionality and the technical requirements, as well as the relative measurement conditions, of 76-77 GHz radar are set in [14] and can be resumed as:

- the permitted range of operating frequencies for intentional emissions shall be from 76GHz to 77GHz;

- the transmitted power for equipment with fixed beam antennas measured as mean power (EIRP) shall be less than 50dBm for system others than pulsed Doppler radar (Class 1) and less than 23.5dBm for pulsed Doppler radar only (Class 2);

- the transmitted power for equipment with fixed beam antennas measured as peak power (EIRP) shall be less than 55dBm;

- the transmitted power for equipment with steerable antennas shall be less than the limits shown in Table 8;

- the mean power density radiated outside the 76GHz to 77GHz band shall not exceed 0dVm/MHz;

- for the transmitter, the effective radiated power density of any radiated spurious emission shall not exceed the values given in Table 9 and shall be in accordance to CEPT/ERC/Recommendation 74-01;

- for the receiver, the maximum equivalent isotropically radiated power (max. EIRP) of any spurious emission outside the permitted range of frequencies shall not exceed 2nW ( $\approx$  -57dBm) in the frequency range 25MHz  $\leq$  f  $\leq$  1GHz and shall not exceed 20nW ( $\approx$  -47dBm) on frequencies in the range 1GHz < f  $\leq$  73,5GHz and 79,5GHz < f  $\leq$  100GHz in accordance to CEPT/ERC/Recommendation 74-01.

Table 8. Limits for transmitted power (steerable antenna). t is the largest dwell time<sup>1</sup> at any angle. D is the ratio of the area of the beam to the total area scanned by the antenna; the power is averaged across one antenna cycle; as D is smaller than 1, the log(D) is negative and leads to a reduction of the 55dBm value.

|                                                | Class 1                                                       |              | Class 2                                                         |              |

|------------------------------------------------|---------------------------------------------------------------|--------------|-----------------------------------------------------------------|--------------|

| Maximum antenna signal dwell time <sup>1</sup> | t < 100ms                                                     | t ><br>100ms | t < 100ms                                                       | t ><br>100ms |

| Mean Power (EIRP)                              | [55dBm + 10 log(D)]<br>or 50dBm (whichever is<br>the smaller) | 50dBm        | [55dBm + 10 log(D)]<br>or 23.5dBm (whichever<br>is the smaller) | 23.5dBm      |

| Peak Power (EIRP)                              | 55dBm                                                         | 55dBm        | 55dBm                                                           | 55dBm        |

Table 9. Limits of radiated spurious emissions.

| Frequency range [MHz]                                                                                                      | Limit values for spurious radiation |  |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|

| 47 to 74                                                                                                                   | -54dBm/100kHz                       |  |

| 87.5 to 118                                                                                                                | -54dBm/100kHz                       |  |

| 174 to 230                                                                                                                 | -54dBm/100kHz                       |  |

| 470 to 862                                                                                                                 | -54dBm/100kHz                       |  |

| otherwise in band 30 to 1000                                                                                               | -36dBm/100kHz                       |  |

| 1000 to 25000                                                                                                              | -30dBm/MHz                          |  |

| 25000 to 40000                                                                                                             | -30dBm/MHz                          |  |

| 40000 to 100000 (not applicable when the permitted range of frequencies from 76GHz to 77GHz and in the out of band region) | -30dBm/MHz                          |  |

In a similar way [15] fixes the technical requirements of SRR receiver, transmitter and integrated transceiver operating in the 22-26.65 GHz band, whereas the functionalities and the technical characteristics of SRR devices operating in the 77-81 GHz frequency range are discussed in detail in [16]. Even if an exhaustive report of these data is obviously beyond the aim of this text, it can be interesting to underline the main features of the 79GHz SRR devices as set by [16] that can be resumed as follows:

- SRR units operate in the 77-81 GHz band;

- operating range can vary from 0 to 30m approximately;

- a precise speed measurement is allowed, with help of a continuous wave (CW) Doppler emission and this speed measurement mode is combined with wideband signals to provide also precise radial range information of objects with a high range separation in order of approximately 5cm to 10cm;

- to obtain the required resolution, the SRR needs a large bandwidth of 4GHz for an accurate measurement of the range;

- several wideband modulation technologies are suggested (eventually combined in hybrid concepts):

23

<sup>&</sup>lt;sup>1</sup> The dwell time is the accumulated amount of transmission time of uninterrupted continuous transmission within a single given frequency channel and within one channel repetition interval.

**Pulse Modulation**

Frequency Hopping Spread Spectrum (FHSS)

Binary Phase Shift Keying (BPSK)

Pulsed Frequency Modulated Continuous Wave (FMCW)

- the peak power limit for the SRR allocation from 77GHz to 81GHz is required to be from 46,2 up to 55 dBm to achieve road safety goals (power levels required for SRR operation are listed in table 10).

Table 10. Overview of SRR and LRR parameters defined by ETSI [16].

|                                               | CDD             | LRR       |         |

|-----------------------------------------------|-----------------|-----------|---------|

|                                               | SRR             | FMCW      | Pulsed  |

| Frequency                                     | 77-81 GHz       | 76-77 GHz |         |

| Worst Case Mean EIRP Spectral Density @ 79GHz | < -15dBm/MHz to |           |         |

| Worst case Mean EIRP Spectral Density @ 790H2 | -3dBm/MHz       |           |         |

| Mean Power                                    | 18-30 dBm       | 50dBm     | 23.5dBm |

| Worst Case Peak EIRP @ 79GHz                  | 46.2-55 dBm     | 55dBm     |         |

| Operating Distance                            | 30m             | 150m      |         |

Beside LRR and SRR in the 79GHz band, ETSI provides also a preliminary regulation of ITS equipments for IVC and RVC, setting their operational bandwidth in the 63-64 GHz range [17].

#### 1.2.3 VeLo Project

The European Commission has adopted a policy goal to reduce road fatalities in Europe by 50% by 2010. The objective and focus of "The EC Approach to Road Safety and Intelligent Transport Systems (ITS)" are defined as to "Improve Safety, Security, Comfort and Efficiency in all Transport modes" and "Focusing on Advanced Pilot/Driver Assistance Systems".

European industry responded to these goals and, in order to promote the development of the necessary silicon technology, a first joint research project on "Automotive high frequency electronics - KOKON" was started in September 2004, funded by the German Ministry of Education and Research (BMBF), putting together two semiconductor companies (Atmel and Infineon), two automotive radar sensor manufacturers (Bosch and ContiTemic), and one automotive manufacturer (DaimlerChrysler), supported by institutes and universities [18]. The KOKON project investigated the feasibility of 79GHz UWB SRR and of 76.5GHz advanced LRR on silicon-germanium heterojunction bipolar transistor (SiGe HBT) technology that was identified as the best-suited for low cost solutions in the automotive radar context.

In 2006, the French National Research Agency (ANR) launched a new research project focused on millimeter wave automotive radar known as "Communication Inter Véhicules et Localisation Relative Précise en gamme millimétrique à 79GHz - VeLo".

Several French laboratories (CEA-Leti, IEMN, IMS, Lab-STICC, and LAAS) are involved in the project as well as the semiconductor company ST Microelectronics, the automotive manufacturer Autocruise, and the French National Institute for the Research on Transports and Transport Security (INRETS).

The aim of the project is the development of a radar sensor completely integrated on a silicon-based technology capable to support millimeter wave operation.

According to the definition given in the project documentation, the VeLo sensor should operate as an ultra-large band (ULB) SRR in the range of 77-81 GHz, providing a precise speed measurement based on Doppler emission, combined with a precise radial range detection of objects with a resolution between 5cm and 10cm; as a third function, the SRR should provide a lateral detection of a 1m<sup>2</sup> target at a distance of 30m, with a spatial resolution of 5cm.

At the same time, it should support also inter-vehicle communication, establishing a link with the surrounding vehicles and detecting and constantly monitoring their relative position. A vehicle equipped with a VeLo sensor will therefore analyze the position of other vehicles in the environment considering both other radar-equipped vehicles and passive ones. Furthermore, to complete its perception of the environment, it will estimate its own absolute position on the basis of the localization data collected by surrounding vehicles and supplied by a satellite navigation system.

Generally speaking, the final target of the project is to give a practical demonstration of the feasibility of a millimeter wave integrated device capable to operate simultaneously as short range radar and as inter-vehicle communication system.

Integration of the complete device in a silicon-based technology is a key element since, as already explained in the previous paragraphs, the main trend in automotive applications of millimeter wave technology is to provide low-cost solutions capable of supporting high-volume production.

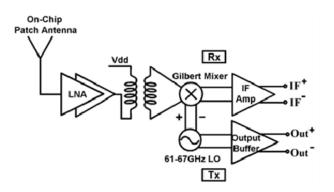

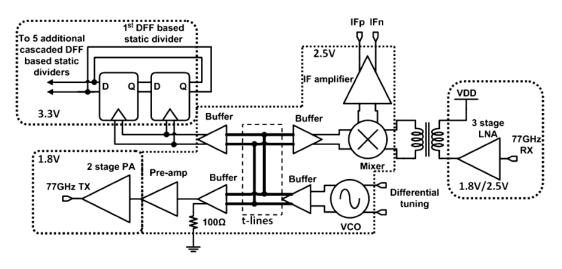

The proposed technology in the VeLo context is the BiCMOS9MW from ST Microelectronics that provides SiGe HBTs with maximum transistor  $f_T$  and fmax higher than 200GHz. Therefore, from the specific point of view of millimeter wave integrated circuits design, the main goal of the project is to demonstrate the feasibility of a complete receiver front-end (LNA, Mixer, and VCO) and of a power amplifier in the BiCMOS9MW technology. A first solution takes also into account the co-integration of the transmitting antenna with the power amplifier and of the receiving antenna with the receiver front-end leading to a complete system on chip (SoC) implementation. An alternative solution requires the implementation of the antennas as distinct modules on a common substrate, thus avoiding the difficulties related to antenna integration at millimeter wave frequencies.

A summary of the preliminary specifications given for the main building blocks is reported in Table 11 [19]. The VeLo project was concluded at the end of 2010 and our work is a part of it. The design of an 80GHz LNA that can respond to the project requirements is described in chapter 3. The main issues concerning the co-integration of the LNA and the Rx antenna, as well as the design of the receiver front-end are also discussed in chapter 3.

Table 11. Preliminary specifications of the VeLo Project (differential architecture) [19].

|                 | Low Noise<br>Amplifier | Down-converter<br>Mixer | Local oscillator                                                          | Power<br>Amplifier | Antenna<br>(Rx/Tx) |

|-----------------|------------------------|-------------------------|---------------------------------------------------------------------------|--------------------|--------------------|

| Freq            | 79GHz                  | 79GHz                   | 79GHz                                                                     | 79GHz              | 79GHz              |

| Gain            | 14.4dB                 | 11.5dB                  |                                                                           | 15dB               | 13dBi              |

| Noise Figure    | 6.5dB                  | 15dB DSB                |                                                                           |                    |                    |

| S11             | -10dB                  | -10dB                   | -15dB                                                                     |                    |                    |

| S22             | -15dB                  | -15dB                   |                                                                           | -10dB              |                    |

| IIP1dB          | -29.6dBm               | -27.6dBm                |                                                                           | 15dBm              |                    |

| IIP3            | -20dBm                 | -18dBm                  |                                                                           | 25dBm              |                    |

| Output<br>Power |                        | 0dBm LO                 | 3dBm                                                                      | 15dBm Min          |                    |

| Phase Noise     |                        |                         | -79dBc/Hz at<br>50kHz<br>-105dBc/Hz at<br>1MHz<br>-120dBc/Hz at<br>5.6MHz |                    |                    |

| Directivity     |                        |                         |                                                                           |                    | 19.6dBi            |

| Efficiency      |                        |                         |                                                                           |                    | 22%                |

| Insertion       |                        |                         |                                                                           |                    | -25dB              |

| Loss            |                        |                         |                                                                           |                    | -23UD              |

| LO/RF           |                        | 57dB                    |                                                                           |                    |                    |

| Isolation       |                        | 3700                    |                                                                           |                    |                    |

#### 1.3 Millimeter wave imaging in the 94GHz band

#### 1.3.1 Overview

The upper portion of the millimeter wave spectrum has been traditionally exploited for applications in the field of astronomy. Recently, further improvements of the related technology have turned the interest of industry on the development of terrestrial applications based on millimeter wave imaging [20]-[22].

As a matter of fact, the property of millimeter wave imaging systems to see through materials that are opaque to more conventional imaging wavebands (visible, IR and UV) makes them remarkably useful for many scientific and industrial applications.

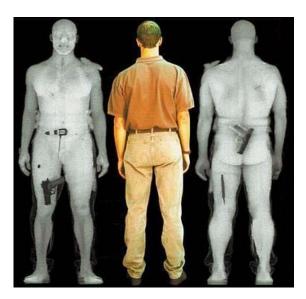

In particular, millimeter waves can readily penetrate common clothing materials and are reflected from the human body and any concealed items. For this reason they can be efficiently used in the field of security and defense, for the detection of concealed weapons or explosives. Furthermore, since millimeter wave imaging uses low-power and not-ionizing radiations, it results to be safer when compared to concurrent technologies based on X-rays and is better suited for the implementation of body scanner used for example for airport security screening. In such a context, it is possible to reveal not only weapons and explosives, but also any object hidden on the body, like drugs and

contraband stuff. The personal scanner uses harmless coherent radar waves from a millimeter wave antenna array to illuminate the person under surveillance. Then the reflected signal from the body or from any object on the body is collected by the array and processed to form high-resolution three-dimensional images like that of Fig. 9.

Fig. 9. An example of body scanner operation based on millimeter waves.

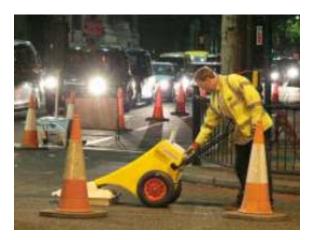

Following a similar approach it is possible to realize many other applications of millimeter wave as ground penetrating radar (GPR) imaging, and wall probing systems like inner-wall imaging, throughwall imaging, through-concrete imaging.

Ground-penetrating radar (GPR) is a geophysical method that uses radar pulses to image the subsurface and detects the reflected signals from subsurface structures. GPR can be used in a variety of media, including rock, soil, ice, fresh water, pavements and structures. It can detect hidden objects, changes in material, and voids and cracks, without drilling, probing, or digging. The applications of GPR imaging cover a large number of fields as engineering, where it is used for non-destructive testing of structures and pavements, for example to map defects such as voids, moisture and cracking or to determine pavement type and thickness in the context of highway and airport runway inspection without traffic interruption; archeology, where it is used to map archeological structures and sites; military, for landmine detection; geophysical, for ground investigation in order to trace foundations and other obstructions, and to locate geological hazards that may pose a risk to construction activity or human habitation; or environmental protection, where GPR can be used to define landfills, contaminant plumes, and remediation sites.

Also wall probing systems can be useful for non-destructive structural test, to map buried utility cables, pipes and ducts or to measure the depth to buried utilities, so making maintenance interventions simpler, reducing costs and the risk of accidental damage to power and gas lines.

Fig. 10. Applications of GPR. Surface mapping of an underground storage tank (left). Roadway inspection (right).

Many of the applications discussed so far are currently realized using concurrent technologies (like UWB in the range from 30 MHz to 12.4 GHz in the case of GPR). Nevertheless, all of them can be potentially supported by millimeter wave systems operating in the frequency range around 94GHz.

The importance of 94GHz band is given by the fact that the atmospheric absorption reaches a minimum level precisely at 94GHz, as depicted in Fig. 2.

Besides imaging, millimeter wave technology can be applied also to the implementation of a cloud profiling radar (CPR) employed in satellite missions to investigate cloud structure and its variability. By using the 94GHz frequency range it is possible to penetrate ice clouds with negligible attenuation and obtain a profile of cloud characteristics.

Moreover, the capability of 94GHz signals to propagate through fog, clouds, rain, and even sandstorms with irrelevant attenuation can be exploited to design millimeter wave sensor capable to improve the aviation safety and facilitate airport ground control in extremely poor visibility.

#### 1.3.2 Direct detectors for Imaging systems

In general, imaging systems can be divided into two categories: active and passive.

Passive (known also as radiometric) imaging is based on the principle that any object not at the absolute zero temperature emits electromagnetic energy at all wavelengths. This energy can be detected by an appropriate receiver and can be used to produce an image. It is the preferred method for outdoor stand-off detection and for systems working at distances of a few meters to several kilometers. Such imagers rely on temperature differences of the target, where the cold sky helps to improve the image contrast. The main benefit is that no high-power source is needed to illuminate the scene. Some problems associated with active illumination, such as poor visibility of metal surfaces due to specular reflections, are also eliminated. As a drawback, due to the lack of phase information in the received signal, the ability to perform radar operation is limited.

Active imaging systems use dedicated millimeter wave sources that project a narrow beam of energy against the target in order to achieve a higher contrast or better signal to noise ratio. It distinguishes

itself from passive imaging, because it often detects the radiation as electric field amplitude and phase in a way similar to radar applications. This enables imaging with three-dimensional and tomographical content and enhances the object detection capabilities.

In the case of active imaging systems, receivers can be implemented as direct detectors or, alternatively, as indirect (coherent) receivers which are commonly based on the heterodyne architecture. Passive imaging, on the contrary, commonly uses direct detectors.

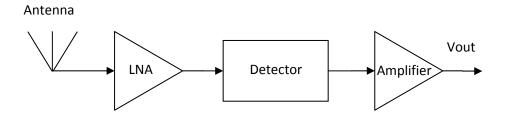

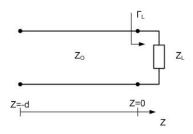

A typical direct detection receiver is made of an antenna, a LNA, a square-law diode detector and dc amplifiers. A block diagram is shown in Fig. 11. The average output voltage Vout (V) is the product of the RF bandwidth  $\Delta f$ , the receiver responsivity  $\mathcal{R}$  (V/W) and the equivalent input noise power spectral density (PSD) Pin (W/Hz) which is directly related to the temperature of the observed scene.

$$Vout = \mathcal{R} \,\Delta f \,Pin \tag{1}$$

The usual detector figure of merit is the noise equivalent power (NEP), defined as the measured output noise voltage spectral density divided by the responsivity [22].

Fig. 11. Block diagram of the direct detection receiver

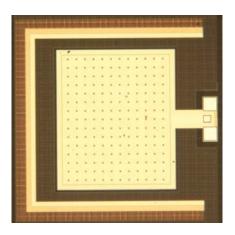

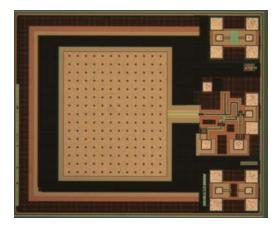

Present LNA-based passive imaging detectors are mainly implemented using GaAs or InP devices. Nevertheless, due to the recent advances in silicon and SiGe technologies, low-cost systems with high temperature resolution can be designed. Recently, a first 94GHz passive imaging direct detector with state-of-the-art NEP implemented on a SiGe BiCMOS process has been reported [23]. It consists of a five-stage common-emitter LNA and a square-law detector implemented using a common-emitter BJT. The chip occupies less then 0.26mm², consumes 34.8mW and has ~ 4000kV/W peak responsivity, a 3-dB bandwidth of 84-103 GHz, and NEP of 0.014 pW/Hz¹/² at 94 GHz.

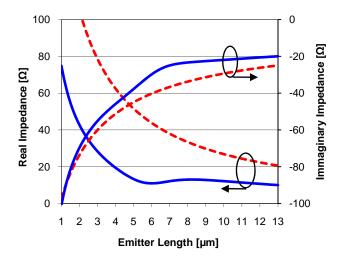

A first example of 90GHz-band passive imaging receiver implemented in a standard 65nm CMOS process is given in [24]. It consists of a 5-stage cascode LNA and a square-law power detector implemented in differential form. A transformer converts the LNA single-ended output into a differential signal that drives the detector. The peak gain of the LNA, measured as stand-alone, is over 27dB at 88GHz and coincides with its minimum NF of 6.8dB. The responsivity of the receiver peaks at over 220kV/W and the best NEP, measured at an IF frequency of 400 kHz, is below  $0.1pW/Hz^{1/2}$ , both at 86GHz. Chip dimensions are  $0.665 \times 0.47 \text{ mm}^2$ .

# 1.4 Building blocks and design solutions for the implementation of millimeter wave systems

#### 1.4.1 Possible architectures for integrated transceivers: fundamental concepts

The common trend in the implementation of millimeter wave circuits, as it results from literature survey, does not consist in the development of ad-hoc circuital architectures, but relies on the adoption of common solutions traditionally used in the radio-frequency domain, extending their validity at higher frequencies.

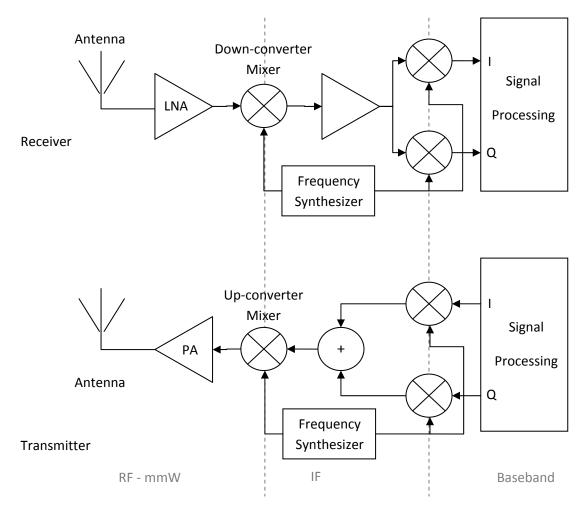

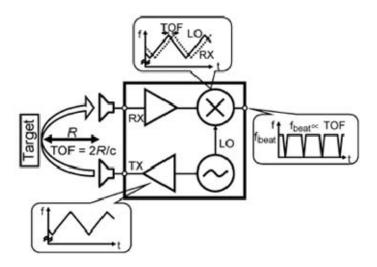

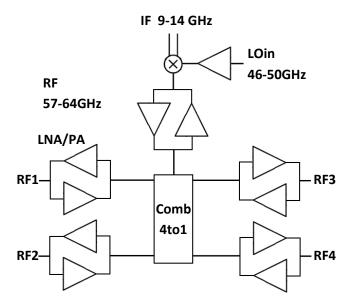

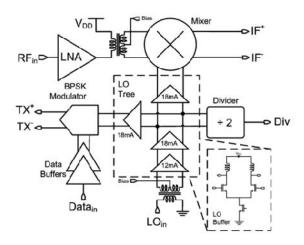

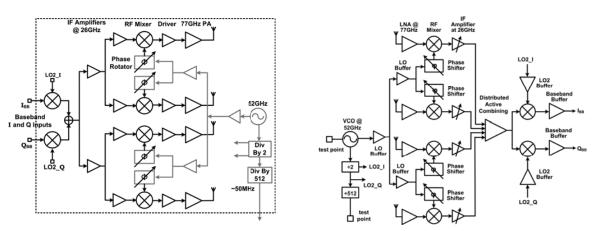

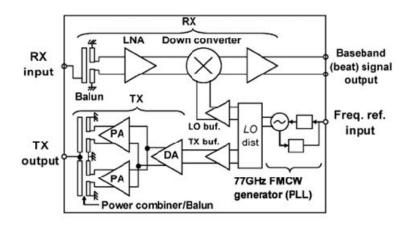

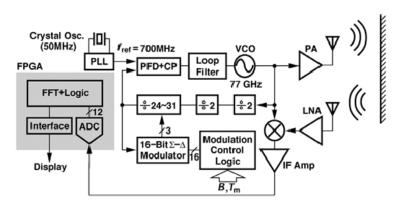

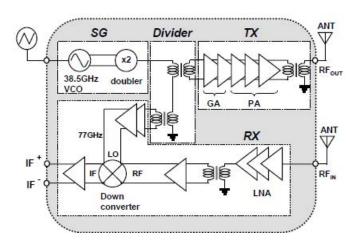

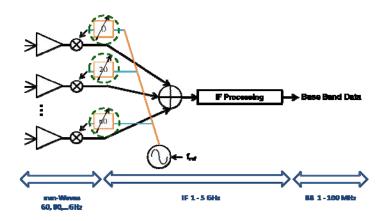

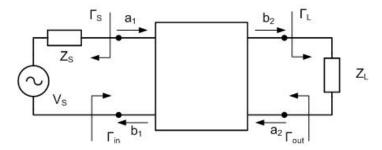

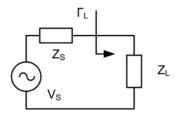

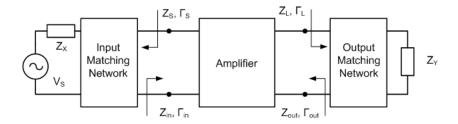

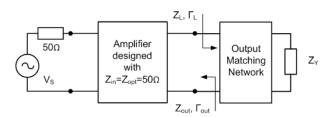

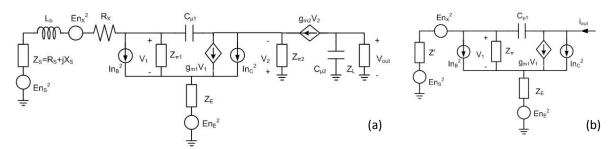

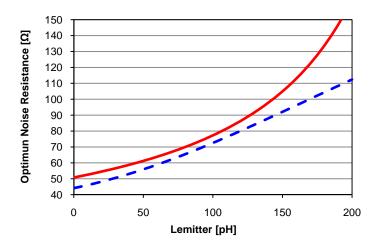

Generally speaking, a standard choice for the implementation of radio-frequency front-ends is the super-heterodyne architecture, shown in the block diagram of Fig. 12. This architecture can be applied, with minor modifications, to several RF receivers and transmitters, as well as to integrated transceivers, regardless of their specific operation, their operative frequencies or targeted applications.

Fig. 12. Simplified block diagram of a super-heterodyne architecture.

As shown in the Figure, the signal at the output of the receive antenna is amplified by a low noise amplifier (LNA) with sufficient gain to establish the system noise figure. The LNA drives a mixer that

translates the RF signal to an intermediate frequency (IF), chosen to provide easy image rejection at the RF and to support very high data-rates. A variable-gain IF amplifier can be used to increase the dynamic range of the receiver.

The IF signal is translated in the baseband frequency and eventually split into its in-phase and in quadrature (I/Q) components, in the case of a quadrature reception scheme. Usually a single frequency synthesizer furnishes the LO signal for the conversion mixer as well as for the quadrature mixers.

The transmit path is designed using a dual strategy. The IF signal — eventually formed by its I/Q components — is translated in the RF carrier frequency by a mixer. Then the RF signal is translated to the desired transmit power by the power amplifier (PA) which, in turn, drives the transmit antenna.

The super-heterodyne performs frequency conversion from RF to baseband and vice versa in two steps. In a variant of the super-heterodyne known as homodyne (or direct conversion, or Zero-IF) architecture, the LO is synchronous to the RF signal and this one is converted to baseband with a single mixing step. It means that the IF frequency is chosen to correspond to the baseband and that the IF signal can be processed as a baseband signal.

In some cases the single-element antenna of Fig. 12 is replaced by a group of antennas forming a phased array. The relative phases of the signals feeding the antennas are varied in such a way that the effective radiation pattern of the array is reinforced in a desired direction and suppressed in undesired directions. The directionality of the array can be varied in a controlled manner applying a signal processing technique known as beamforming. When transmitting, a beamformer controls the phase and relative amplitude of the signal at each transmitter element, in order to create a pattern of constructive and destructive interference in the wave front. When receiving, information from different sensors is combined in such a way that the expected pattern of radiation is preferentially observed. Achieving electronic beam steering, beamforming enables directional communication and reduces interference for receivers that are not targeted. Furthermore, it results in a sensible augmentation of antenna gain both in transmission and reception mode and also of the emitted power if many power amplifiers are inserted in parallel into the array.

Several beamforming techniques have been developed so far and some of them can be applied to the millimeter wave context. Many of the applications discussed in the previous section, from 60GHz links to automotive radars, including imaging systems, can take advantage of it.

Examples of millimeter wave transceivers based on super-heterodyne or direct conversion architecture, with or without on-chip phased-arrays, are illustrated in the next section. Hereafter, we will give a brief overview of the most common building blocks of radio frequency systems and a summary of their main features.

#### 1.4.2 Low-Noise Amplifier (LNA)

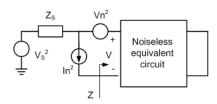

The first stage of a receiver is typically a Low-Noise Amplifier (LNA), whose main function is to provide enough gain to overcome the noise contribution of subsequent stages. Usually it is located just after the antenna (or after the antenna switch or filter, if they are included in the receiver

architecture). Regardless of the specific application, a wireless receiver must handle the signal coming from the antenna that is characterized by a very low power level. Any further degradation of the input signal must be avoided and an LNA should provide sufficient gain while adding as little noise as possible. LNAs are therefore designed following special techniques in order to reduce their noise contributions.

The role of the LNA inside a receiver system can be more rigorously expressed by means of the Friis equation that links the noise factor of a N-stage reception chain (F) with the noise  $(F_i)$  and gain  $(G_i)$  contributions of the i-th stage, as follows:

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \frac{F_4 - 1}{G_1 G_2 G_3} + \cdots$$

(2)

A detailed strategy for LNA design will be described in Chapter 3. Now, let us focus on the parameters commonly used to evaluate the performances of a LNA.

First of all a LNA must provide low noise *and* high gain, as results from (2). Besides, it should accommodate large signals without distortion and frequently must present a specific input impedance in order to be matched to the source. Additionally, power consumption is an important consideration in many applications. Furthermore, in the specific context of millimeter wave, also reverse isolation and stability are critical considerations.

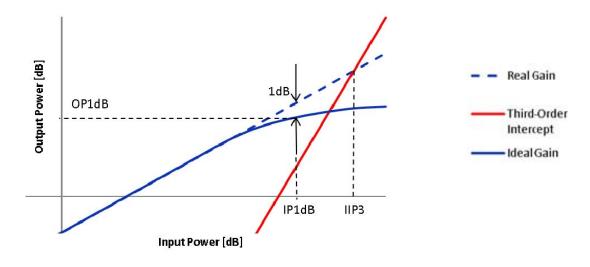

A simple way to estimate the linearity of an amplifier is based on gain compression. For an ideal linear amplifier, power gain should be a linear function of input power. Actually, the gain will start to saturate when input signal becomes too large. The input-referred 1dB compression point (IP1dB) is defined as the value of input power that corresponds to a mismatch of 1dB between the real gain and the ideal gain predicted on the basis of the linear assumption. Sometimes, the output-referred compression point (OP1dB) that is the output power corresponding to the 1dB gain compression point is used.

Linearity can also be measured in terms of third-order intercept point (IP3). The output of a linear, memoryless system can be approximated as follows:

$$f[v] \cong c_0 + c_1 v + c_2 v^2 + c_3 v^3 \tag{3}$$

$$v = V\cos(\omega_1 t) + V\cos(\omega_2 t) \tag{4}$$

where v is the input signal, chosen as sufficiently small to make reasonable the approximation with a power series truncated after the cubic term. If v is the sum of two sinusoidal tones of equal amplitude but slightly different frequencies as in equation (4), then the cubic term of the output gives rise to third-order intermodulation product:

$$\frac{3}{4}c_{3}V^{3}[\cos(\omega_{1}+2\omega_{2})t+\cos(\omega_{1}-2\omega_{2})t+\cos(2\omega_{1}+\omega_{2})t+\cos(2\omega_{1}-\omega_{2})t] \tag{5}$$

Whereas the sum frequency terms can be neglected in a tuned amplifier, the difference frequency terms lie within the bandwidth of RF signal and their amplitude increases as a function of input amplitude (V) three times faster than the fundamental term on a logarithmic scale. The intercept point occurs when the amplitude of the intermodulation term equals the amplitude of the fundamental term:

$$|c_1V| = \left|\frac{3}{4}c_3V^3\right|$$

$$V^2 = \frac{4}{3} \left| \frac{c_1}{c_3} \right|$$

Then, moving from the input voltage amplitude to the power domain, the input-referred third-order intermodulation point (IIP3) is:

$$IIP3 = \frac{V^2}{2R} = \frac{2}{3R} \left| \frac{c_1}{c_3} \right| \tag{6}$$

Alternatively, the IIP3 can be calculated feeding the amplifier with a single tone input and evaluating the influence on the output of its third-order harmonic. In both cases, the resulting IIP3 value is a purely mathematical concept that relies on the assumption that the higher-order, non-linear terms not considered in (3) are negligible, a condition that is not verified in many practical cases. In both simulations and experiments, the IIP3 is evaluated by extrapolating trends observed with relatively small amplitude inputs, at the smallest possible power level and its value depends on the measurement conditions that need to be accurately documented. Nevertheless, the IIP3 is often reported in the literature without any detail of the measurement conditions, making impossible the comparison between data of different sources.

Fig. 13. Linearity.

#### 1.4.3 Mixer

Mixers are frequency-translation devices. In all receivers based on the heterodyne architecture, they are commonly used to convert the radio frequency input signal to the intermediate frequency. Since a linear, time-invariant system cannot produce output signals with spectral components that are not present at the input, mixers must be either nonlinear or time-varying elements in order to perform frequency translation.

Practically speaking, a mixer consists of two inputs, the RF signal and the output of a local oscillator, that are multiplied, giving an output signal at a frequency that is the sum or, as more usual, the

difference between the input frequencies, together with some undesired spurious products. Actually, two input frequencies, frequently referred as *sidebands*, will correspond to a given intermediate frequency since signals both above and below  $\omega_{LO}$  by an amount equal to  $\omega_{IF}$  will produce IF outputs at the same frequency. In many cases only one is the desired RF signal whereas the other is a disturb known as *image* signal.

The definition of noise figure in the context of mixers must take this phenomenon into account. Usually a single sideband (SSB) NF is defined considering the signal-to-noise ratio at the RF port, divided by the SNR ratio at the IF port that includes also the noise contribution due to the image signal. On the contrary, when both the main RF and image signals contain useful information, a double sideband (DSB) NF should be used.

Beside NF, an important mixer characteristic is conversion gain which is defined as the power ratio of the IF output to the RF input. It can be greater than unity in active mixers, whereas a passive mixer is usually affected by conversion loss.

As in the case of amplifiers, linearity in the context of mixers can be evaluated using the 1dB compression point of the conversion gain (IP1dB) or the third-order intermodulation intercept point (IIP3) defined considering two input tones with slightly different frequencies, both within the RF range, in a similar manner as explained in the previous paragraph.

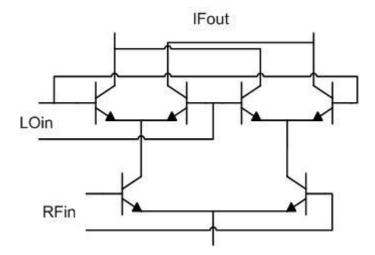

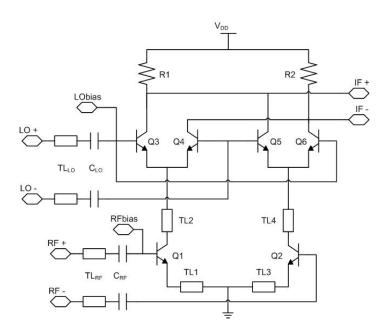

Another parameter of great importance in mixer design is isolation. Interaction among the RF, IF, and LO ports must be minimized, to assure that each one of the three concerned signal operates correctly. In particular, to prevent the presence of RF and LO signals at the output port, together with the desired IF signal, a double-balanced mixer can be used. In a double-balanced mixer both the RF and LO signals are applied differentially at the corresponding input ports, adding themselves destructively at the IF port. The most common implementation of a double-balanced mixer as an integrated circuit is the four-quadrant multiplier based on the Gilbert cell, sketched in Fig. 14. This solution, common in traditional radio frequency context, can be efficiently applied also to millimeter wave design.

Fig. 14. Double-balanced mixer based on the Gilbert cell.

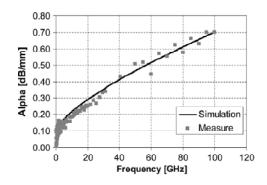

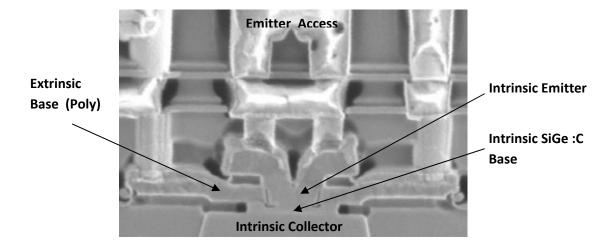

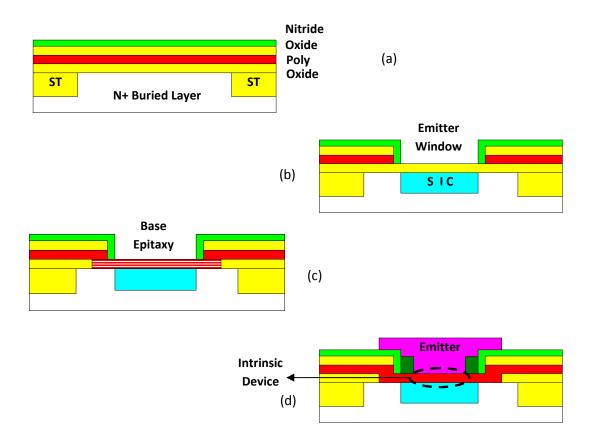

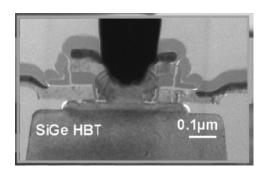

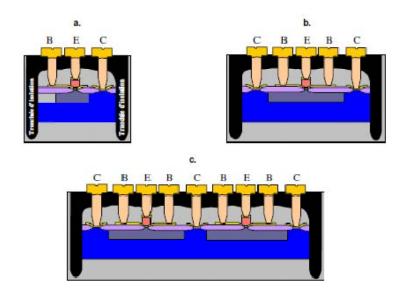

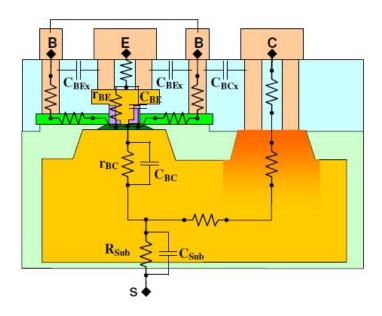

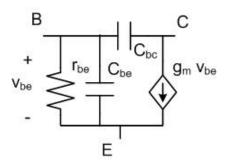

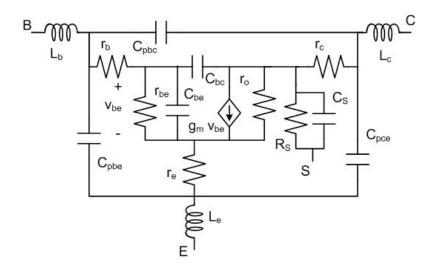

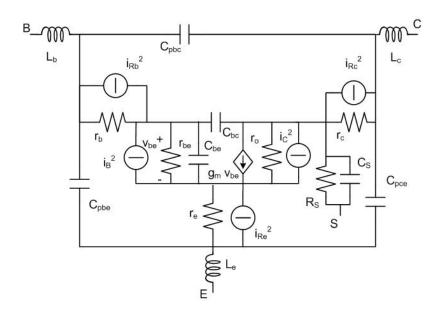

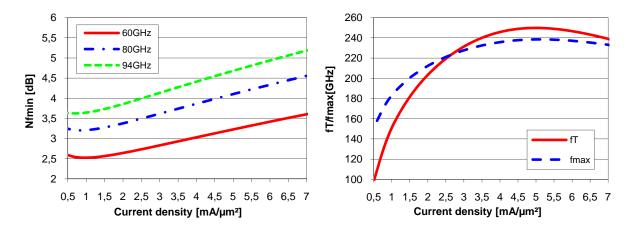

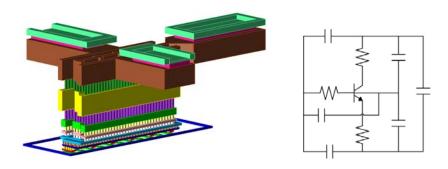

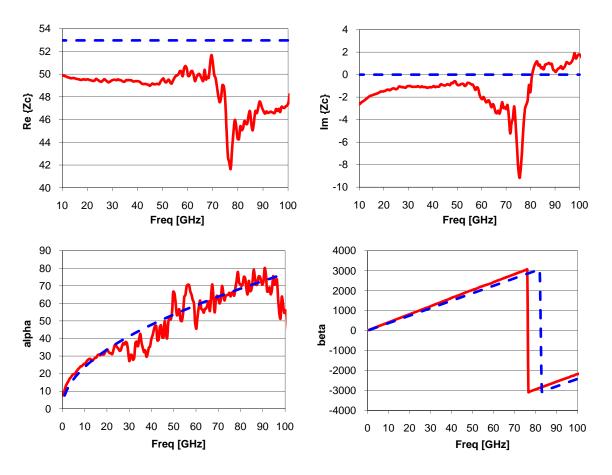

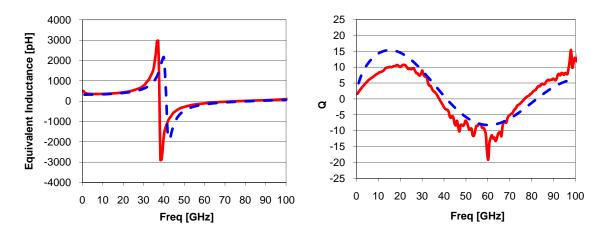

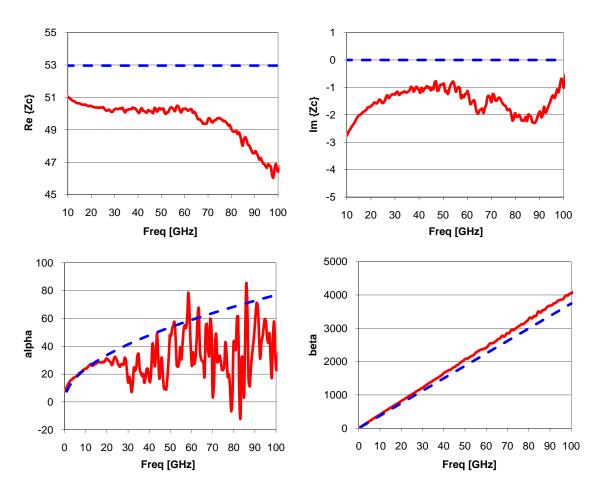

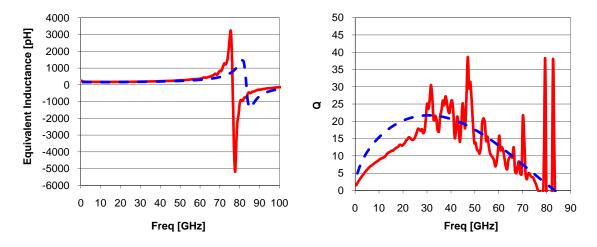

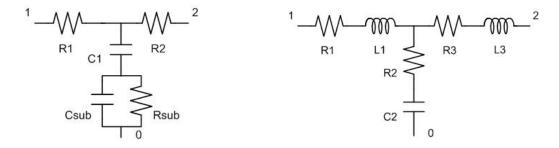

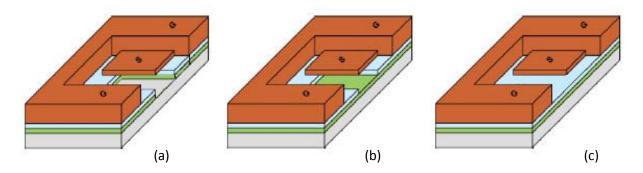

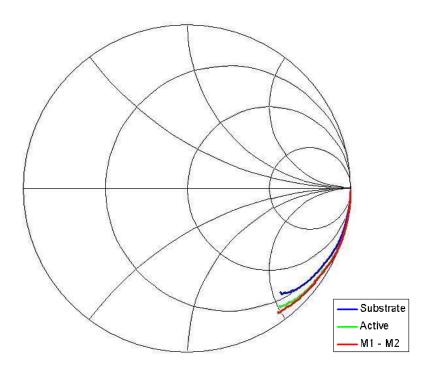

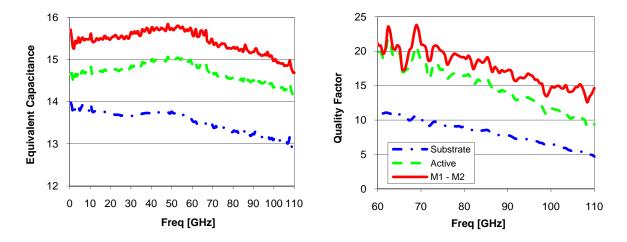

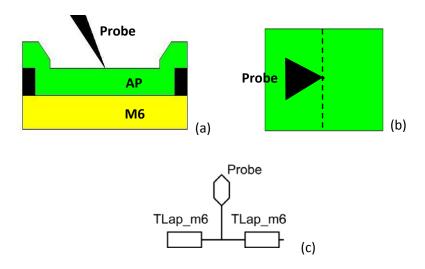

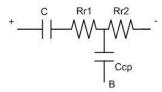

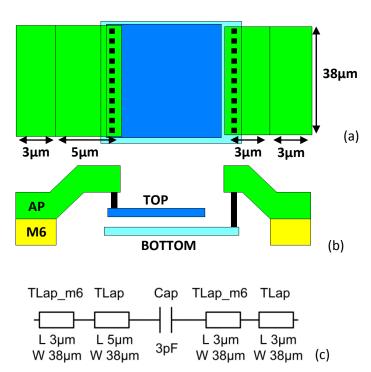

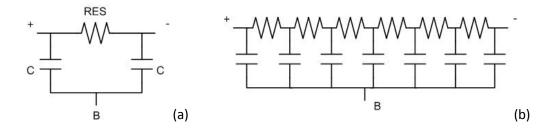

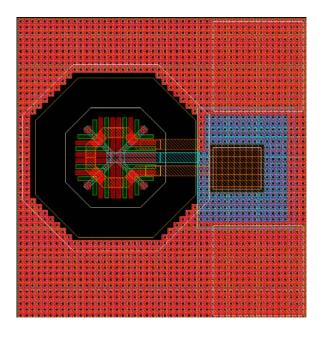

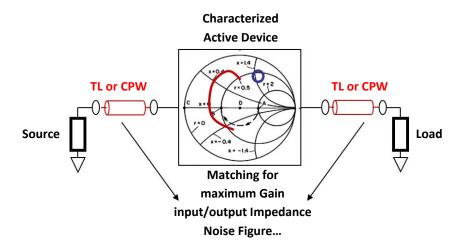

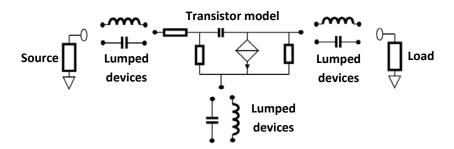

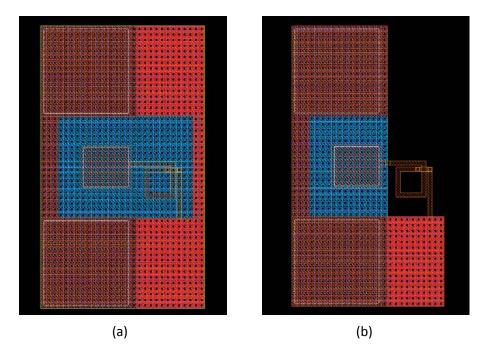

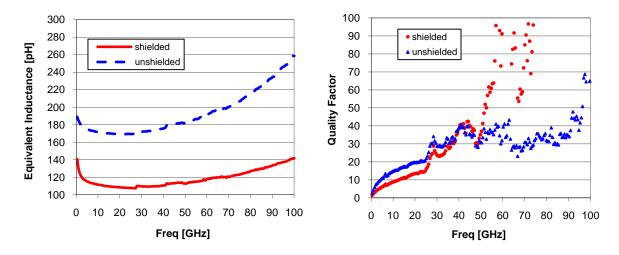

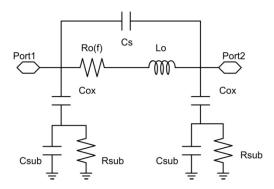

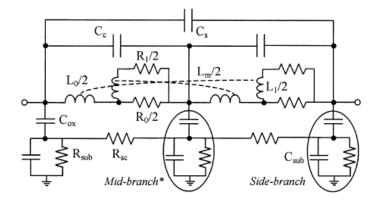

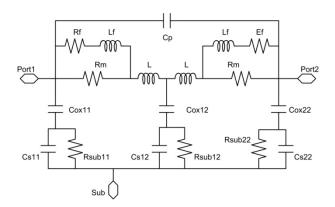

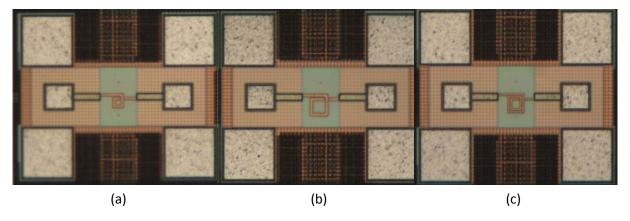

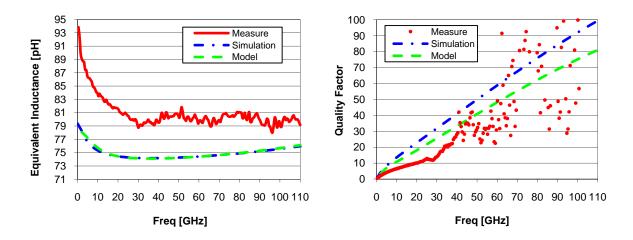

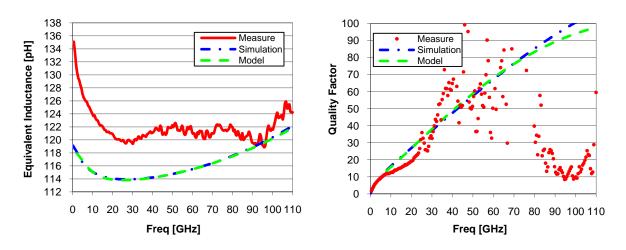

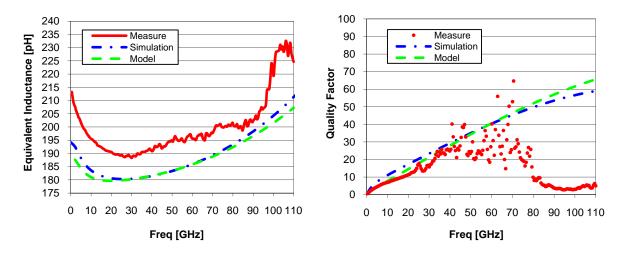

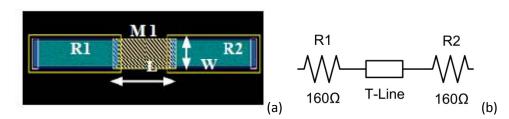

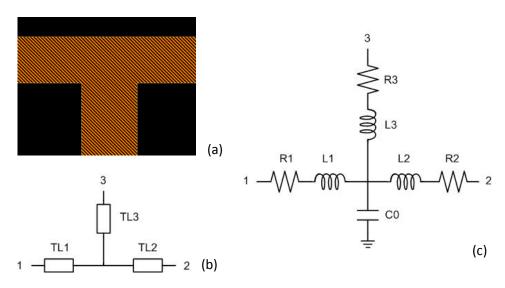

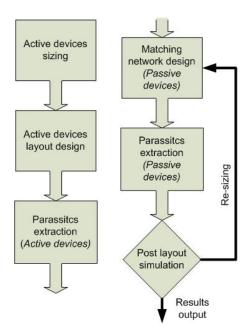

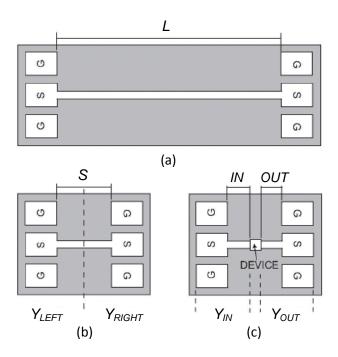

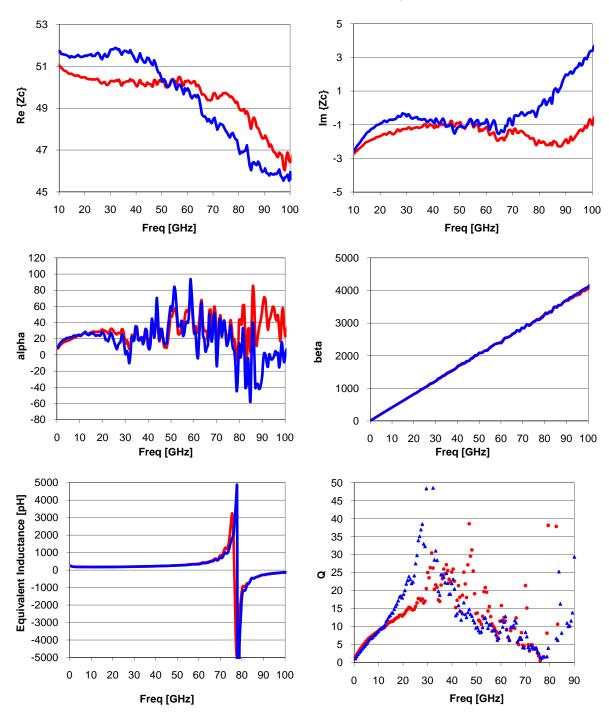

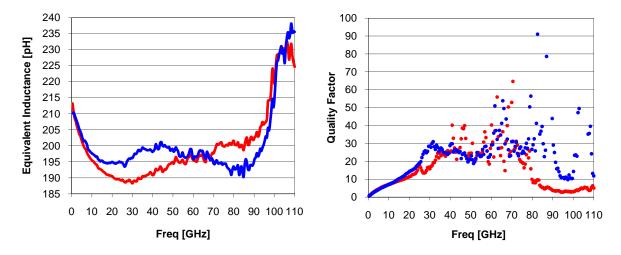

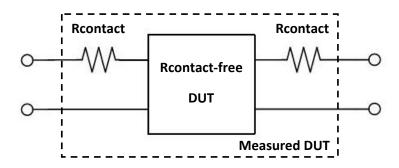

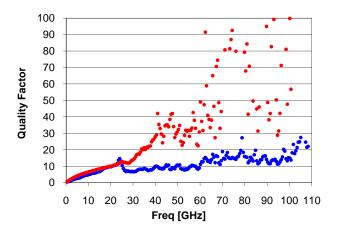

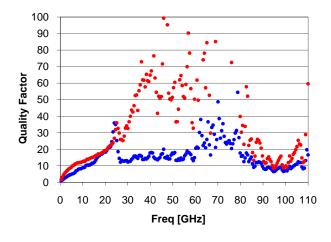

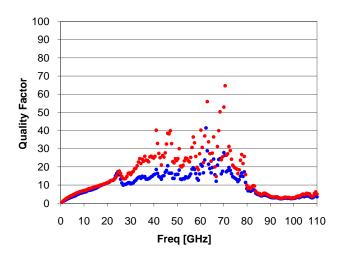

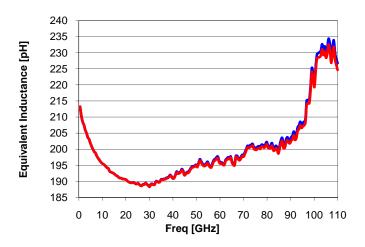

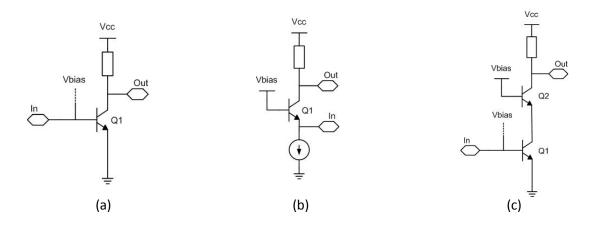

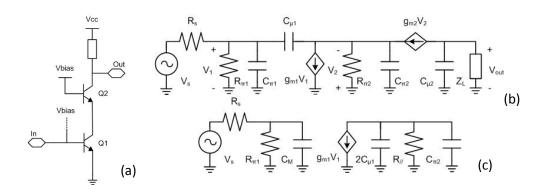

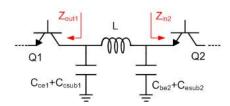

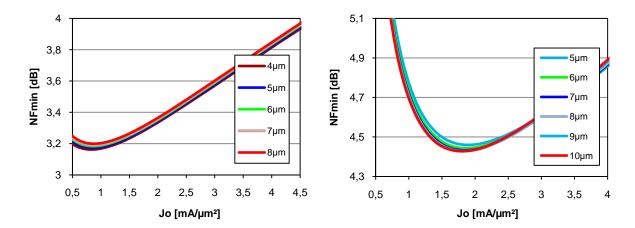

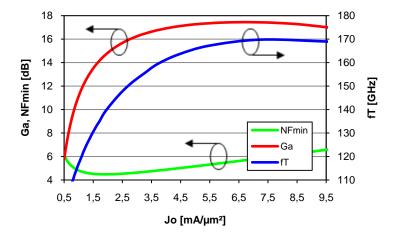

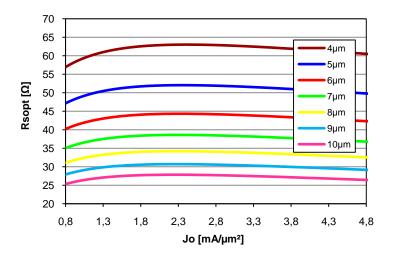

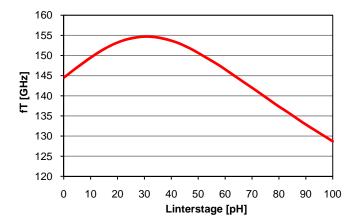

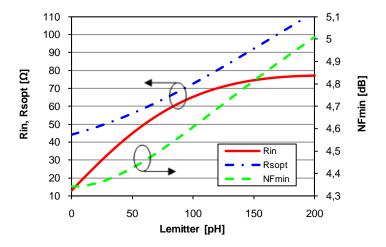

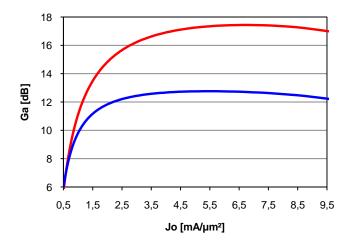

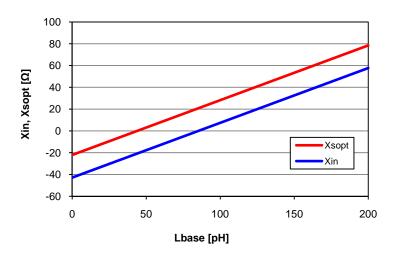

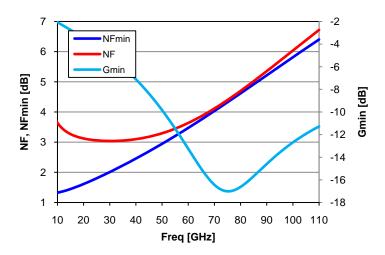

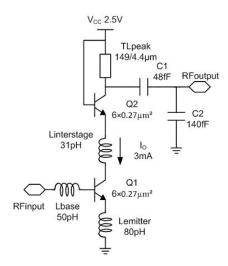

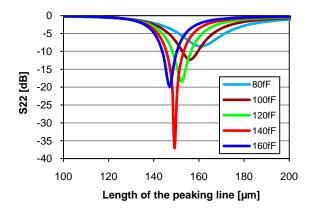

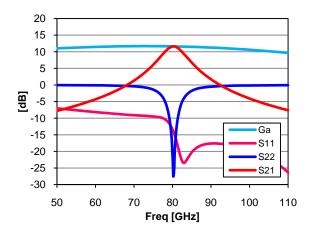

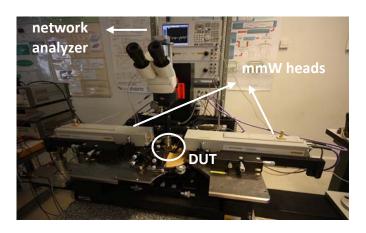

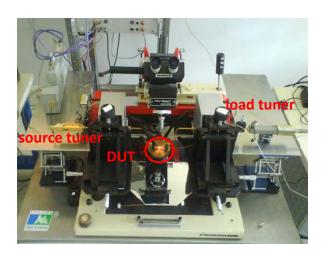

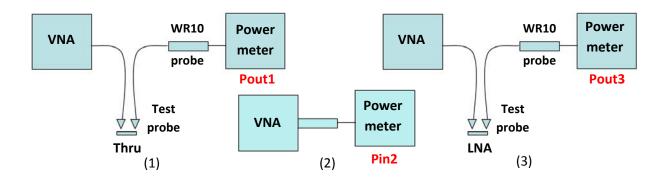

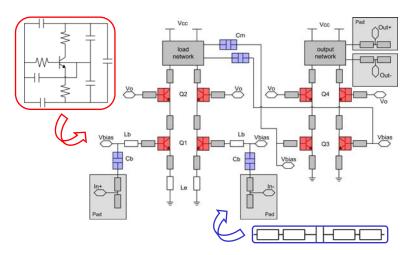

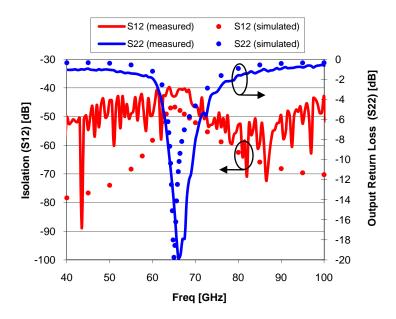

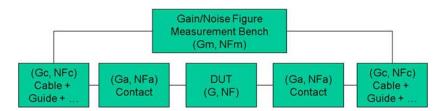

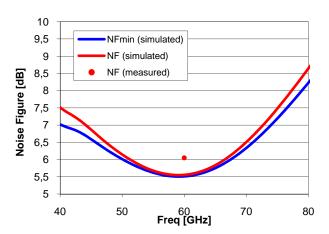

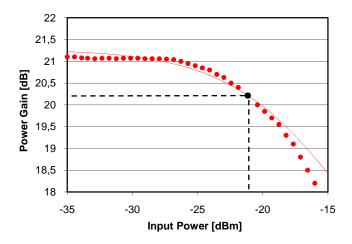

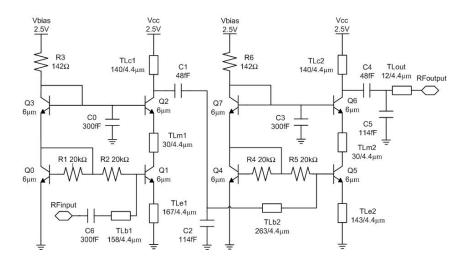

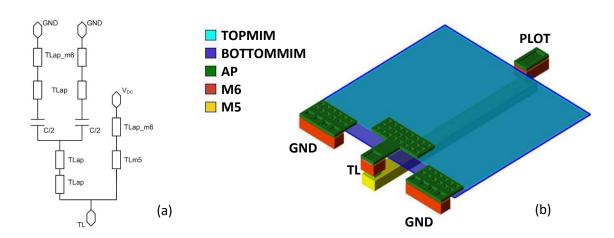

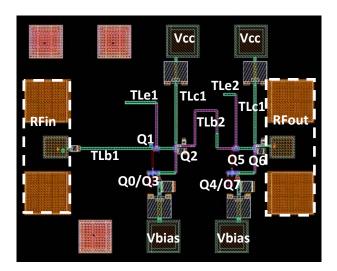

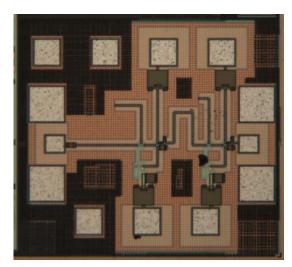

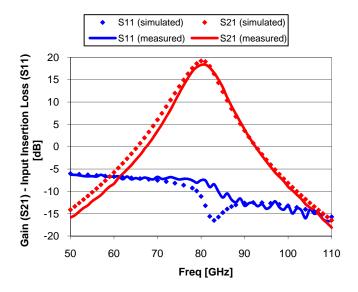

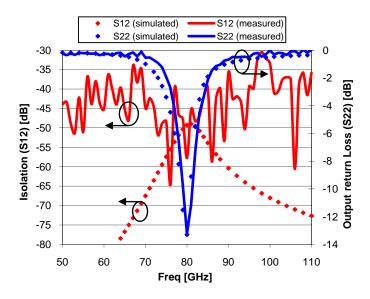

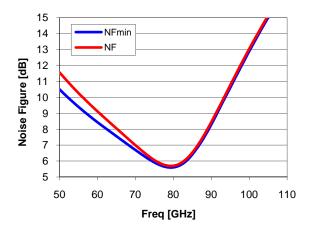

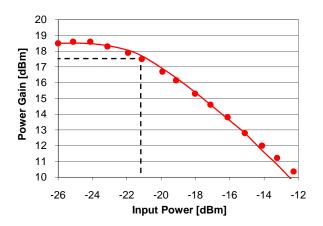

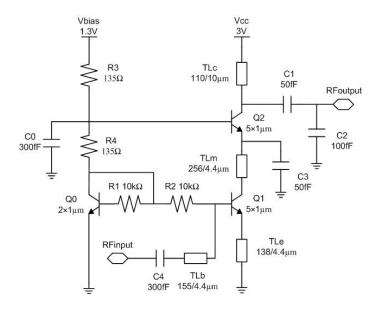

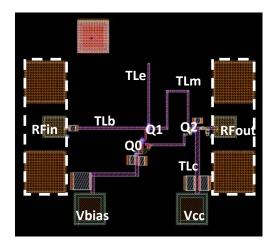

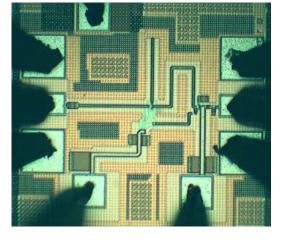

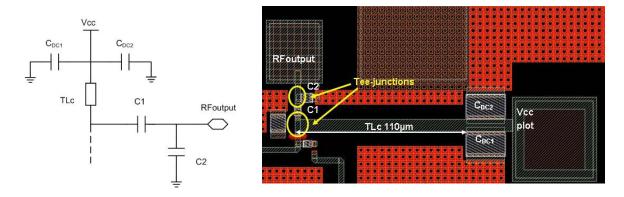

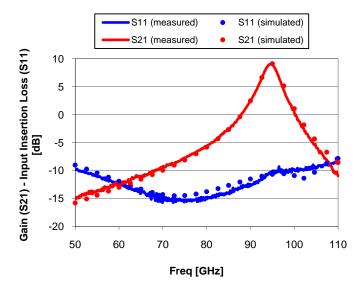

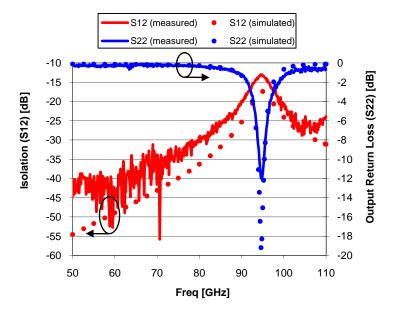

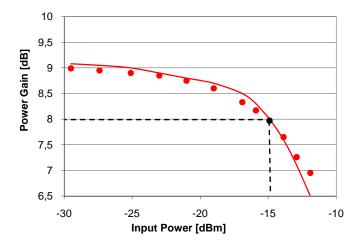

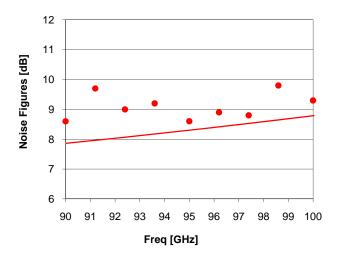

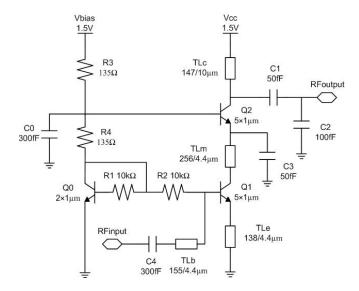

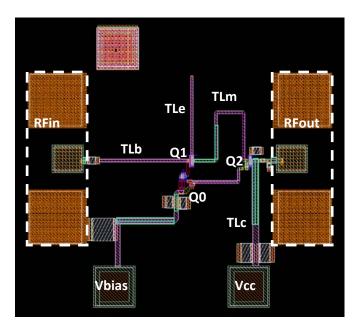

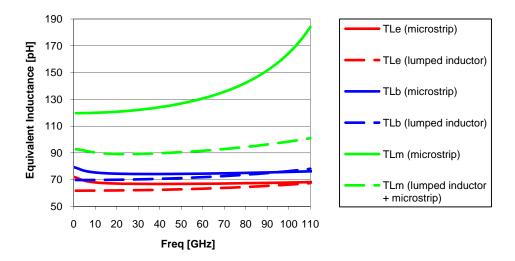

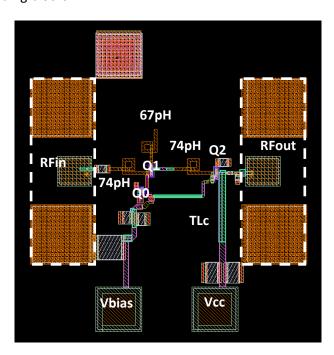

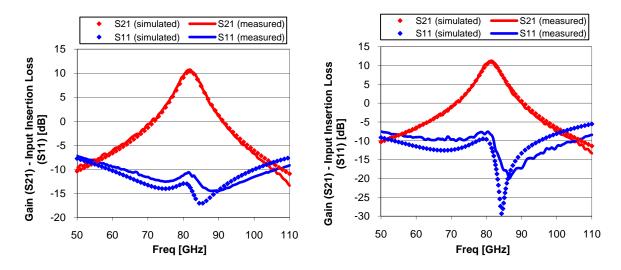

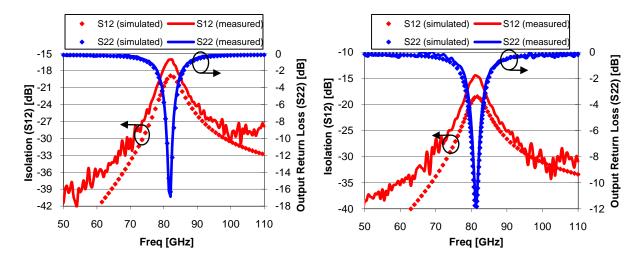

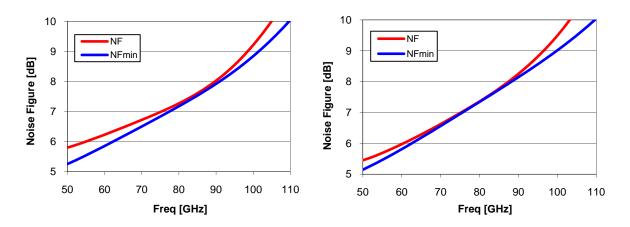

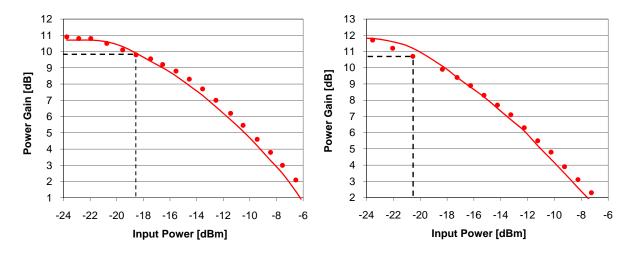

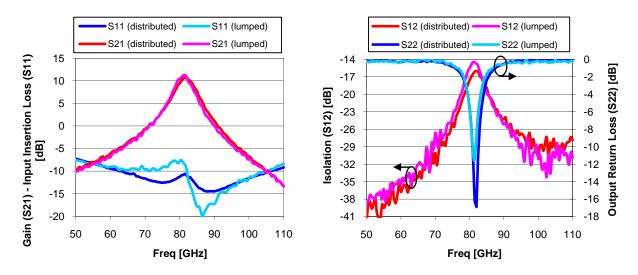

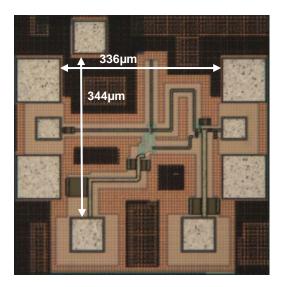

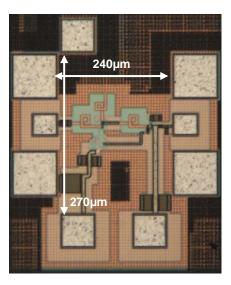

# 1.4.4 Frequency Synthesizer