# Université de Provence

École Doctorale 353 – Sciences pour l'ingénieur : Mécanique, Physique, Micro et Nanoélectronique

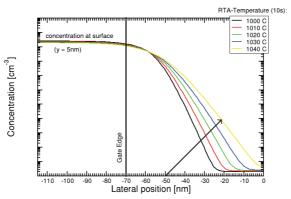

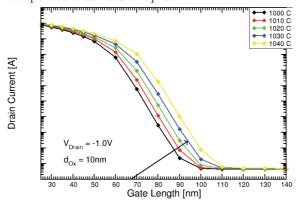

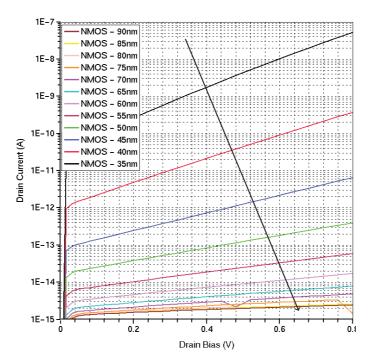

# THÈSE

pour obtenir le grade de Docteur de l'université de Provence

présentée et soutenue publiquement par Pascal LEMOIGNE

Équipes d'accueil : IM2NP et STMicroelectronics

Titre:

# Simulation de la variabilité du transistor MOS

Soutenue le 1<sup>er</sup> décembre 2011 devant le jury composé de :

| Rachid Bouchakour, HDR | Président  | CNRS/IM2NP, Marseille       |

|------------------------|------------|-----------------------------|

| Gérard Ghibaudo, HDR   | Rapporteur | CNRS/IMEP, Grenoble         |

| Pascal Masson, HDR     | Rapporteur | CNRS/LEAT, Nice             |

| Lakhdar Zaïd, HDR      | Directeur  | CNRS/IM2NP, Marseille       |

| André Juge, Docteur    | Directeur  | STMicroelectronics, Crolles |

| Christian Dufaza, HDR  | Invité     | CNRS/IM2NP, Marseille       |

# Merci à vous!

Je tiens à remercier Jean-Daniel Arnould, mon directeur de stage de M2R pour m'avoir incité à poursuivre en thèse et à « ne pas se poser de limites. »

Merci à Gérard Ghibaudo et Pascal Masson de m'avoir fait l'honneur d'accepter d'être rapporteurs de cette thèse malgré leurs agenda déjà plein.

Je veux témoigner ma gratitude à mes premiers directeurs de thèse Christian Dufaza et Denis Rideau, ainsi qu'à Hervé Jaouen et Clément Tavernier qui m'ont accordé leur confiance en m'accueuillant dans leurs équipes.

Ces travaux n'auraient pas aboutis sans mes actuels directeurs de thèse André Juge et Lakhdar Zaïd qui ont accepté de reprendre l'encadrement de cette thèse à mi-parcours à la suite de réorganisations à Crolles comme à Marseille, et qui m'ont soutenu et encouragé jusqu'au bout (et au delà!). Encore merci.

Merci à Albane Sangiovanni pour les corrections de ce manuscrit.

Je tiens à remercier l'équipe de Crolles avec qui j'ai énormément appris et avec qui j'ai passé trois très bonnes années : Lorenzo, Adi, Clément, Denis, Blandine, Xavier, Thierry, Pierre, François, Olivier, Vincent, Florian, Daniel, David, Grégory... Merci aux thésards pour les bons moments et la bonne ambiance (et quelques soirées mémorables;) ) Maxime, Vincent, Marc, Mehdi, Sébastien, Alban, Andres, Romuald, Carine, Jean et Giancarlo.

Merci à l'équipe de *Process Integration*: Maud Bideau, Laurence Boissonnet, Emmanuel Josse et Dominique Golanski auprès de qui j'ai eu un aperçu de ce qui se passait en dehors du monde de la simulation et qui m'ont fourni l'ensemble des mesures utilisées dans cette thèse. Merci à Alexander Burenkov pour notre collaboration dans le cadre du projet ATOMICS.

Un merci à mes amis pour tout ce que nous avons vécu ensemble et pour m'avoir supporté pendant cette époque : Audrey et Philippe, Romain et Émilie, Caro et Simon, Pierre et Valéria, Jojo et Séverine, Be, Jack, Pierrot et Olivia, Benoit et Nathalie, David, Cobo, Olivier et Pauline, Émilie, Rémy et Céline, Bao, Julien, Anaïs, Katia, Alex et Géo, Gaspard, Rom2.

Enfin je remercierai ma famille, sans qui je ne serais pas là, avec qui nous traversé des moments tristes et des moments heureux pendant cette intervalle

$\operatorname{de}$  temps. Merci pour vos encouragements.

# Table des matières

|    | Tab  | le des n | natières                                                | V          |

|----|------|----------|---------------------------------------------------------|------------|

| In | trod | uction   | V                                                       | 'i         |

| 1  | Cor  | ntexte   | – Problématique                                         | 1          |

|    | 1.1  | La vai   | riabilité et ses conséquences                           | 4          |

|    | 1.2  | Source   | es de déviation                                         | 7          |

|    |      | 1.2.1    | Observations des effets                                 | 7          |

|    |      | 1.2.2    |                                                         | 13         |

|    |      | 1.2.3    | Sources originaires du dessin                           | 21         |

|    |      | 1.2.4    | Sources originaires du procédé                          | 27         |

|    | 1.3  | Modél    | lisation des déviations                                 | 32         |

|    |      | 1.3.1    | Variabilité du process                                  | 32         |

|    |      | 1.3.2    | Variabilité du transistor                               | 34         |

|    |      | 1.3.3    | Variabilité des circuits                                | 36         |

|    | 1.4  | Concl    | usion                                                   | 37         |

| 2  | Car  | actéris  | sation du dopage des dispositifs MOSFET                 | 39         |

|    | 2.1  |          |                                                         | 36         |

|    | 2.2  | Carac    | térisation de la température de recuit                  | 41         |

|    |      | 2.2.1    | Estimation de la variation spatiale de la température   |            |

|    |      |          | reçue                                                   | 42         |

|    | 2.3  | Carac    | térisation électrique du profil latéral du dopage 4     | 45         |

|    |      | 2.3.1    | Principe de la méthode                                  | <b>1</b> 5 |

|    |      | 2.3.2    | Application de la méthode sur des simulations TCAD      |            |

|    |      |          | d'un procédé industriel                                 | 48         |

|    |      | 2.3.3    | Étude de l'impact de la variabilité du procédé à l'aide |            |

|    |      |          | d'un plan d'expériences                                 | 5(         |

|    |      | 2.3.4    |                                                         | 52         |

|    |      | 2.3.5    | Conclusion                                              | 54         |

|    | 2.4  | Carac    | térisation de la polarisation du substrat               | 54         |

|    |      | 2 4 1    | L'effet substrat                                        | 54         |

|  | MATIERES |

|--|----------|

|  |          |

|  |          |

|  |          |

|  |          |

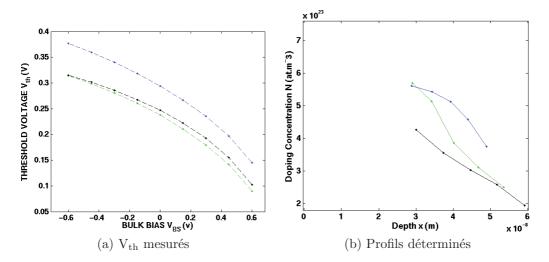

|    |       | 2.4.2 Extraction des paramètres gamma et phif                    | 55  |

|----|-------|------------------------------------------------------------------|-----|

|    |       | 2.4.3 Caractérisation de l'effet avec un dopage réel             |     |

|    |       | 2.4.4 Effet de la longueur de grille sur cette caractérisation . |     |

|    | 2.5   | Détermination du dopage canal                                    |     |

|    |       | 2.5.1 Méthode                                                    |     |

|    |       | 2.5.2 Simulations TCAD                                           |     |

|    |       | 2.5.3 Détermination du profil vertical à partir de l'effet sub-  |     |

|    |       | strat                                                            | 60  |

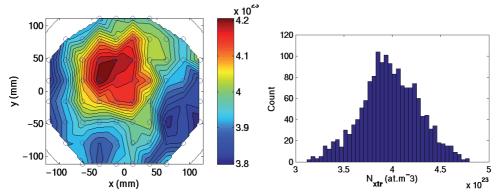

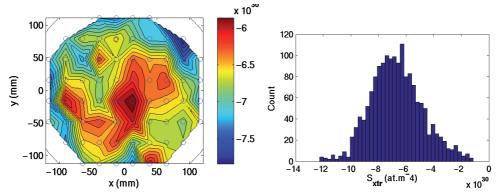

|    | 2.6   | Variabilité du profil de dopage vertical                         | 61  |

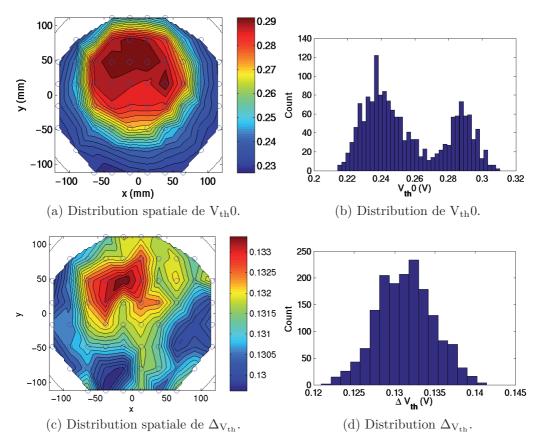

|    |       | 2.6.1 Présentation des données expérimentales                    | 61  |

|    |       | 2.6.2 Application de la méthode                                  | 62  |

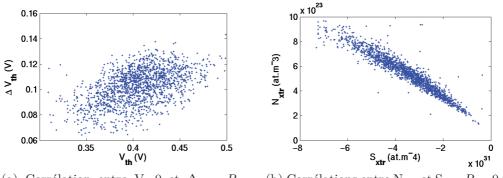

|    |       | 2.6.3 Étude des corrélations                                     | 64  |

|    | 2.7   | Conclusion                                                       | 66  |

| 3  | Étu   | de expérimentale du nœud technologique 45nm                      | 68  |

|    | 3.1   | Les variables étudiées                                           | 69  |

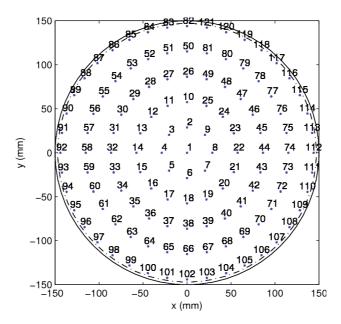

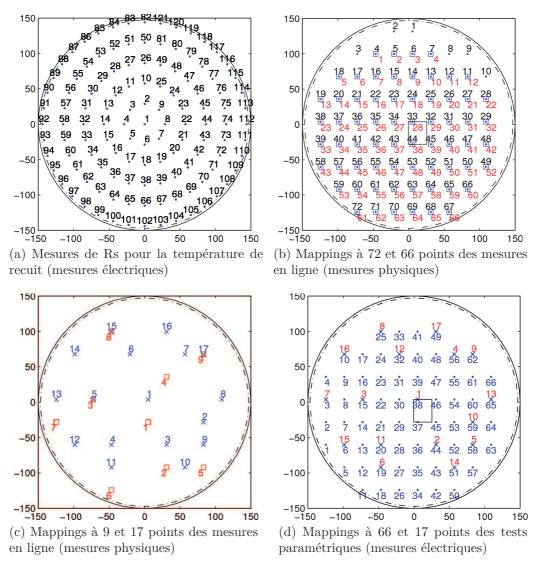

|    |       | 3.1.1 Échantillonage spatial                                     |     |

|    | 3.2   | Observation des données                                          | 72  |

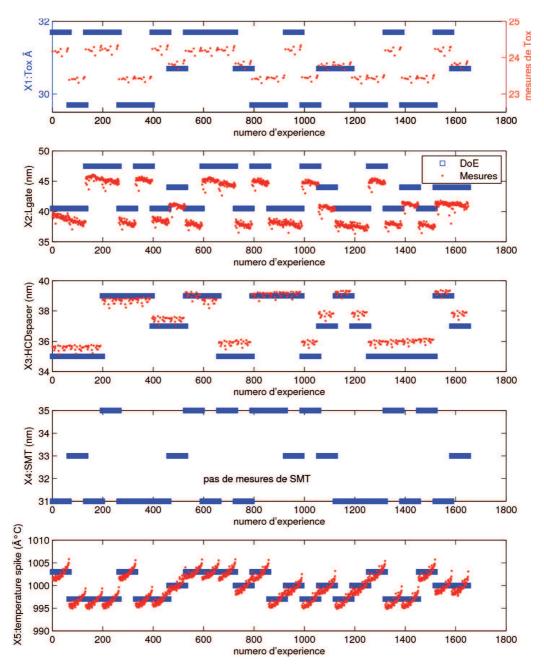

|    |       | 3.2.1 Les facteurs                                               | 72  |

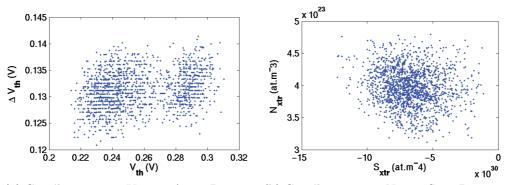

|    |       | 3.2.2 Variabilité intra-plaque                                   |     |

|    |       | 3.2.3 Corrélations entre variables technologiques                |     |

|    |       | 3.2.4 Indépendance des expériences                               |     |

|    | 3.3   | Étude du plan d'expériences                                      |     |

|    |       | 3.3.1 Le plan expérimental                                       | 83  |

|    |       | 3.3.2 Régression multilinéaire d'un modèle polynomial            | 86  |

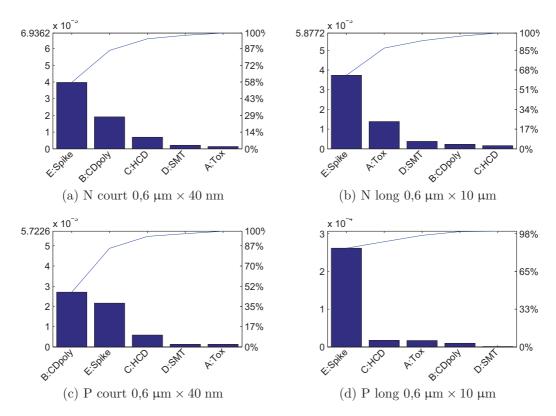

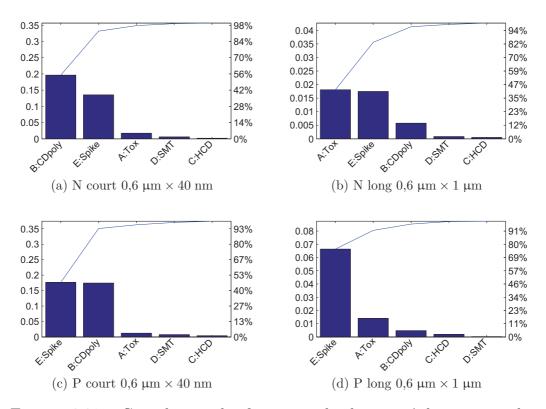

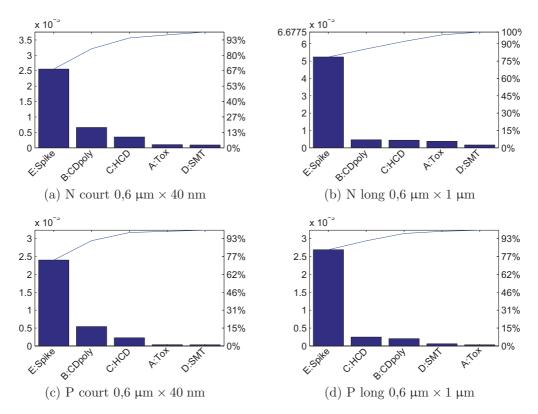

|    |       | 3.3.3 Estimation de la contribution de chaque facteur            | 93  |

|    | 3.4   | Conclusions                                                      | 103 |

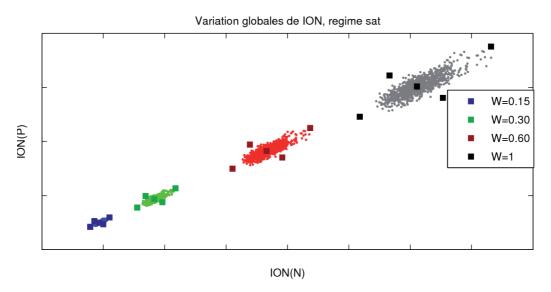

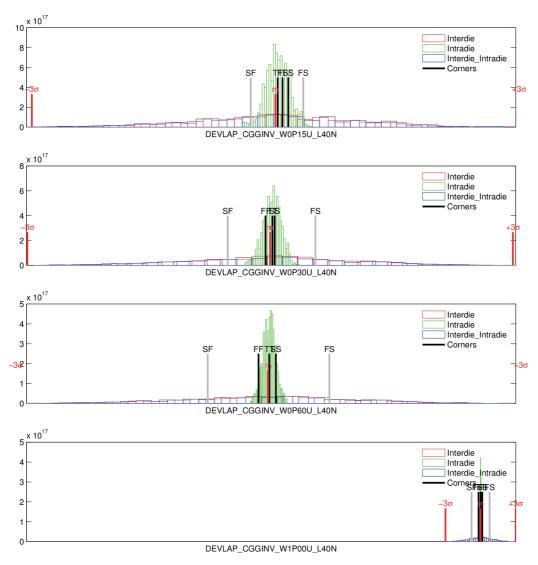

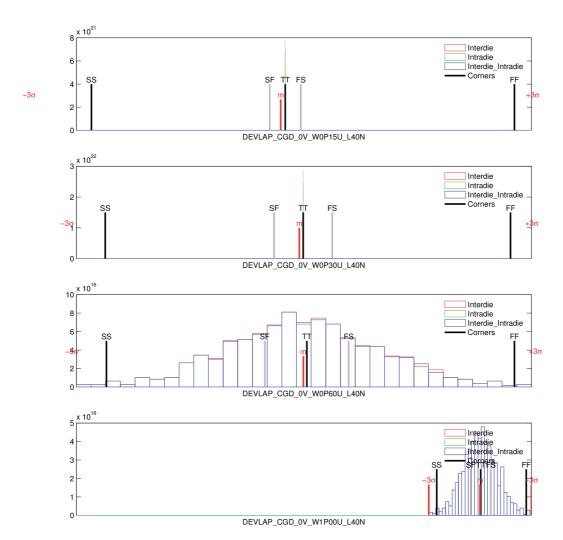

| 4  | Sim   | ulation des variations dans les modèles compacts                 | 104 |

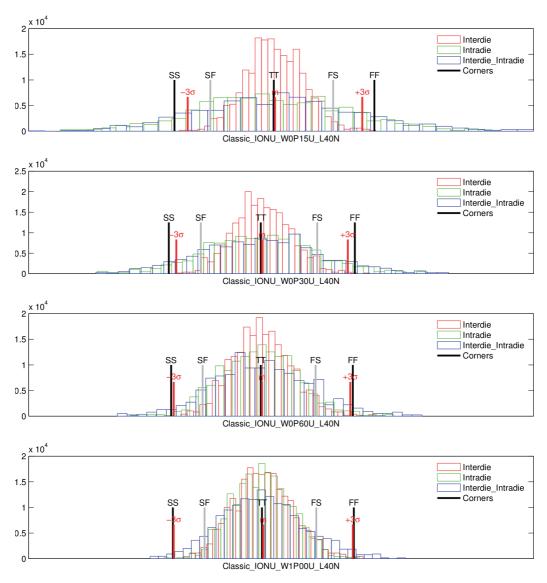

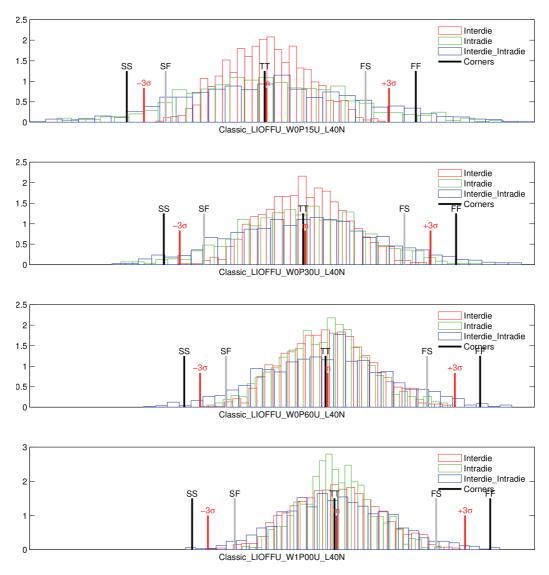

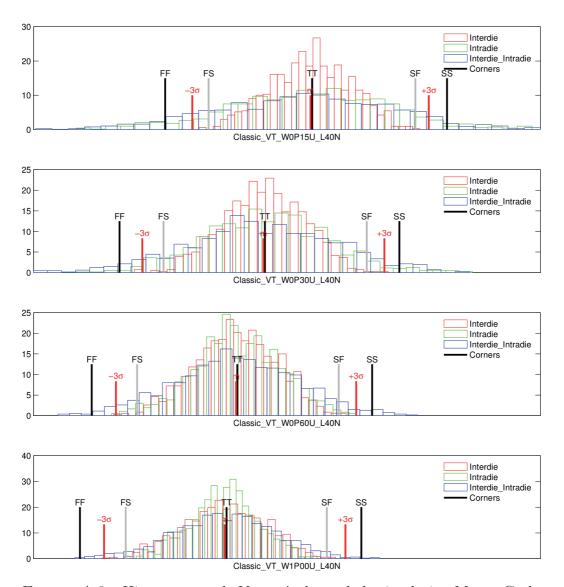

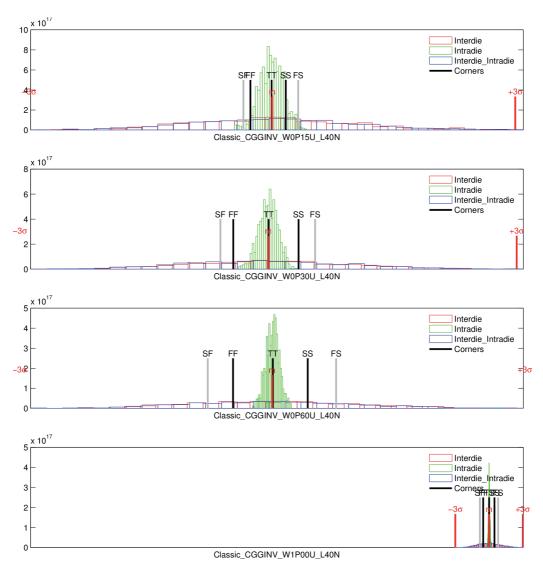

|    | 4.1   | Simulations Monte-Carlo                                          | 105 |

|    |       | 4.1.1 Construction de la simulation Monte-Carlo                  | 105 |

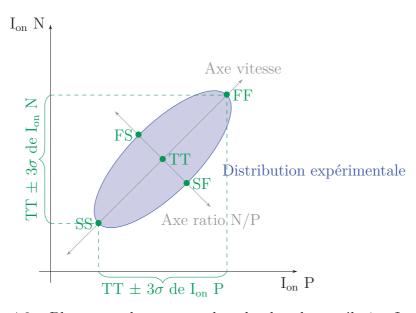

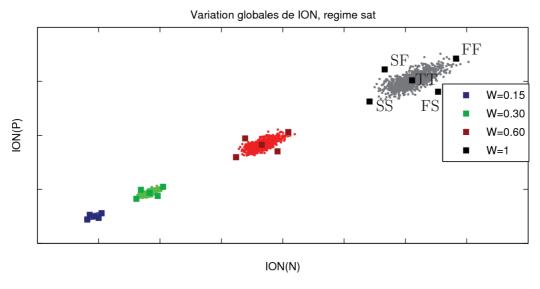

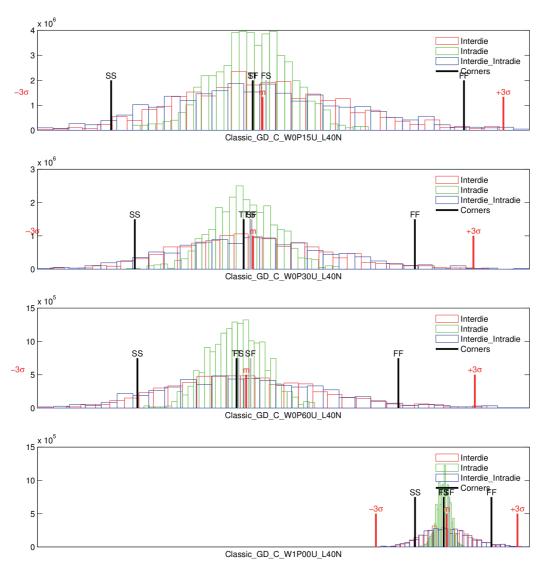

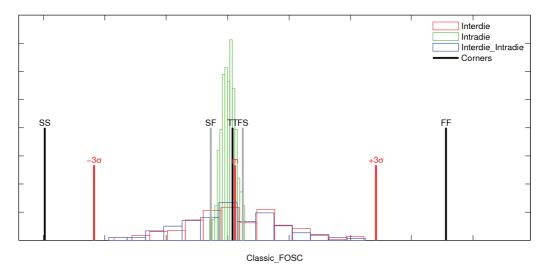

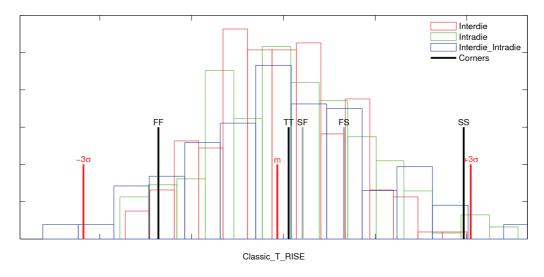

|    | 4.2   | Génération de Corners                                            | 107 |

|    |       | 4.2.1 Méthode standard                                           | 108 |

|    |       | 4.2.2 Statut par rapport aux résultats Monte-Carlo               | 110 |

|    |       | 4.2.3 Génération spécifique à une performance                    | 113 |

|    |       | 4.2.4 Détermination non paramétrique multidimensionnelle .       | 114 |

|    | 4.3   | Modification du modèle de variation                              | 114 |

|    |       | 4.3.1 Résultats                                                  | 117 |

|    | 4.4   | Conclusion                                                       | 121 |

| Co | onclu | usion générale                                                   | 122 |

| TABLE DES MATIÈRES |                                              | vi  |

|--------------------|----------------------------------------------|-----|

| A Annexes          |                                              | 125 |

| A.1 Figures d      | du chapitre 4                                | 125 |

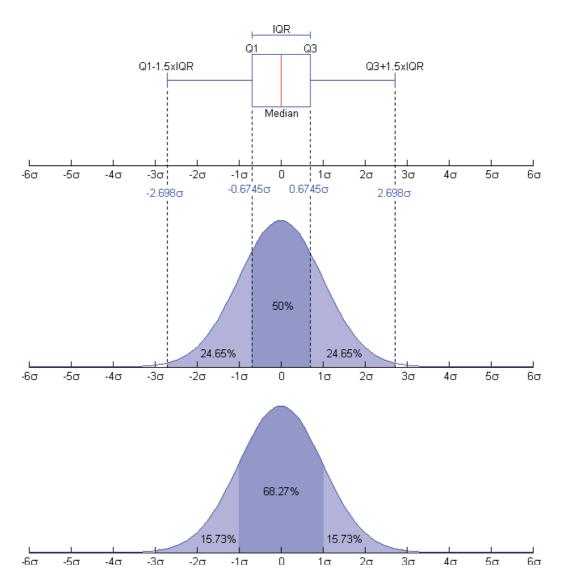

| A.2 Boite à n      | moustaches                                   | 136 |

| A.3 Extraits       | de code relatifs aux simulations Monte-Carlo | 138 |

| Bibliographie      |                                              | 152 |

| Liste des figures  | es                                           | 158 |

| Liste des tablea   | aux                                          | 159 |

| Publications       |                                              | 160 |

# Introduction

La constance des performances des produits est une priorité pour les fabricants de circuits intégrés. Ils s'engagent auprès de leurs clients à fournir des puces dont la dispersion des performances est très faible, ce qui implique que chaque circuit fabriqué qui n'entre pas dans les marges de tolérance est mis au rebut et donc fait monter le coût de production moyen par plaque de silicium. Il faut donc savoir contrôler la fabrication afin d'uniformiser les performances. Les produits de l'industrie de la micro-électronique, des circuits électroniques, sont fabriqués par des techniques organisées autour de la photolithographie sur des tranches de silicium cristallin. Une tranche peut contenir de quelques dizaines à des centaines de puces électroniques. Dans une usine, les tranches de silicium sont groupées par lots de vingtcinq plaques pour subir certaines étapes du procédé de fabrication. Enfin, un fondeur peut choisir de fabriquer un même produit dans plusieurs usines. Il y a donc différentes échelles auxquelles vont intervenir les dispersions de performances. Les composants de base des circuits intégrés sont soumis à différentes sources de fluctuations. Certaines sont dues aux matériaux utilisés. En effet, l'implantation volontaire d'impuretés dans le silicium afin de régler les propriétés des composants – le dopage – n'agit pas de manière continue dans tout matériau. C'est une action locale à l'échelle atomique, et plus les composants sont petits, moins les effets sont lissés. De la même manière, l'utilisation de silicium polycristallin introduit des effets locaux aux interfaces entre les cristaux le composant. L'emploi de résines en matériaux polymères entraine une certaine imperfection du bord des gravures, dont l'importance croît avec la miniaturisation des dispositifs.

D'autres imperfections sont induites par les outils du procédé <sup>2</sup>. Les étapes

<sup>1.</sup> c'est le nom qu'on donne aux fabricants de puces, car c'est historiquement l'industrie de la métallurgie qui possédait les outils nécessaires pour fondre le silicium afin d'en faire des cristaux.

<sup>2.</sup> ou process en anglais qui remplace souvent le mot français dans le jargon

Introduction viii

du process comportent des procédés chimiques (gravure, retrait de résine), physiques (gravure, implantation d'ions, dépôt de matériau), thermiques (recuit en four, recuit laser, croissance d'oxyde) ou encore optiques (insolation des résines pour appliquer le dessin des circuits). Les machines réalisant ces étapes introduisent chacune des non uniformités qui leurs sont propres.

Le placement-routage du circuit ou la proximité d'un circuit avec différentes zones du circuit peut aussi influencer la manière dont le circuit subit le procédé. La variabilité est un sujet qui concerne toutes les spécialités.

En amont de la fabrication, les concepteurs de circuits utilisent des modèles pour prédire le comportement électrique des circuits qu'ils dessinent, et ces modèles doivent permettre de prédire la dispersion des performances. Avec ces modèles, ils s'attachent à concevoir des circuits dont les performances simulées prévoient que la production des circuits atteindra un certain seuil de rendement.

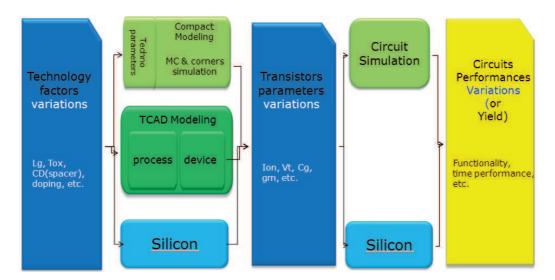

Il existe différentes méthodes de simulation de la variabilité, avec différents niveaux de complexité. Certaines s'appliquent aux simulations de circuits complexes, d'autres aux simulations de petits circuits standards, et celles auxquelles nous nous intéressons en particuliers sont les simulations du transistor métal—oxyde—semiconducteur MOS, composant de base des circuits intégrés.

Reproduire et prédire les variations font l'objet de recherche sur diverses méthodes de simulations. Certaines simulations se focalisent sur les sources dues aux matériaux afin de mieux comprendre les phénomènes mis en jeu. Ces résultats peuvent servir de points d'entrées pour des simulations de procédé de type éléments finis appelées TCAD et qui permettent de reproduire virtuellement les recettes de fabrication et de prédire les effets au niveau des performances électriques. Du coté des simulations de circuits, l'utilisation de méthodes Monte-Carlo et de pire-cas reste la référence. La méthode Monte-Carlo permet de propager sans simplification la variabilité des paramètres technologiques et la méthode pire-cas fournit aux concepteurs un critère de sanction des performances raisonnable en termes de temps de calcul, contrairement à la méthode Monte-Carlo lorsqu'elle est appliquée à un circuit de plusieurs millions de transistors.

Ce manuscrit commence par une introduction et un état de l'art des études faites sur la variabilité du transistor MOS et les moyens pour la simuler dans le chapitre 1 Contexte – Problématique.

Dans un premier temps, il est important de connaître expérimentalement

Introduction ix

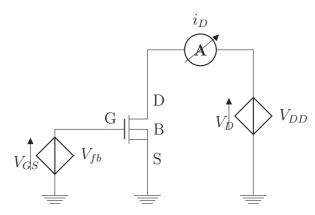

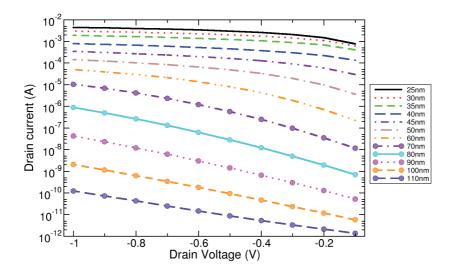

les fluctuations des facteurs technologiques. Le dopage du canal peut être mesuré par spectroscopie d'ions secondaires émis après un bombardement d'ions, mais pas sans détruire le dispositif. Cette caractérisation lourde en préparation ne permet pas un échantillonnage statistique. Dans le chapitre 2 intitulé Caractérisation du dopage des dispositifs MOSFET, nous nous intéressons au facteur de variabilité qu'est le dopage du semiconducteur. Nous proposons une méthode d'estimation du dopage canal en se basant sur des mesures électriques. Nous présentons également une méthode de calibration du dopage latéral des simulations TCAD Ainsi qu'un moyen d'obtenir une image de la dispersion des recuits thermiques sur la surface d'une plaque.

Le chapitre 3 traite de l'Étude expérimentale du nœud technologique 45 nm. Cette étude expérimentale du nœud technologique 45 nanomètres nous permet de déterminer et confirmer la liste des facteurs qui participent principalement à la variabilité des performances du transistor et nous renseigne sur les valeurs de dispersion auxquelles nous avons à faire.

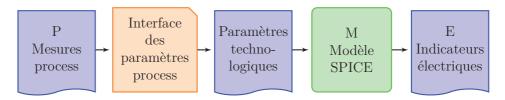

Pour finir, dans le chapitre 4 intitulé Simulation des variations dans les modèles compacts, nous proposons d'améliorer la prise en compte des déviations des facteurs process dans les simulations Monte-Carlo et pire-cas appliquées aux modèles compacts au regard d'observations expérimentales.

# Chapitre 1

# Contexte – Problématique

FIGURE 1.1 – Réplique du premier transistor réalisé aux Bell Labs.

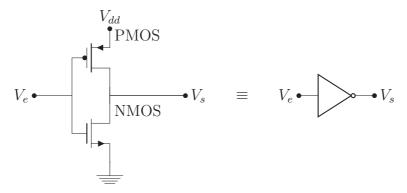

La fabrication du transistor MOS à grande échelle et à coût réduit a été rendue possible par une série d'avancées majeures dans le milieu du XX<sup>e</sup> siècle. Après l'invention du transistor <sup>1</sup> en 1947 par John Bardeen, Walter Houser Brattain et William Shockley aux Bell Laboratories [1], Gordon Teal fabrica un premier transistor en silicium en 1954 chez Texas Instruments. Le premier MOS-FET a été réalisé par Kahng [2] et Atalla [3] en 1960 au Bell Labs [4] et enfin Jean Hoerni développa en 1962 chez Fairchild Semiconductor des procédés pla-

naires que nous utilisons encore aujourd'hui pour la fabrication du dispositif MOS.

Le succès du transistor MOS tient à quelques éléments clefs : Le procédé de lithographie qui permet de fabriquer les composants comme les interconnexions, la possibilité d'utiliser l'oxide de silicium comme isolant, l'auto-alignement du transistor autour de sa grille et l'association de dispositifs complémentaires dans les circuits logiques.

Depuis, la course à la miniaturisation, pour augmenter le nombre de puces

<sup>1.</sup> Transistor est un mot-valise pour transfer resistor :

<sup>«</sup> The way I provided the name, was to think of what the device did. And at that time, it was supposed to be the dual of the vacuum tube. The vacuum tube had transconductance, so the transistor would have *transresistance*. And the name should fit in with the names of other devices, such as *varistor* and *thermistor*. And... I suggested the name *transistor*. » — John R. Pierce

par surface de tranche de silicium et donc augmenter la rentabilité des produits, a suivi la fameuse « loi », ennoncé par Gordon Moore, co-fondateur de Intel, en 1965 dans *Electronics magazine* qui prévoit que le nombre de transistors par puce va doubler tous les deux ans. Cette augmentation passe par la diminution des dimensions de ces composants. De dimensions de l'ordre du micromètre dans les années 70 [5], les dimensions nominales des récents microprocesseurs atteignent 32 nm, le noeud technologique 22 nm étant prévu pour 2013 selon l'ITRS [6].

La fabrication de circuits électroniques intégrés est une longue succession de procédés appliqués à une tranche de silicium monocristallin, ou wafer, sciée dans un lingot créé par la méthode Czochralski. La méthode Czochralski (CZ) qui est utilisée pour créer un cristal consiste à plonger un petit morceau de silicum monocristallin, la graine, à la surface de silicium en fusion<sup>2</sup> dans un creuset en rotation<sup>3</sup>. La graine, montée avec une orientation cristalline précise sur une tige en rotation dans le sens opposé, est mise en contact avec la surface du liquide. En refroidissant lentement, le silicium en fusion se solidifie en suivant la structure cristalline de la graine. Le cristal se forme au fur et à mesure de la remontée de la tige sur laquelle il est monté. Le diamètre du lingot est déterminé par le contrôle des vitesses de rotation, de tirage vers le haut et de la température. Les diamètres utilisés aujourd'hui sont 200 mm et 300 mm. L'utilisation de wafers de 450 mm est prévu pour 2012 [8]. Une fois que le lingot a fini de croître et qu'il a refroidi, il est scié en tranches de 200 µm à 800 µm. Les tranches sont ensuite arrondies sur leur bord et leur surface est polie par CMP (Chemical Mechanical Polishing) jusqu'à atteindre le niveau de planéité requis. Un certain nombre de méplats ou d'encoches sont faits sur le bord des plaques pour indiquer le type de dopage

FIGURE 1.2 – Un lingot de silicium. À l'extrémité supérieure se trouvait la graine, ou cristal initial à partir duquel a crû le cylindre entier.

<sup>2.</sup> La température de fusion du silicium est de 1414 °C.

<sup>3.</sup> Voir http://youtu.be/aWVywhzuHnQ, une vidéo montrant le procédé de fabrication des wafers (de 0 :59 à 4 :20) mais également la page d'explication du fabricant de wafers MEMC (en anglais) : [7]

et l'orientation du cristal. Le silicium à partir duquel est fait le wafer peut être initialement dopé, N ou P, à des niveaux de l'ordre de  $10^{13}$  cm<sup>-3</sup> à  $10^{16}$  cm<sup>-3</sup>.

Dans cette succession de procédés ou process qui est le terme anglais courament employé, on trouve la fabrication des dispositifs de base tels que les transistors, les éléments passifs (capacités, inductances, résistances) et les connexions métalliques. On répartit tous ces dispositifs sur différentes couches empilées les unes après les autres sur le substrat de silicium, en fonction des procédés requis par chaque dispositif. Le nombre de niveaux utilisés dépend de la complexité du circuit, en particulier des interconnexions.

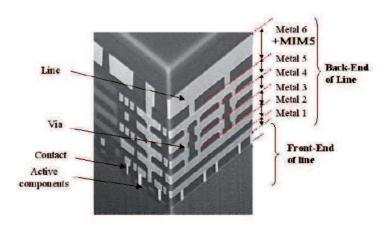

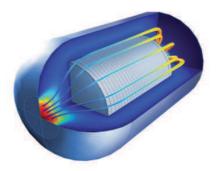

FIGURE 1.3 – Empilement des niveaux dans une technologie CMOS 0,25  $\mu$ m avec 6 niveaux d'interconnexions en cuivre [9].

Les transistors et les capacités de type MOS sont fabriqués dans le premier niveau, et donc en premier à partir de la plaque de silicium initiale. On appelle ce niveau et l'ensemble de ce qui s'y trouve le front-end of line. Dans les niveaux suivants on trouvera les interconnexions, et parmi les niveaux d'interconnexions supérieurs on trouvera des composants passifs comme des inductances ou des capacités MIM par exemple. On appelle ces niveaux et l'ensemble de ce qui s'y trouve le back-end of line  $^4$ . Les différents niveaux sont connectés entre eux par des vias. Ce sont des colonnes de métal. La figure 1.3 donne un aperçu de ces empilements dans une technologie CMOS 0,25  $\mu$ m

<sup>4.</sup> Back-end of line (BEOL) et front-end of line (FEOL) ne doivent pas être confondus avec back-end of chip et front-end of chip qui sont respectivement la mise en boitier du circuit intégré et sa fabrication.

avec 6 niveaux d'interconnexions. Après la réalisation du circuit, la plaque est sciée pour séparer les puces (chip) qui vont être mises en boitier. Nous nous intéresserons ici au *front-end of line*, là où sont réalisés les transistors.

# 1.1 La variabilité et ses conséquences

La miniaturisation du transistor se traduit par une diminution de la longueur de grille et de la largeur du composant. Ces réductions de dimensions impliquent la réduction de l'épaisseur d'oxyde de grille, l'augmentation des dopages et la diminution des tensions de fonctionnement.

Depuis le transistor simple tel qu'il a été inventé, il a fallu ajouter lors des passages à de nouveaux noeuds technologiques des caractéristiques techniques pour contrebalancer les effets qui apparaissent avec la miniaturisation. Ces étapes du procédé de fabrication supplémentaires sont, par exemple, un dopage anti-perçage, un dopage d'ajustement de la tension de seuil  $V_{\rm th}$ , des régions ldd légèrement, accompagnées d'espaceurs pour repousser les implants source/drain. Ce sont autant de nouvelles sources de fluctuations des performances.

Dans une première approche, on peut voir que si une dimension D d'un transistor diminue, alors les variations  $\Delta D$  de cette dimension vont représenter une part  $\Delta D/D$  croissante. Le comportement électrique du transistor étant fonction de ces paramètres technologiques qui ont servi à sa fabrication, ses fluctuations augmentent aussi. On pourrait penser que les outils progressent sur la répétabilité autant que sur la miniaturisation, mais d'une part, rien ne garantit que ces progrès aillent de pair, et d'autre part l'augmentation de  $\Delta D/D$  n'est pas le seul mécanisme de la dégradation de la variabilité.

La dispersion d'une performance électrique est le produit de la dispersion d'un paramètre technologique auquel elle est sensible par la sensibilité les liant. Pour une performance y et un seul paramètre technologique  $\theta$ , on peut écrire :

$$\Delta_y = \frac{dy}{d\theta} \cdot \Delta_\theta \tag{1.1}$$

en faisant l'hypothèse d'une relation linéaire entre y et  $\theta$ . Dans le cas de N

paramètres technologiques indépendants, donc orthogonaux, on a :

$$\Delta_y^2 = \sum_{i=1}^N \left( \frac{\partial y}{\partial \theta} \cdot \Delta_\theta \right)^2. \tag{1.2}$$

L'augmentation de la variabilité peut donc venir de l'augmentation de  $\Delta_{\theta}$  comme de l'augmentation de la sensibilité  $\partial y/\partial \theta$ . Sitte et al. comparent les sensibilités de dispositifs de 1,5 µm et 0,1 µm [11]. Ils observent avec le passage d'un grand transistor à un petit, l'augmentation des déviations des performances et l'augmentation des sensibilités des performances avec même un changement de signe dans certains cas. Cela montre la nécéssité de mettre à jour les informations sur les fluctuations à chaque nouveau noeud technologique. Ils vérifient aussi l'indépendance des paramètres technologiques qui s'explique principalement par le fait que les étapes de fabrication sont séquentielles.

Les technologues ont la possibilité d'agir sur les deux éléments, déviations technologiques et sensibilité du dispositif à ces variations. Ils doivent réussir à réduire les variations des procédés afin de réduire les déviations électriques au niveau des composants et, en ce qui nous concerne, au niveau du transistor MOS. Ceci passe par une meilleure maîtrise des outils de production par les ateliers.

Ils peuvent également améliorer la robustesse du dispositif en trouvant la combinaison des réglages qui réduisent les sensibilités ou remplacer quelques point-clefs du process. Intel l'a fait au noeud 45 nm avec un isolant de grille high- $\kappa$  et un matériau de grille métallique qui permettent de réduire les fuites d'isolant de grille. Ce procédé permet de s'affranchir de la désertion du polysilicium de grille tout en ayant une épaisseur physique supérieure pour une même capacité [12, 13]. La variation du travail de sortie  $^5$  a été reportée comme étant une source de variation dans les dispositifs à grille métallique [14].

Des architectures structurellement différentes sont également à l'étude pour remplacer le dispositif planaire tel qu'il existe depuis cinquante ans. Asenov et al., étudient les couches de dopage delta [15]. Ils montrent que ces structures à canaux épitaxiés, formant une couche de dopage delta peu dopée, de l'ordre de  $10^{15} \, \mathrm{cm}^{-3}$ , sont plus robustes. Une solution radicale

<sup>5.</sup> différence d'énergie entre le niveau de Fermi du matériau et le niveau d'énergie du vide, utilisé comme référence.

pour supprimer la source de variation qui resulte du placement aléatoire des dopants serait d'avoir un canal non dopé, mais pour garder le contrôle électrostatique, il faut imaginer de nouvelles architectures. L'isolation de la couche d'oxyde des substrats SOI (Silicon On Insulator) permet de réduire le dopage du canal partiellement ou complètement déserté, réduisant ainsi le désappariement [16, 17]. L'utilisation de transistor à double grille, triple grille, quadruple grille ou gate all around permet de réduire fortement le dopage canal mais introduit d'autres sources de variation comme celles liées à la géométrie du dispositif [18] .

Dans les dispositifs SOI, la réduction du dopage permet un gain sur la variation des performances. Les dispersions de longueur de grille et d'épaisseur de silicium sont attendues comme une limitation dans ces dispositifs [19].

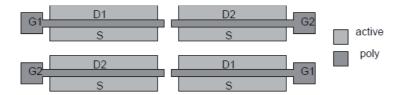

Les concepteurs de circuits, les designers, subissent cette variabilité des procédés. Ils ne contrôlent pas les marges sur les performances des composants (transistors, résistances, etc.) du circuit qu'ils dessinent. Ils doivent pour autant s'assurer que les circuits qu'ils conçoivent présenteront des performances dont les dispersions seront dans les marges requises par le cahier des charges avec un rendement maximum. Pour cela, ils peuvent rendre plus robuste leur circuit, c'est à dire réduire sa sensibilité aux fluctuations de la technologie, grâce à des méthodes de conception [20] ou des méthodes d'optimisation du circuit [21, 22]. Du coté du placement des circuits – le layout – on peut citer la technique appelé common centroid permettant de compenser les effets d'un gradient spatial de paramètre technologique en dessinant les composants de manières symétrique (figure 1.4). Cette compensation des effets

FIGURE 1.4 – Placement de 2 transistors en common centroid. Les transistors 1 et 2 ont été séparés chacun en une somme de deux transistors qui sont placés de manière symétrique par rapport au centre du dessin du circuit. Les gradients spatiaux de paramètres sont ainsi autocompensés autour de la valeurs centrale du paramètre. [23]

spatiaux améliore en particulier l'appariement des dispositifs dont la surface est grande et où l'amplitude des variations de paramètres est significative.

Elzinga utilise des structures de tests suivant ce placement des transistors avec un accès indépendant aux quatre transistors pour différencier les effets totalement aléatoires des effets paramétriques spatiaux [24]. Les transistors par paires cablés côte-à-côte – horizontalement ou verticalement – présentent des effets aléatoires et paramétriques, tandis que les paires cablées de façon croisées masquent les effets paramétriques et ne présentent que des effets aléatoires.

En général, ces techniques de compensation par la conception ou le dessin impliquent des circuits plus complexes qui utilisent plus de composants et de surface de silicium. Donc, non seulement la variabilité réduit les rendements de production mais elle peut augmenter le coût des circuits en réduisant leur densité d'intégration. Pour s'assurer que le circuit sera conforme au rendement attendu, les concepteurs utilisent les fonctions de prédiction de la variabilité que leur offrent les modèles de simulation.

Le travail des modélistes consiste à développer des modèles de transistors prenant en compte la variabilité des dispositifs afin que les concepteurs puissent simuler le comportement statistique des performances critiques de leur circuit. Nous verrons en section 1.3 les différentes méthodes possibles. Les méthodes de simulation les plus courament employées restent le « tir Monte-Carlo » et les « pire-cas » – appelés courrament corner. Dans tous les cas, créer des modèles prenant en compte la variabilité nécessite de connaître les sources et de comprendre leurs comportements.

## 1.2 Sources de déviation

### 1.2.1 Observations des effets

Le manque de répétabilité des performances d'un transistor à un autre, conçus identiquement, peuvent se manifester de différentes manières. Les différentes sources de variations agissent à des échelles différentes selon leur nature et s'observent différement.

Croon et al. étudient l'influence de la méthode de caractérisation de la tension de seuil  $V_{\rm th}$  [25]. En effet, la précision de la mesure peut apparaître dans les résultats comme un phénomène de désappariement mais sa nature est différente et il ne faut pas confondre ces effets. Ils comparent en termes de répétabilité et d'erreur systématique quatre appareils de mesures et cinq méthodes d'extraction du  $V_{\rm th}$ : a) pente maximum, b) méthode trois points,

c) méthode quatre points, d) méthode à courant constant et e) méthode d'ajustement du désappariement du courant. Ils concluent que chaque méthode peut donner de bon résultats tant qu'elle est définie avec soin, mais la méthode trois points semble plus sure.

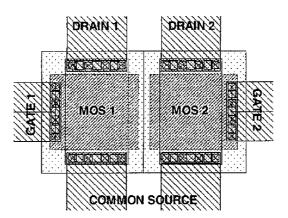

#### Au niveau local

À des distances de l'ordre de la taille d'un transistor, les différences d'accord, ou d'appariement <sup>6</sup> sont de nature aléatoire et sont attribuées aux variations locales des matériaux constituant les composants : silicium dopé, polysilicium, oxyde de grille principalement. L'appariement est mesuré sur des paires de transistors identiques et dessinés côte à côte afin de s'affranchir des sources de variations intervenant à plus grande distance. La figure 1.5 montre le placement d'une paire de transistors.

FIGURE 1.5 – Une paire de transistors identiques, placés au plus proche l'un de l'autre. La différence de caractéristiques électriques entre les deux est reconnue comme étant uniquement aléatoire car leurs paramètres de fabrication sont considérés identiques à cette distance minimale. [26]

Le désappariement provenant de ce type d'observation a pour cause une certaine quantité d'un même phénomène dont les effets sont tellement petits qu'ils peuvent être sommés. Leur distance de corrélation étant inférieure aux dimensions du transistor, le théorème centrale limite explique que les déviations engendrées par ces causes suivent une distribution normale, *i.e.* de loi gausssienne. Leur représentation fréquentielle est un bruit blanc (un

<sup>6.</sup> Pour le désappariement entre deux transitors identiques on utilise le terme anglais de mismatch (du verbe  $to\ match$ : correspondre à).

spectre continu). Les variations de performances en fonction du placement des transistors qui apparaissent à l'échelle d'une puce ou à l'échelle d'une tranche de silicium ont un spectre spatial composé de basses fréquences. Pelgrom et al. expriment, via l'espace de Fourier, l'écart type d'une performance du transistor causé par ces deux types de sources indépendantes [27]:

$$\sigma(\Delta P)^2 = \frac{A_P^2}{WL} + S_P^2 D_x^2 \tag{1.3}$$

où l'écart-type des déviations du paramètre P dépend d'une part de l'inverse de la surface du transistor pour les variations aléatoires (via le coefficient  $A_P$  dépendant de la technologie) et dépends de la distance entre les deux transistors considérés (via le paramètre  $S_P$ ). La figure 1.5 montre une paire de transistors utilisée pour caractériser de cette variabilité. La distance entre les deux transistors est minimale. Par conséquent seul le premier terme de (1.3) reste :

$$\sigma(\Delta P) = \frac{A_P}{\sqrt{WL}}.\tag{1.4}$$

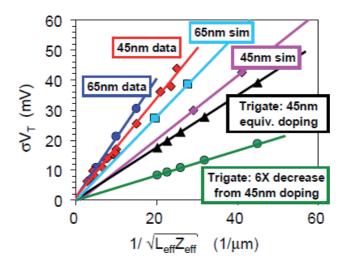

On appelle aujourd'hui couramment (1.4) la loi de Pelgrom et le tracé de  $\sigma(\Delta P)$  en fonction de  $1/\sqrt{WL}$  un graphe de Pelgrom. La figure 1.6 est un graphe de Pelgrom du  $V_{th}$  de différentes technologies. La croissance de l'écart-type de  $V_{th}$  est linéaire en fonction de l'inverse de la racine de la surface. Le facteur  $A_{V_{th}}$  sert d'indicateur de la robustesse de telle ou telle technologie.

## À l'échelle d'une puce

À cette échelle interviennent des sources modélisées par le second terme de l'équation (1.3), ce sont les gradients des paramètres technologiques sur la superficie de la tranche de silicium. Une autre source intervenant à cette échelle est l'interaction de la conception du circuit sur le procédé. Les paramètres de placement des éléments du circuit vont influencer le déroulement des étapes de fabrication. On peut citer :

- le nombre de grilles d'un transistor,

- la distance entre un transistor et ses voisins,

- l'orientation des dispositifs,

- la forme de la zone active,

- la largeur des tranchées d'isolation,...

FIGURE 1.6 – Graphe de Pelgrom du  $V_{\rm th}$  de différentes technologies mesurées ou simulées [13].

Ces paramètres relèvent du choix des concepteurs lors du placement routage de leur circuit – qu'on appellera couramment *layout*. Il a été montré que l'utilisation de dessins les plus réguliers possibles permet de minimiser ce genre de variations [28, 29, 30, 31].

Il est nécessaire pour mesurer ces effets de prévoir des structures de test à l'intérieur des puces et pas uniquement entre les puces sur les chemins de découpe comme il est courant de le faire pour la variabilité de puce à puce. L'étude expérimentale des différents effets de layout augmente considérablement le nombre de transistors à mesurer. Aussi, pour gagner en surface, on peut multiplexer ces structures et n'utiliser qu'un jeu de plots de mesure par groupe de structure de test pour poser les pointes de mesure [32]. Une étape de calibrage afin de retirer les contributions parasites des lignes d'accès est alors nécessaire.

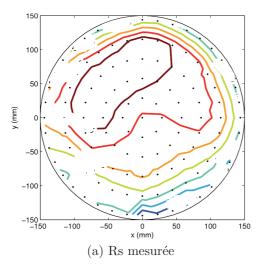

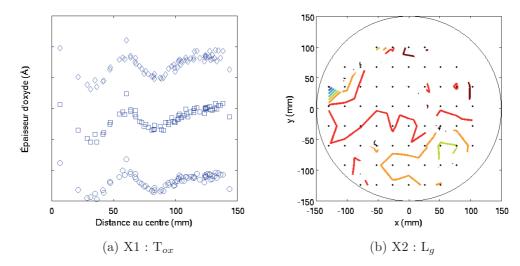

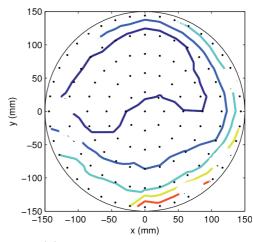

# À l'échelle d'une plaque

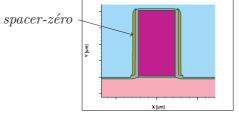

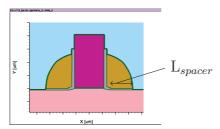

De puce à puce, les variations de paramètres existent lorsqu'un paramètre technologique varie d'un endroit à l'autre de la plaque, comme par exemple l'épaisseur d'oxyde déposé avant l'implantation des  $ldd^7$  représentée sur la figure 1.7. L'étendue et les motifs typiques de ces variations peuvent tout

<sup>7.</sup> lightly doped drain ou drain dopé légèrement. Ce sont les extensions des implants source/drain dans le canal.

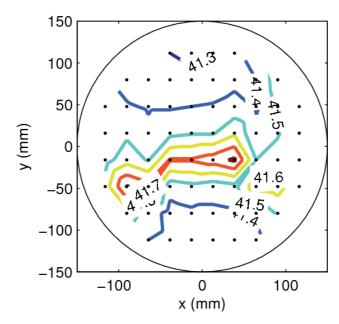

FIGURE 1.7 – Répartition spatiale de l'épaisseur d'oxyde liner mesurée sur la plaque n° 5 d'un lot de 12 plaques. Les variations suivent un motif radial et la plage de variation est de 0.3%.

à fait être connues pour les paramètres mesurables. Cependant, du fait que ces variations interviennent d'une puce à l'autre, on ne peut pas les intégrer de manière déterministe dans la chaine de simulation. En effet, les variations locales et intra-puce (cf. précédemment) font partie de la conception d'un même circuit. On peut donc dans une certaine mesure modéliser et prévoir le comportement de ces transistors, situé aux différents endroits de la puce et dont l'environnement est connu. Par contre les puces ne gardent pas l'information de leur position sur la tranche de silicium une fois qu'elles sont découpées. Ces variations ne peuvent donc être simulées que de manière statistique.

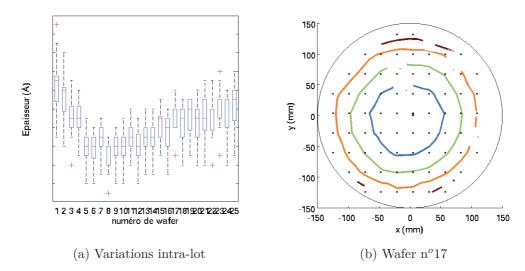

#### À l'échelle d'un lot

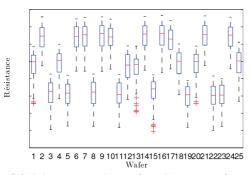

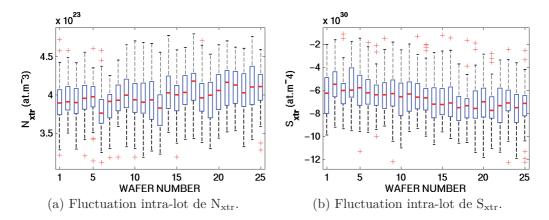

On peut noter que sur les 25 plaques – ou wafer – constituant un lot, les paramètres technologiques changent aussi. Certaines étapes technologiques se font plaque par plaque alors que d'autres se font simultanément – par batch –, c'est à dire 25 wafers dans la même machine. Dans le premier cas la répétabilité de l'opération seule importe, dans le second s'ajoute l'homogénéité spatiale de l'opération à l'intérieur de la machine. La figure 1.8 montre

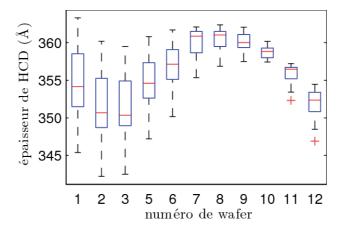

les variations entre plaques de l'épaisseur de nitrure déposée pour la formation des espaceurs dans une technologie 45 nm en cours de développement. Chaque boite à moustache  $^8$  représente la mesure de la population intraplaque. On peut observer d'une plaque à l'autre l'évolution de la médiane qui rend compte de la variabilité W2W-wafer to wafer. On observe aussi que l'uniformité du dépot évolue d'un bout à l'autre d'un lot.

FIGURE 1.8 – Boites à moustaches représentant la population du paramètre  $\mathrm{HCD}_{th}$  par plaque, pour les 12 plaques d'un lot. Cette visualisation permet de comparer les variations à l'intérieur d'une plaque et dans un lot. La tendance de la médiane sur les 25 plaques est une signature des équipements servant à cette étape de dépot de nitrure.

## Mesures

Les grandeurs technologiques que l'on peut mesurer directement et de manière non destructive sont les épaisseurs des différentes couches (dépots ou oxyde thermique) et les largeurs (dimensions critiques ou CD, *Critical Dimensions*). Les épaisseurs sont mesurées par ellipsométrie. Le principe de l'ellipsométrie est de mesurer la polarisation d'une onde lumineuse de polarisation initiale connue après sa réflexion sur la surface à analyser. Les mesures de largeur se font par microscopie SEM (Scanning Electron Microscopy) ou par ellipsométrie spectroscopique (SCD, Spectroscopic Critical Dimension). Les grandeurs technologiques sont mesurées *en ligne*, c'est à dire entre deux étapes du procédé de fabrication, tant que la mesure est possible.

<sup>8.</sup> Voir A.12, page 137

Pour mesurer les profils de dopages, on utilise la technique des SIMS qui consiste en l'analyse par spectrométrie de masse d'ions secondaires éjectés de la surface par le bombardement d'un faisceau d'ions primaires. Ce faisceau présente un rayon d'un micron environ et les ions utilisés peuvent être le césium  $Cs^+$  ou  $l'O_2^+$  selon les espèces mesurées. La mesure permet de compter le nombre d'ions secondaires par seconde. Un échantillon étalon est nécessaire pour calibrer quantitativement les résultats. Après la mesure de la profondeur creusée par le faisceau, on peut remonter au profil de la concentration de dopants en fonction de la profondeur par proportionalité. Ce type de mesures nécessite la préparation de l'échantillon qui sera par conséquent détruit [33, 34].

Les mesures électriques se font après la fin du procédé de fabrication. Les structures de tests sont conçues avec des plots d'accès, c'est à dire des petites surfaces de métal où l'on vient poser les pointes des appareils de mesures. Des méthodes de multiplexages sont mises en œuvre pour accéder à plusieurs structures de test par les mêmes plots de mesures afin d'économiser de la surface [35].

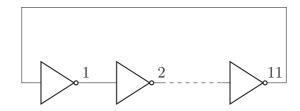

Vickers rapporte le développement d'une technique de mesure sans contact [36]. Il présente un oscillateur en anneau comme structure de test, alimentée *via* un laser par une photodiode et dont la fréquence d'oscillation est déterminée par une mesure radiofréquence.

# 1.2.2 Sources intrinsèques

Une partie des sources de variabilité n'est pas attribuable au procédé de fabrication mais est causée par les matériaux constituant le transistor. Si, pour des dispositifs de grande dimension, les propriétés paraissent continues, dans les dispositifs décananométriques, les imperfections des matériaux et leurs propriétés à l'échelle locale voire atomique sont à prendre en compte. Les conséquences des ces imperfections ont été étudiées par simulation par plusieurs équipes de recherche.

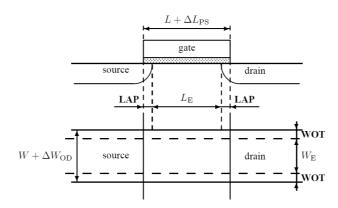

#### Rugosité de ligne de grille

Le trait de polysilicium formant la grille du transistor n'est pas un parallélépipède parfait. Ses bords verticaux en particulier ne sont pas parfaitement plans et souffrent de ce qu'on appelle la rugosité du bord de ligne – *Line Edge Roughness* ou LER – qui entraine une variation de la longueur effective du canal dans la direction correspondant à la largeur du transistor. En effet, la grille en polysilicium sert de masque lors de l'implantation des ldd et positionne donc les jonctions canal-source/drain. C'est le principe d'autoalignement.

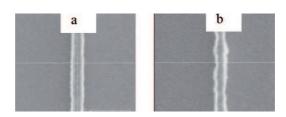

FIGURE 1.9 – Image SEM de traits de polysilicium. On voit nettement l'imperfection du bord de grille [37].

FIGURE 1.10 – Exemple de faible (a) et forte (b) rugosité de ligne [38].

On définit la LER par l'écart type de la largeur du trait de polysilicium [39]. Selon le positionnement et l'étendue de ces mesures, on observe sur une courte étendue des variations plutôt hautes fréquences et sur une étendue supérieure à une longueur caractéristique, dépendante de la technologie, la somme quadratique de variations basses fréquences et hautes fréquences [39, figure 2]. Cependant, l'influence de l'écart-type de la longueur de grille se moyenne quand le dispositif est plus large, et décroît naturellement pour le transistor long de par sa dépendance en  $\Delta L/L$ .

Difrenza et al. [40] montrent que la fluctuation des dopants n'est pas la seule source de désappariement et mettent en évidence l'impact de la rugosité du trait de polysilicium. Ils différencient aussi l'effet statistique de la réduction des dimensions et du changement de sensibilité à la longueur de grille qui en résulte. En effet, dans les canaux courts où la tension de seuil chute, la sensibilité  $\partial V_t/\partial L$  augmente nettement.

L'origine de cette rugosité est attribuée au développement de la résine servant de masque pour la grille. Les propriétés du matériau polymère de la résine du masque, les propriétés optiques de la lumière utilisée pour insoler le masque et l'ensemble optique sont incriminés. Des traitements de cette résine ont été proposés pour améliorer la LER, comme un dépot par dessus la résine gravée ou encore un traitement thermique [41, 42]. Une surgravure de la grille est aussi proposée pour réduire la composante haute-fréquence de

la rugosité [43]. Pargon et~al. montrent que l'utilisation de masque en  $SiO_2$  ou en carbone amorphe aide à réduire la rugosité du bord de grille [44].

Asenov et al. étudient cette source par simulation 3D [45]. Le profil de la grille est caractérisé par une amplitude moyenne et une longueur de corrélation. À partir de ces deux paramètres, ils génèrent aléatoirement des profils de grille qu'ils utilisent pour des simulations Monte-Carlo de courants de transistors de différentes dimensions. Ils prévoient une variation  $\sigma/\mu$  de I<sub>on</sub> de 8% pour des dispositifs de 50 nm de large et 30 nm de long avec une forte dépendance à longueur de grille ( $\propto 1/L$ ).

Linton et al. prévoient à partir d'un modèle de transistor en parrallèle que  $\sigma_{\rm LER}$  devra être réduit à 1 nm au noeud 32 nm pour que son influence sur la variation du courant n'augmente pas par rapport au noeud 80 nm [38]. Ils proposent aussi, à partir de ce modèle, une méthode pour extraire des mesures la part de variation attribuable à la LER.

### Pincement du potentiel de surface par les joints de grain du polysilicium

La grille est faite de silicium polycristallin – ou polysilicium – qui est composé de petits cristaux d'orientations différentes. Pendant le dépot du matériau, la croissance du cristal démarre à plusieurs endroits en même temps avec des orientations aléatoires. À partir de ces points, des cristaux croissent jusqu'à être en contact. On parle de joints de grains pour ces surfaces de contact. La taille des grains est également aléatoire.

Les propriétés électriques locales du matériau aux joints sont différentes de celles du cristal lui-même. En particulier, à l'interface entre le polysilicium de grille et l'isolant, le travail de sortie du matériau se trouve modifié le long des joints de grains. Le potentiel de surface et la tension de seuil sont impactés en conséquence.

Difrenza et al. observent expérimentalement l'importance du procédé de formation de la grille dans les déviations de  $V_{th}$  en comparant le matériau déposé (silicium amorphe ou polycristallin) et le type de recuit (en four ou recuit rapide). Ils construisent un modèle compact afin d'évaluer la contribution de ce phénomène [46]. Ils prennent en compte un dopage différent sur les joints de grain et sur les parties cristallines du polysilicium qui implique un écart de  $V_{th}$  via une zone de déplétion dans les parties moins dopées. Ils différencient l'effet du nombre de grains par rapport au nombre de dopants

grâce à la dépendance en  $V_{\rm B}$  des modèles qu'ils ont écrit pour le nombre de dopants et le nombre de grains.

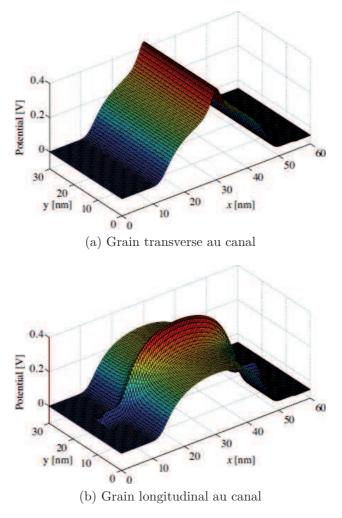

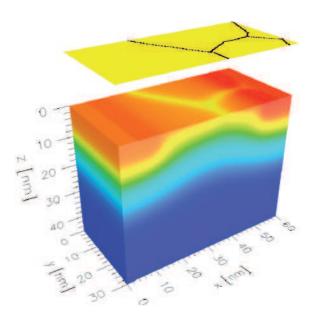

Asenov montre comment le placement aléatoire des joints de grains et en particulier leur orientation influencent le courant du dispositif. Il montre les cas extrêmes de deux transistors ayant un joint de grain dans la grille [47, 48]. Sur l'un, le joint est longitudinal aux sens du canal, dans l'autre il est transversal (figure 1.11). La barrière de potentiel du premier est augmentée sur toute la largeur du canal alors que celle du second n'est surelevée que sur la largeur d'un joint de grain.

FIGURE 1.11 – Potentiel de surface sous l'influence d'un seul joint de grain [48].

Dans les grands transistors une grande quantité de joints de grains est

FIGURE 1.12 – Échantillon d'une simulation Monte-Carlo 3D atomistique prenant en compte l'influence des joints de grains sur le potentiel de surface [48].

présente et leurs influences sur une grande surface de canal sont globalement identiques d'un transistor à l'autre. Quand les dimensions diminuent et que la surface du canal ne comporte alors que quelque joints, leurs différences d'un dispositif à l'autre deviennent très nettes et donc la variabilité du seuil de conduction augmente dans les petits dispositifs.

### Placement aléatoire des dopants

Dans des transistors de petite surface, on ne peut pas considérer que le dopage est uniforme comme dans un grand dispositif. Lors de l'implantation ionique, les atomes de dopants se répartissent globalement selon un profil bien connu à l'échelle macroscopique, mais à l'échelle microscopique leurs emplacements individuels restent aléatoires. Une concentration par exemple de  $10^{17}$  atomes/cm³ ne représente que peu d'atomes au milieu du cristal de silicium qui en contient  $5\times 10^{22}$  par centimètre cube : 2 atomes de dopants pour un million d'atomes de silicium. Pour donner un ordre de grandeur, un volume de  $W\times L=120$  nm  $\times 40$  nm sur disons 10 nm de profondeur, qui peut être le volume du canal d'un transistor de dimensions nominales,

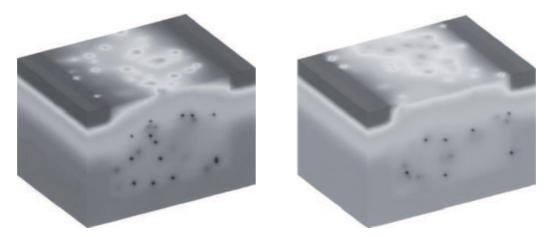

FIGURE 1.13 – Simulation de 2 transistors qui diffèrent uniquement par le positionnement local des dopants dans le canal.

contiendrait en moyenne:

$$120 \times 40 \times 10 \times 10^{-21} \,\mathrm{cm}^3 \times 10^{17} \,\mathrm{cm}^{-3} = 48000 \times 10^{-4} = 4.8 \,\mathrm{atomes}.$$

On comprend que ces cinq atomes auront un impact très différent s'il sont espacés régulièrement dans le volume ou s'ils sont plutôt regroupés au milieu du canal, ou encore sur les bords.

Plusieurs laboratoires ont développé des outils de simulation dits atomistiques, car ils calculent le potentiel électrique en prenant en compte la contribution individuelle de chaque atome dopant. Le placement des atomes dans le cristal est soit le résultat d'une simulation atomistique du process reproduisant l'implantation puis le recuit, soit un placement aléatoire suivant un profil de concentration prédéfini. Le courant électrique est ensuite calculé par un simulateur drift-diffusion utilisant le potentiel électrique calculé de manière atomistique.

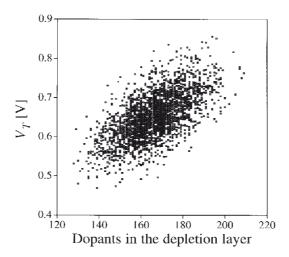

Gross et~al. montrent à partir de simulations atomistiques Monte-Carlo prenant en compte les interactions électron-électron et électron-ion que le positionnement des impuretés dans la zone de déplétion (qui occupe les 15 nm supérieur du canal) est fortement correlé au  $V_{\rm th}$ . De même, les fluctuations du courant sont très corrélées au placement des dopants dans les huit premiers

<sup>9.</sup> La densité de courant J est exprimée par la somme du courant résultant du gradient de dopage n(x) et du courant résultant du gradient de potentiel électrique E. On a  $J_n = qn(x)\mu_n E(x) + qD_n\partial n/\partial x$  pour les électrons et  $J_p = qn(x)\mu_p E(x) - qD_p\partial n/\partial x$  pour les trous, avec  $\mu$  la mobilité des porteurs et D leur coefficient de diffusion.

FIGURE 1.14 – Tensions de seuils de 2500 transistors de la figure 1.13 en fonction du nombre de dopants dans la couche de désertion [49].

nanomètres (couche d'inversion) [50].

Sano et al., puis Ezaki et al., proposent une décomposition du potentiel coulombien associé à chaque charge pour éviter une singularité de calcul au niveau de l'impureté en introduisant une longueur d'écrantage [51]. L'expression du potentiel est séparée en un terme d'interaction longue distance et un terme d'interaction proche. Ezaki et al. utilisent un simulateur d'implantation et de recuit pour déterminer le placement des impuretés [52].

Dollfus et al. développent aussi leur simulateur d'implantation/diffusion et leur simulateur atomistique [53]. Ils étudient l'influence du positionnement et du nombre de dopants dans la couche d'inversion sur le champ électrique, la concentration et la vitesse des électrons dans un transistor de dimensions  $50 \text{ nm} \times 50 \text{ nm}$ . Ils soulignent l'importance de s'intéresser aux architectures de transistors non dopés pour les technologies à venir.

De la même manière que pour le pincement du potentiel de surface, Asenov et~al. simulent plusieurs dispositifs dont la densité de dopants est identique mais dont le placement de chaque atome d'impureté reste aléatoire [49, 54, 15, 55, 56, 57]. On peut observer, sur la figure 1.13, deux dispositifs globalement identiques mais dont le placement des dopants est aléatoire. On observe les différences de potentiel de surface qui apparaissent à cause de la nature discrète du dopage. Les valeurs de  $V_{\rm th}$  obtenues à partir d'un tir Monte-Carlo de 2500 simulations de ce type présentent un écart-type de 50 mV à ces dimensions, pour une épaisseur d'oxyde de grille de 3 nm.

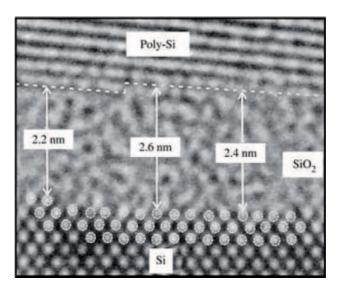

### Imperfection du diélectrique de grille

Le diélectrique de grille présente également des imperfections. En effet, les derniers nœuds technologiques emploient des épaisseurs de 2 à 3 nanomètres et les variations d'épaisseurs d'un atome sont alors significatives. L'image SEM de la figure 1.16 illustre cette variation. En plus d'apporter des fuites par effets tunnel direct à travers l'oxyde [58], cette rugosité de l'interface apporte sa part de variabilité.

FIGURE 1.15 – Simulation prenant en compte les irrégularités de la surface  ${\rm SiO_2/Si~[59]}$ . On peut observer séparement de haut en bas l'irrégularité de la surface oxyde/silicium, une isosurface de niveau de dopage de  $10^{17}\,{\rm cm^{-3}}$  et la distribution de potentiel à la surface du canal.

L'interface  $\mathrm{SiO}_2/\mathrm{Si}$  est affectée par la surface du cristal de silicium dont les sauts d'un plan atomique à l'autre sont de l'ordre de 0,2–0,3 nm pour le plan (001) [59]. La figure 1.15 montre une simulation prenant en compte cette interface imparfaite [59]. Dans ce travail, la surface est modélisée grâce à une fonction d'autocorrélation gaussienne ou exponentielle, paramétrée avec une longueur d'autocorrélation  $\Lambda$  et une hauteur moyenne  $\Delta$ . On note que  $\Delta$  et  $\Lambda$  sont determinés à partir d'image TEM et AFM. Le potentiel de surface du dispositif subit des variations locales aléatoires qui causent une déviation de la tension de seuil du dispositif. Sur ce dispositif de 30 nm×30 nm avec un oxyde d'épaisseur moyenne de 1,05 nm, un tir Monte-Carlo sur 200 échantillons prévoit un écart-type de la tension de seuil pouvant aller jusqu'à 25 mV sur ce dispositif selon les paramètres de rugosité utilisés. L'influence de cette rugosité augmente aussi avec le niveau de dopage mais les variations de ces

FIGURE 1.16 – Image SEM de l'oxyde de grille illustrant les imperfections d'épaisseur [60].

deux effets agissent indépendamment.

## 1.2.3 Sources originaires du dessin

La topologie dessinée impacte les chemins critiques des circuits numériques et les circuits analogiques (à signal mixte ou radiofréquences) à travers les effets de proximités dépendants du dessin (STI, WPE, lithographie...).

#### Orientation

L'orientation des dispositifs place les transistors dans des situations différentes vis-à-vis du cristal dont les propriétés électriques ne sont pas isotropes. La mobilité est différente selon le plan choisi pour la surface du silicium et pour l'orientation du canal [62]. Le tableau 1.1 rappelle les mobilités maximales pour différents plans de surface de la tranche de silicium et différentes orientations du canal.

Pelgrom *et al.* rapportent une augmentation d'un facteur 5 du coefficient de désappariement lorsque les paires de transistors mesurés sont perpendiculaires et non pas parallèles [27].

On a vu que les effets systématiques dus au placement peuvent être en partie modélisés et donc pris en compte dans la simulation du circuit, au coût

| NMOS                                            |                       |  |                                 |

|-------------------------------------------------|-----------------------|--|---------------------------------|

| Substrat Canal Mobilité max. $(cm^2/V \cdot s)$ | (100)<br>[110]<br>380 |  | (111)<br>(20) [112]<br>(40) 280 |

| PMOS                                            |                       |  |                                 |

| Substrat Canal Mobilité max. $(cm^2/V \cdot s)$ | (100)<br>[110]<br>80  |  | (111)<br>(20) [112]<br>(20) 120 |

TABLE 1.1 – Mobilité maximale selon les orientations [62]. La mobilité est fonction du champ vertical et de la température. Seules les valeurs maximum sont rapportées ici.

d'un effort de caractérisation de structures de test dédiées. D'autres effets du layout sont ré-évalués par simulation numérique après le placement.

### Perturbation de la lithographie

En plus du caractère aléatoire du bord de trait de polysilicium dont nous avons parlé au paragraphe 1.2.2, page 13, l'étape de révélation de la résine de lithographie est influencée par le routage des circuits. Les échelles atteintes par les motifs des transistors modernes sont de l'ordre de la longueur d'onde de la lumière utilisée (193 nm). La forme ou le degré de proximité des lignes de polysilicium vont affecter l'énergie reçue par une zone de la couche de résine et donc la forme finale de la résine après révélation. Par exemple les bouts de lignes et les angles vont être arrondis, la largeur du trait peut varier en fonction de la distance avec le trait voisin. Un motif trop fin ne s'imprimera pas du fait que sa résine aura été irradiée par les zones voisines etc. Pour contrebalancer cela, on met en place des techniques d'amélioration de la résolution - RET pour Resolution Enhancement Technics. On trouve en premier lieu les corrections optiques de proximité – OPC pour Optical Proximity Correction – dont le principe est de modifier le masque de manière à anticiper les effets non voulus de l'illumination de la résine. Les masques à décalage de phase – PSM pour Phase Shift Mask [63] –, quant à eux, permettent de graver au delà de la résolution optique en plaçant en opposition de phase deux zones encadrant un motif fin.

La figure 1.17 montre un exemple de masque rectangle avec et sans cor-

rection optique. Le motif du masque initialement rectangle produira sur la résine une forme dégradée par rapport à la forme souhaitée par les concepteurs. Les corrections apportées au masque entre la conception du circuit et la lithographie modifient en particulier les angles du rectangle et ajoutent des motifs pour contrôler l'environnement optique du rectangle.

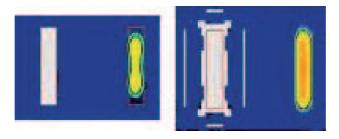

FIGURE 1.17 – Correction de proximité optique. À gauche, sans correction, le motif initial rectangle est arrondi et raccourci après exposition et révélation de la résine. L'échelle de couleur indique le taux de révélation de la résine. À droite, avec correction, la forme du motif sur le masque anticipe les dégradations et permet un motif proche du rectangle intial voulu [64].

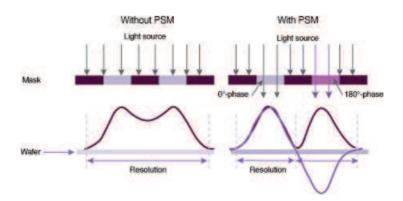

FIGURE 1.18 – Principe du masque à décalage de phase [65]. En mettant en opposition de phase les ondes passant à droite et à gauche du motif à imprimer, on conserve une zone d'ombre sur le motif en question. On augmente ainsi la résolution maximale.

La figure 1.18 montre le principe de la technique PSM. Sans PSM, à gauche, un motif trop étroit reçoit de l'énergie des zones voisines par diffraction. En effet la longueur d'onde est relativement trop grande et le seuil d'énergie nécessaire pour permettre la dissolution de la résine est dépassé. Par conséquent, le motif sera effacé à la révélation de la résine. La méthode

PSM à droite permet d'obtenir deux zones en opposition de phase en cadrant le motif afin que ce dernier ne reçoive pas d'énergie non voulue. Cette technique est possible grâce à une couche déposée sur la résine et dont l'épaisseur est choisie en fonction du décalage de phase souhaité.

### Interaction entre le dessin et les variations du procédé

Le recuit arrivant en fin des procédés front-end est un recuit rapide à haute température. Le but de ce recuit est d'activer électriquement les dopants en les faisant diffuser le moins possible puisqu'on veut garder des jonctions peu profondes. Le recuit est réalisé par des lampes émettant dans le domaine du proche infrarouge. Localement sur la puce, l'absorption d'énergie dépend du matériau présent. L'absorption du silicium, de l'oxyde des régions STI et du polysilicium est différente. Il en résulte que l'énergie reçue lors du recuit dépend du dessin du circuit. L'activation et la diffusion des dopants seront donc influencése par la densité de polysilicium et d'oxyde à la surface du silicium.

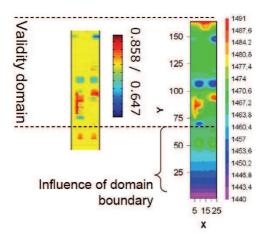

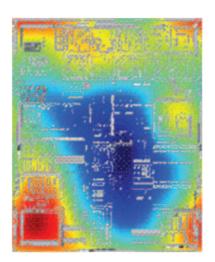

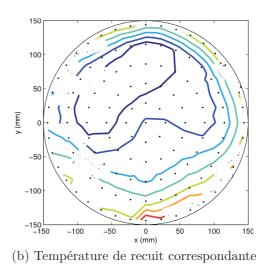

La variabilité intrapuce de la température reçue lors du recuit spike peut être évaluée par simulation optique et thermique. Fiori, Cacho et al. étudient les propriétés optiques de plusieurs motifs réguliers en fonction de la distance entre deux zones de polysilicium, de la largeur des traits de polysilicium et de la présence ou pas du STI. Ils combinent ces résultats avec les informations contenues dans le fichier GDS <sup>10</sup> afin d'évaluer les valeurs d'absorption sur un vrai circuit. La carte d'absorption est ensuite convertie en température grâce à des mesures préalablement effectuées sur des structures de test – des résistances de surface – dédiées à la corrélation entre le motif et la température, via la sensibilité de la résistance à la température. Ils étudient ainsi le recuit flash et le recuit laser [66, 67]. La figure 1.19 montre le résultat dans le cas de la simulation d'un recuit laser. Les différences de température atteignent 50 °C dans le domaine de simulation.

Dans le cas du recuit spike, il a été montré que le dépot d'une couche de carbone amorphe avant le recuit aide grandement à l'amélioration de l'uniformité du recuit [68].

<sup>10.</sup> graphic database system, le fichier décrivant les masques utilisés pour la photolithographie.

FIGURE 1.19 – Simulation de l'absorption énergétique et de la température associée lors d'un recuit laser [67]. Sur ce domaine d'étude, la température reçue varie d'une cinquantaine de degrés.

FIGURE 1.20 — Simulation de la température reçue lors d'un recuit spike [66]. Sur ce domaine d'étude, la température reçue varie de deux degrés.

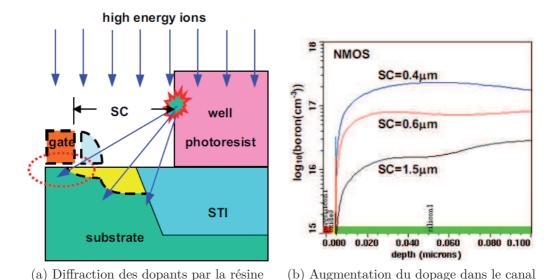

### Effet de proximité du well

En bord de  $well^{11}$ , le dopage est modifié à cause de diffractions des ions implantés. Les ions qui sont implantés sur le bord du masque sont déviés et viennent s'accumuler avec les ions normalement implantés dans le bord de la zone active, comme le montre la figure 1.21a. Ce surplus de dopants crée un gradient de dopant dans le canal [69, 70, 71]. On appelle well proximity effect (WPE) cet effet agissant en bord de well. C'est un effet systématique qui est pris en compte dans les modèles. Wils et al. montrent que cet effet n'apporte pas de variabilité supplémentaire au transistor [72].

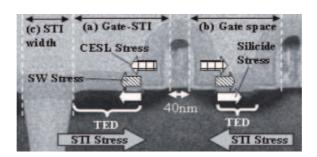

#### Influence du dessin sur le stress

Tsuno et~al. étudie l'influence de l'espacement des grilles, de la largeur des  $STI^{12}$  et de la distance entre la grille et les STI [73]. Ils modélisent les variations causées par ces facteurs systématiques par deux effets : le stress

<sup>11.</sup> Zone délimitant le dopage substrat des dispositifs

<sup>12.</sup> Shallow Trench Isolation, tranchée d'isolation peu profonde.

FIGURE 1.21 – Effet de proximité du well [70]

mécanique et la TED <sup>13</sup>. La TED varie à cause de sa proximité ou non avec l'interface silicium/oxyde des STI, où la ségrégation des interstitiels modifie localement la diffusion des dopants <sup>14</sup>. Le stress est supposé provenir du recuit de la siliciuration des source/drain et de la couche d'arrêt de gravure des

<sup>14.</sup> Cette influence sur la diffusion est dépendante de l'espèce qui diffuse, ce qui implique que les effets sont différents sur les transistors N et P.

FIGURE 1.22 – Les performances du transistors sont influencées par des paramètres d'instance du transistor comme la distance entre grilles, la distance grille-STI, la largeur des STI, via leurs influences sur le stress et la diffusion. [73]

<sup>13.</sup> Transient Enhanced Diffusion, Diffusion accélérée transitoire. Un mécanisme de diffusion des dopants accélérés par leurs interactions avec la diffusion des défauts de silicium interstitiels. Une fois que tous les défauts sont réparés, la diffusion n'est plus accélérée, d'où son nom de transitoire [74, 75](voir figure 1.22).

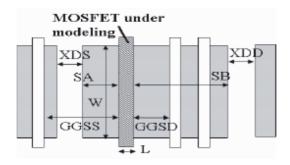

contacts, et des espaceurs. Tsuno et al. introduisent dans le modèle compact

FIGURE 1.23 – Paramètres d'instance proposés par Tsuno pour simuler les interactions du layout sur le process. [73]

BSIM les effets de la distance au STI, de la taille du STI et la distance entre la grille et le premier trait de polysilicium, en ajoutant des termes correctifs à la tension de seuil  $V_{th}$  et à la mobilité  $\mu_{eff}$ :

$$Vt = Vt_0 + f(SA, SB, XDS, XDD, L) + g(SA, SB, GGSS, GGSD, L),$$

(1.5)

$$\mu_{\text{eff}} = \mu_{\text{eff0}} \times h(\text{SA}, \text{SB}, \text{XDS}, \text{XDD}, \text{GGSS}, \text{GGSD}),$$

(1.6)

où f est une fonction du stress, g une fonction de la TED, et les autres paramètres sont décrits dans la figure 1.23.

# 1.2.4 Sources originaires du procédé

#### Dépôts

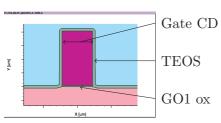

Dans le front-end du procédé, des dépots d'oxyde, de polysilicium (la grille) et de nitrure sont effectués. La technique de dépot est le dépot chimique en phase vapeur – CVD, Chemical vapor deposition – qui consiste à exposer la surface des plaquettes à une molécule contenant le matériau à déposer, appelée précurseur. Les dépots existent sous un bon nombre de variantes selon la pression dans la chambre de réaction (utilisation de plasma ou de phase vapeur). Sous l'action de l'atmosphère présente dans la chambre à réaction, le précurseur va réagir selon les équations du tableau 1.2 et ainsi déposer le matériau voulu.

Le dépot de dioxyde porte couramment le nom de son précurseur, le TEOS

| Polysilicium        | $\mathrm{SiH}_4$    | $\longrightarrow$ | $Si + 2H_2$                                                                |

|---------------------|---------------------|-------------------|----------------------------------------------------------------------------|

| Dioxyde de silicium | $SiCl_2H_2 + 2N_2O$ | $\longrightarrow$ | $SiO_2 + 2H_2$<br>$SiO_2 + 2N_2 + 2HCl$<br>$SiO_2 + résidus$               |

| Nitrure             |                     | $\longrightarrow$ | $Si_3N_4 + 12H_2$<br>$Si_3N_4 + 6HCl + 6H_2$<br>$n_3Si_3N_4 + n_4HCl$ [76] |

Table 1.2 – Réactions utilisées pour les dépots.

$t\acute{e}tra-ethyl-ortho-silicate~Si(OC_2H_5)_4$ . De même on appele HCD,  $hexa-chloro-disilane~(SiCl_3)_2$ , le dépôt de nitrure.

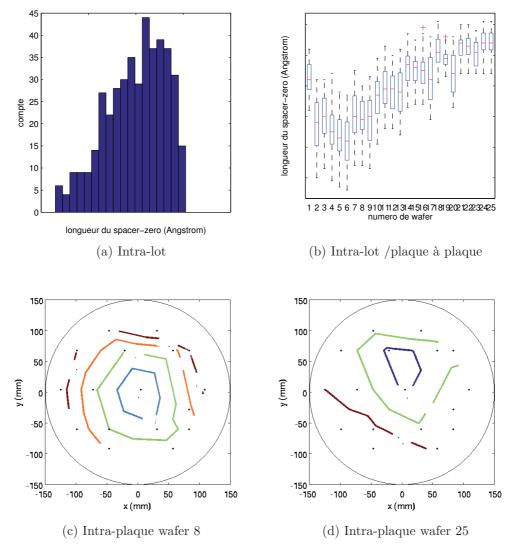

Les variations d'épaisseur de ces dépots s'observent par plaques avec un motif typiquement radial. Pour les dépots issus d'un procédé par *batch*, c'est à dire qu'on place le lot entier dans la chambre de réaction, on observe à la fois une dérive de la valeur moyenne et une dispersion de l'épaisseur déposée par plaquette d'un bout à l'autre du lot. On observera des mesures de ce type dans le chapitre 3.

FIGURE 1.24 – Simulation des taux de croissance locaux dans le réacteur en fonction du flux de gaz [77].

### Gravures

Parmi les gravures entrant en jeu dans la réalisation du transistor MOS, il y a la gravure de la tranchée d'isolation STI, la gravure du polysilicium de grille, la gravure du HCD des espaceurs et la gravure du diélectrique pré-métal pour le contact de grille, source, drain et bulk au niveau *Métal 1*.

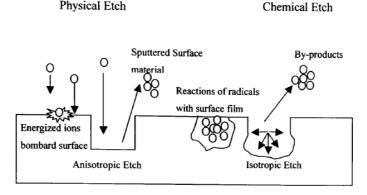

Physical Etch

Ces quatre gravures sont des gravures sèches et isotropiques, pour graver uniquement dans le plan vertical. La littérature ne rapporte pas de source de variabilité particulière associée aux gravures anisotropes.

FIGURE 1.25 – Gravure sèche et humide [78].

### **Implantations**

L'implantation des ions est en soi un procédé réputé comme ayant une bonne répétabilité. La dose est controlée en courant dans l'implanteur. C'est l'intégrale du flux d'ions pendant le temps d'implantation.

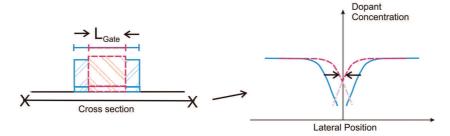

La miniaturisation des dispositifs a poussé à augmenter les niveaux de dopage. Pour régler le V<sub>th</sub>, il a été nécessaire d'ajouter des implantations de dopants pour contrer les effets de canal court. Les implants appelés poches, pockets en anglais, ou encore halo sont des zones surdopées, situées sous les ldd. Leur fonction est de ralentir l'avancée des zones de charge d'espace des source/drain vers le canal et donc la perte de contôle du canal par la grille, quand  $L_g$  diminue. Ce dopage est réalisé par des implantations ioniques inclinées par rapport à la verticale pour envoyer les dopants sous la grille. On effectue généralement quatre implants en pivotant la plaque d'un quart de tour pour doper les zones d'ombre de la grille.

Croon et al. séparent les fluctuations aléatoires de V<sub>th</sub> en fluctuation du dopage, de la charge d'interface, de l'épaisseur d'oxyde et les différencie grâce à l'observation de  $A_{Vt}$  en fonction de  $V_B$ . Le modèle correspondant avec une dépendance en V<sub>B</sub> prends en compte l'épaisseur de la couche de désertion  $W_D$  [79]. L'implant halo vient contredoper le dopage de la grille à travers les grains aléatoires de polysilicium et augmente la part de variation due à

la charge de grille. Ils montrent une réduction de  $A_{Vt}$  d'un facteur 2 sur le pMOS en réduisant l'inclinaison des *pockets* de 45° à 35°.

Le problème avec les implantations ioniques vient aussi et surtout du fait qu'il est nécessaire de réparer le cristal par traitement thermique, ce qui implique une diffusion des dopants.

#### Recuits

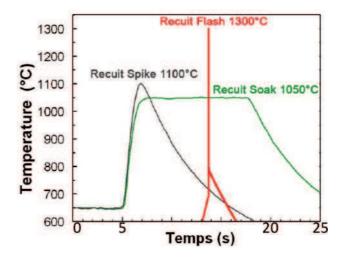

Le recuit est une opération intervenant plusieurs fois, après les implantations ioniques pendant les opérations de front-end. Sa fonction est de reformer le cristal de silicium qui a été abimé, voire complètement amorphisé durant le bombardement ionique, tout en activant les dopants, c'est à dire les intégrer au maillage cristallin. Les recuits sont faits à des températures de l'ordre de 1000 °C. On distingue les recuits soak avec profil en plateau pendant un temps de l'ordre de quelques dizaines de secondes, les recuits spike, en pic pendant quelques secondes et les recuits flash et laser dont le temps d'action est inférieur à la seconde.

FIGURE 1.26 – Profils en température des recuits spike, soak et flash [80].

Les recuits spike (et laser) montent en pic à des températures de l'ordre de 1300° et ne chauffent qu'une couche superficielle du substrat. La chaleur diffuse ensuite dans le substrat. Les wafers sont chauffés plaque par plaque par des lampes halogènes ou au tungstène. Les wafers sont en rotation sur leur support pour améliorer l'uniformité du recuit. Le recuit flash utilise des lampes à arc à l'argon qui émettent autour de 800 nm pour le pic principal.

Pendant le recuit, l'apport d'énergie sous forme de chaleur permet la diffusion des dopants. La diffusion des dopants dans le temps suit le gradient spatial de concentration (lois de Fick) :

$$J = -D_A \frac{\partial C(x,t)}{\partial x} \tag{1.7}$$

avec

$$D_A = -D_0 \exp\left(\frac{-E_a}{kT}\right)$$

(1.8)

et

$$\frac{\partial C(x,t)}{\partial x} = \frac{\partial J(x,t)}{\partial x}$$

. (1.9)

J est le courant de diffusion,  $D_A$  le coefficient de diffusion associé à l'espèce A (bore, arsenic ou phosphore) et C la concentration de A.  $D_0$  est appelé coefficient pré-exponentiel de la loi d'Arrhenius (1.8),  $E_a$  est l'énergie d'activation, k la constante de Boltzman et T la température.

La diffusion ne peut se faire que par des mécanismes d'interactions des impuretés avec les défauts. On définit différents types de placement pour décrire ces défauts :

un atome substitutionnel  $A_S$  qui se place dans le réseau cristallin, un atome interstitiel  $A_I$  se trouve entre les atomes du réseau, un auto-interstitiel I est un atome de silicium interstitiel.

Une lacune  $V^{15}$  est l'absence d'un atome à un endroit du cristal.

Ces différents défauts interagissent selon plusieurs mécanismes (lacunaire, interstitiel, Franck-Turnbull, kick-out, recombinaison interstitiel-lacune) qui résultent en la diffusion des impuretés. Ces défauts se regroupent en défauts étendus (agglomérats, défauts 311, boucles) et évoluent au cours du recuit, influençant la diffusion. On pourra se réferrer à [80] pour une description complète des mécanismes de diffusion.

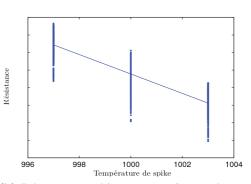

Les recuits des implants du substrat ne sont pas à proprement parler critiques. Les recuits des source/drain le sont car on veut des jonctions étroites et donc peu diffusées. La diffusion des dopants dans les recuits rapides est accélérée par les défauts en particulier au début du recuit par la diffusion accélérée et transistoire (TED-transient enhanced diffusion) qui peut conduire à des coefficients de diffusion beaucoup plus élevés qu'à l'équilibre. Pour ces raisons, le profil final de dopage est très sensible à la température de recuit.

<sup>15.</sup> Vacancy en anglais.

La non uniformité du budget thermique sur une plaque est critique. On observera ce problème au chapitre 3.

Les conditions de process peuvent tout de même être optimisées afin de réduire la sensibilité à cette source de variabilité. Difrenza et al. [26] étudient la sensibilité du coefficient de désappariement aux paramètres du procédé. Ils montrent en particulier la sensibilité du facteur de mismatch  $A_{V_t}$  à la température du recuit RTA – pour Rapid Thermal Annealing – et aux doses des implants ldd. Ils modifient leur procédé en conséquence pour garder les conditions de fabrication de grille minimisant le désappariement de 4,1 mV ·  $\mu$ m à 2 mV ·  $\mu$ m. L'amélioration de l'appariement induit, au niveau du circuit, un acroissement de la linéarité des convertisseurs numérique-analogique de l'ordre de 40 % et une amélioration de 1 bit sur la résolution des convertisseurs analogique-numérique. La marge statique au bruit des circuits SRAM est aussi augmentée de 25 %.

# 1.3 Modélisation des déviations

Modéliser les mécanismes de variabilité est essentiel à plusieurs niveaux. Les concepteurs doivent pouvoir prédire le rendement des circuits qu'ils dessinent, les modélistes doivent leur fournir des modèles permettant de dissocier les variations globales et locales et prévoyant au mieux les déviations systématiques. Les technologues ont besoin de modèles pour étudier les phénomènes mis en jeu afin d'annuler ou de minimiser leurs influences.

Les problèmatiques matériau, transistor et circuit utilisent des outils de simulation différents.

# 1.3.1 Variabilité du process

#### Simulation avancée de procédés

L'équipe de Martin Jaraiz de l'université de Valladolid a développé plusieurs outils de simulation atomistique des procédés de fabrication [81] pour étudier l'implantation, le recuit et la croissance de matériaux. Dans un simulateur atomistique, ce sont les relations entre atomes qui sont modélisées, le résultat de la simulation étant la conséquence à grande échelle de ces règles

intervenant à l'échelle atomique <sup>16</sup>.

Molecular Dynamics permet de reproduire la formation des dommages subis par le silicium et sa recristallisation. Cet outil simule tous les atomes du réseau, avec un pas de simulation constant, ayant pour inconvénient un temps de calcul important, mais les informations obtenues peuvent être pertinentes pour le développement d'autre modèles.

DADOS contrairement à Molecular Dynamics se concentre sur les évènements de diffusion selon leur probabilité d'apparition et ne simule pas le réseau entier. L'implantation utilise l'approximation de collisions entre deux atomes <sup>17</sup>. La prise en compte, au niveau atomique, des interactions des défauts et des dopants pendant le recuit permet d'étudier la dynamique de la diffusion avec une grande prédictivité. Cela donne une référence pour le développement des modèles continus de diffusion. DADOS a été acquis par Synopsys et intégré au simulateur Sprocess [82]. Les résultats de ce type d'implantations prennent intrinsèquement en compte la nature discrète des dopants et permettent l'étude des effets électriques de cette source de variabilité [83].

Hane et~al. ont développé un outil de simulation analogue avec lequel ils génèrent des dispositifs statistiquement différents pour les simuler électriquement dans un simulateur drift-diffusion dont le potentiel électrique est calculé à partir des potentiels coulombiens de chaque atome [84].

### Modélisation de type TCAD

Les simulations TCAD <sup>18</sup> sont des outils de simulation numérique permettant de simuler en premier lieu la fabrication des dispositifs, puis, à partir du résultat du procédé, de simuler son comportement électrique. Au sens usuel du terme, ce sont des simulations par éléments finis résolvant des équations continues. Par conséquent, elles ne sont pas destinées à prendre en compte la nature atomistique des matériaux. Cependant, les outils dont nous avons parlé au paragraphe précédent sont intégrés dans les suites logicielles de TCAD en tant qu'alternative à la résolution d'équations continues, dans le cas des implantations et des recuits. La nature aléatoire des dopants est ainsi utilisable dans les simulations électriques.

<sup>16.</sup> à la différence de simulations par éléments finis où les équations résolues portent sur la concentration des impuretés et au flux de diffusion.

<sup>17.</sup> BCA: Binary Collision Approximation

<sup>18.</sup> Technology Computer Aided Design

Les variations de largeur de trait de polysilicium dues aux effets de proximité peuvent être prédites à partir du masque à l'aide d'outils de simulation optique, utilisés en particulier pour mettre au point les corrections d'amélioration de la résolution [85]. La rugosité de ligne de polysilicium peut-être introduite dans les simulations de procédé, en trois dimensions, si l'utilisateur définit de son coté les profils de masque de grille à utiliser. Les profils peuvent être générés aléatoirement à partir de l'analyse spectrale de vrais profils observés sur polysilicium et dont on extrait l'amplitude moyenne et la longueur d'autocorrélation. Il est également possible de modéliser cette source par une somme de transistors dont les longueurs suivent statistiquement la rugosité de ligne [86]. Les simulateurs commerciaux sont capables de simuler des transistors présentant des irrégularités aléatoires de grille mais c'est à l'utilisateur d'introduire les géométries correspondantes.

#### 1.3.2 Variabilité du transistor

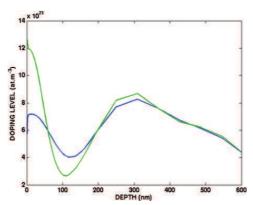

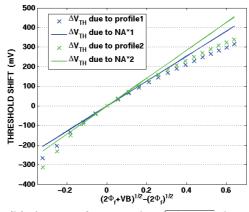

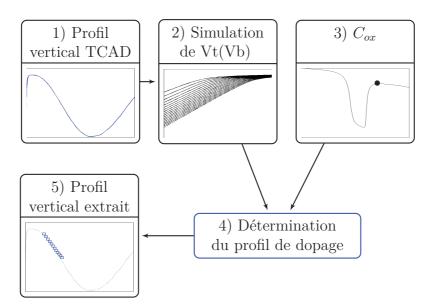

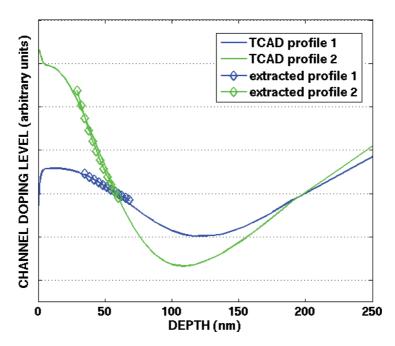

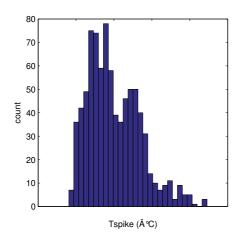

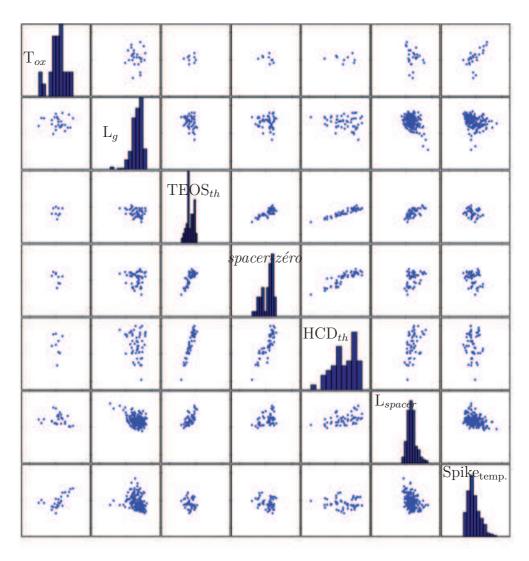

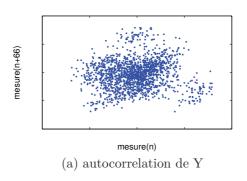

#### Simulations TCAD