Nº d'ordre : 3627

# THÈSE

présentée à

# L'UNIVERSITÉ DE BORDEAUX I

ÉCOLE DOCTORALE DE SCIENCES PHYSIQUES ET DE L'INGENIEUR

par Corinne BESTORY

POUR OBTENIR LE GRADE DE

# **DOCTEUR**

SPÉCIALITÉ : ELECTRONIQUE

Développement d'une stratégie de conception en vue de la fiabilité pour la simulation de la fiabilité et la prévision de la durée de vie des circuits intégrés dès la phase de conception

Soutenue le : 17 Septembre 2008

#### Après avis des rapporteurs: Mme Lorena ANGHEL ..... Maître de conférences - INPG/ENSERG, TIMA ... Rapporteur Luc HEBRARD ..... Professeur - Université Louis Pasteur, InESS ...... Rapporteur Devant la commission d'examen composée de : Mme Lorena ANGHEL ..... Maître de conférences - INPG/ENSERG, TIMA ... Examinateur Μ. Yves DANTO ..... Professeur émérite - Université Bordeaux 1, IMS ... Rapporteur Pascal FOUILLAT .... Μ. Professeur - Université Bordeaux 1, IMS ...... Président du Jury Μ. Didier GOGUENHEIM Professeur associé - ISEN, IM2NP ..... Examinateur Μ. Luc HEBRARD ...... Professeur - Université Louis Pasteur, InESS ...... Examinateur Professeur - Université Bordeaux 1, IMS ...... Μ. Hervé LEVI ..... Examinateur Μ. François MARC ...... Maître de conférences - Université Bordeaux 1, IMS Examinateur Μ. Jean-Luc MURARO ... Docteur-ingénieur - Thalès Alénia Space ..... Examinateur

| A mon papa parti trop tôt                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A ma maman chérie « doudou de mon cœur »                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                       |

| « Science sans conscience n'est que ruine de l'âme »                                                                                                                                                                                                  |

| François Rabelais, $XV^{i\grave{e}me}$ siècle                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                       |

| « Quiconque prétend s'ériger en juge de la vérité et du savoir s'expose à périr sous les éclats de rire des Dieux, puisque nous ignorons comment sont réellement les choses et que nous n'en connaissons que la représentation que nous en faisons. » |

| Albert Einstein, 1879-1955                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                       |

# Remerciements

Le travail synthétisé dans ce mémoire a été réalisé au sein du groupe fiabilité du laboratoire IMS (Intégration du matériau au système, anciennement IXL). Ce laboratoire offre un environnement de travail privilégié tant par la qualité des conditions techniques de travail que par la convivialité et la compétence des personnes que l'on y rencontre. Je remercie Messieurs André TOUBOUL et Pascal FOUILLAT, ancien et nouveau directeur du laboratoire IMS, de m'avoir offert l'opportunité d'intégrer leur laboratoire.

Je remercie vivement Madame Lorena ANGHEL, Maître de conférences à l'INP Grenoble - EN-SERG, et Monsieur Luc HEBRARD, Professeur de l'Université Louis Pasteur de Strasbourg, pour l'honneur qu'ils m'ont fait et pour l'intérêt qu'ils ont porté à mes travaux en acceptant d'être les rapporteurs de ce mémoire de thèse. Leurs remarques constructives et leurs encouragements me seront d'une aide précieuse.

Je remercie vivement messieurs Didier GOGUENHEIM, professeur associé à l'ISEN, et Jean-luc MURARO, Ingénieur à Thalès Alénia Space, pour l'intérêt qu'ils ont porté à ces travaux en acceptant de faire partie du jury de thèse.

Je tiens également à remercier Messieurs Hervé LEVI, mon directeur de thèse, et François MARC, mon encadrant de thèse, de m'avoir accepté pour cette aventure. Les trois années passées sous leur tutelle sont parmi les plus enrichissantes de ma vie, et les conseils et reproches qu'ils ont pu m'adresser ont toujours eu pour objectif de me faire progresser. Pour tout cela et pour leur soutien, qu'ils soient assurés de ma reconnaissance.

J'éprouve une certaine émotion à remercier Monsieur Yves DANTO, Professeur émérite de l'Université Bordeaux 1, de son soutien, ses précieux conseils et les nombreuses conversations très enrichissantes que nous avons eues ensemble.

Je souhaite aussi remercier l'ensemble du personnel administratif et technique des différents services du laboratoire IMS pour les nombreuses aides qu'ils ont pu me rendre durant mon quotidien de doctorante.

Merci aussi à tous les membres du laboratoire, qu'ils soient doctorants ou permanents.

Ces travaux n'auraient jamais pu aboutir sans le soutien moral de mes amis : Nathalie, Mickaël, Rachèle, Hélène, Rodrigue, Manuel et Coralie. Ils m'ont apporté sérénité et réconfort dans les moments de doute, ainsi que de grandes joies. Mon efficacité de travail aurait été bien amoindrie sans leur amitié sincère et profonde. Qu'ils en soient remerciés sur sept générations au moins.

Je remercie également ma tante Jacqueline et Coralie pour leur talent de correctrices. Leurs contributions à ce manuscrit sont aussi des briques précieuses dans sa construction.

Finalement, mes pensées, mon amour et mon respect les plus sincères vont à ma famille proche, ma mère et mes frères, pour m'avoir toujours soutenue, quoique je fasse, et pour m'avoir toujours aimée, quoique je dise. J'adresse une pensée très émue à mes parents, particulièrement à mon père, parti un peu trop tôt, pour m'avoir appris à être curieuse, respectueuse et responsable, pour m'avoir soutenue sans faillir tout au long de ces travaux, mais aussi, bien avant et pour m'avoir donné les fondements de cette réussite. Mon principal héritage est mon caractère entier. Je sais qu'ils sont fiers de moi, mais peut-être ne savent-ils pas que je suis encore plus fière d'être leur fille (unique en plus!). Papa, maman, merci pour tout... A vous, je dédie ce manuscrit.

# Table des matières

| In | trod                                                                           | uction  | générale                                                                           | 1  |

|----|--------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------|----|

| 1  | Du                                                                             | test à  | la simulation de la fiabilité : état de l'art                                      | 5  |

|    | 1                                                                              | La fia  | bilité des semi-conducteurs                                                        | 6  |

|    |                                                                                | 1.1     | Notions et définitions de base                                                     | 6  |

|    |                                                                                | 1.2     | La fiabilité des semiconducteurs                                                   | 8  |

|    |                                                                                | 1.3     | Estimation et analyse de la fiabilité                                              | 10 |

|    |                                                                                | 1.4     | Impact de la maturité d'une technologie sur la fiabilité intrinsèque d'une famille |    |

|    |                                                                                |         | de composants                                                                      | 13 |

|    | 2                                                                              | Le tra  | uitement de la fiabilité                                                           | 14 |

|    |                                                                                | 2.1     | Les essais de fiabilité                                                            | 14 |

|    |                                                                                | 2.2     | Notion de « critère de défaillance »                                               | 15 |

|    |                                                                                | 2.3     | Les mécanismes de défaillances physiques                                           | 16 |

|    |                                                                                | 2.4     | La physique des défaillances                                                       | 19 |

|    |                                                                                | 2.5     | Conclusion                                                                         | 19 |

|    | 3 La conception en vue de la fiabilité : de la modélisation SPICE à la modélis |         |                                                                                    |    |

|    |                                                                                | compo   | ortementale                                                                        | 20 |

|    |                                                                                | 3.1     | Environnement de simulation de la fiabilité                                        | 20 |

|    |                                                                                | 3.2     | Simulation du vieillissement des circuits intégrés                                 | 21 |

|    |                                                                                | 3.3     | De la simulation de type SPICE à la simulation comportementale : limitations       |    |

|    |                                                                                |         | des simulateurs SPICE                                                              | 22 |

|    |                                                                                | 3.4     | Conclusion                                                                         | 23 |

|    | 4                                                                              | Concl   | usion                                                                              | 24 |

| 2  | Mo                                                                             | délisat | ion comportementale de circuits analogiques et mixtes                              | 27 |

|    | 1                                                                              | Introd  | luction à la modélisation de circuits analogiques et mixtes                        | 28 |

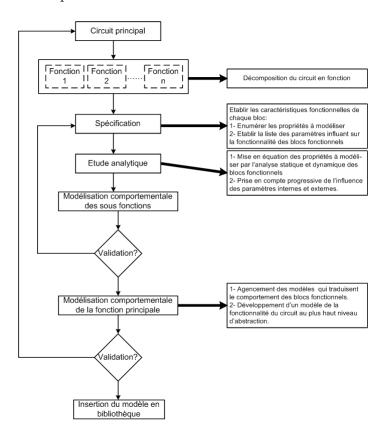

|    |                                                                                | 1.1     | Méthodologie Top-Down & Bottom-Up                                                  | 28 |

|    |                                                                                | 1.2     | Les techniques de modélisation des circuits analogiques et mixtes                  | 30 |

|    |                                                                                | 1.3     | Introduction à la modélisation comportementale                                     | 32 |

|                     |      | 1.4    | Conclusion                                                                           | 41 |

|---------------------|------|--------|--------------------------------------------------------------------------------------|----|

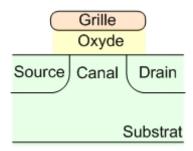

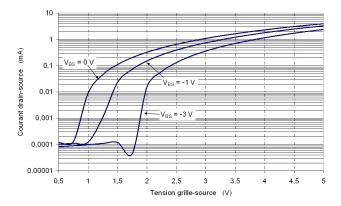

| 2 Le transistor MOS |      |        | ansistor MOS                                                                         | 43 |

|                     |      | 2.1    | Historique                                                                           | 43 |

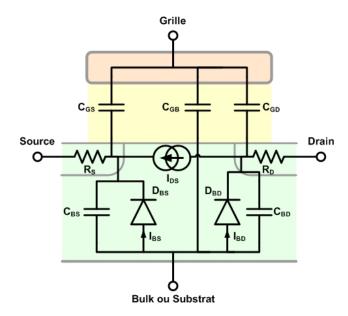

|                     |      | 2.2    | Modèle comportemental simplifié du transistor MOS pour la conception de              |    |

|                     |      |        | fonctions analogiques                                                                | 45 |

|                     |      | 2.3    | Implémentation VHDL-AMS                                                              | 47 |

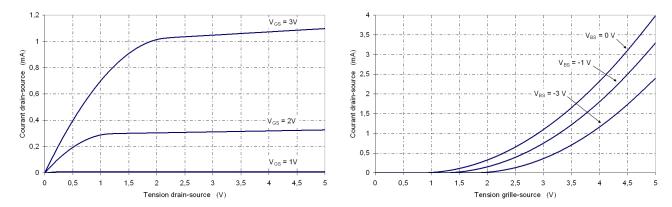

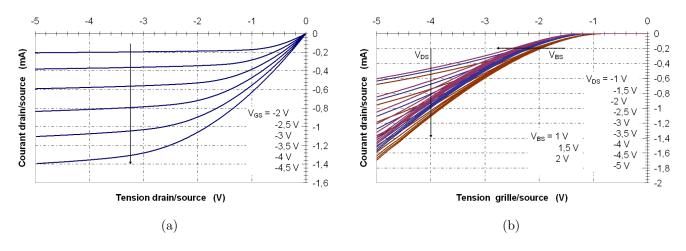

|                     |      | 2.4    | Simulation et représentation graphique                                               | 47 |

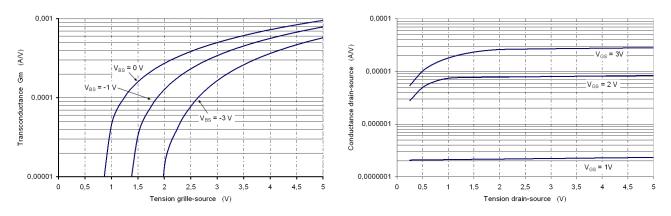

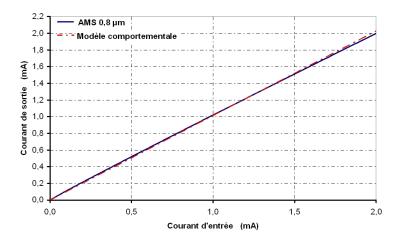

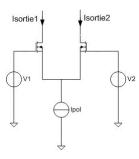

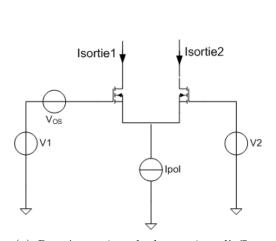

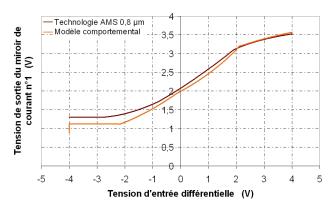

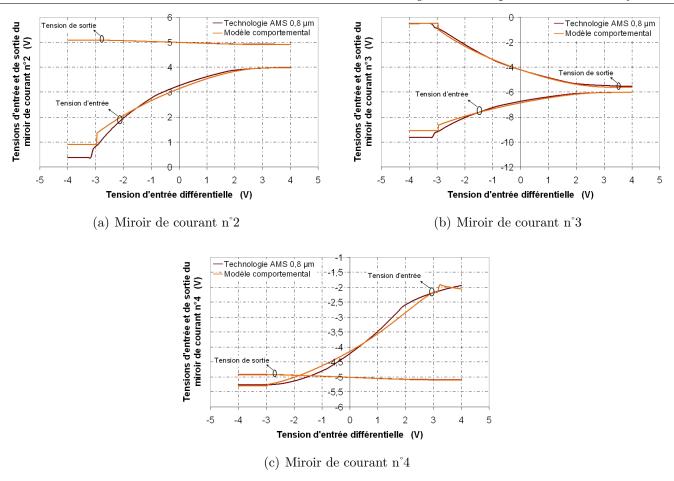

|                     | 3    | Le mi  | roir de courant simple                                                               | 50 |

|                     |      | 3.1    | Le modèle comportemental de niveau 1                                                 | 50 |

|                     |      | 3.2    | Implémentation VHDL-AMS                                                              | 51 |

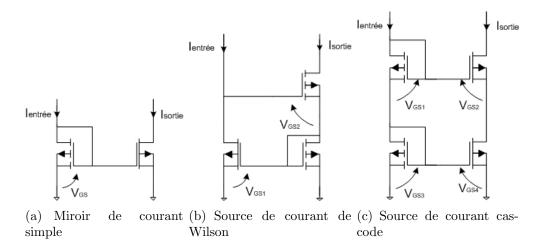

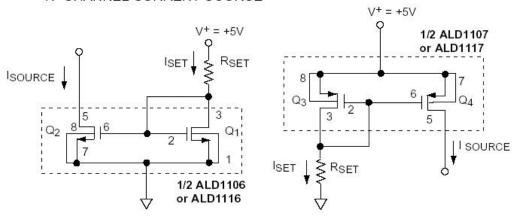

|                     |      | 3.3    | Simulation et représentation graphique                                               | 52 |

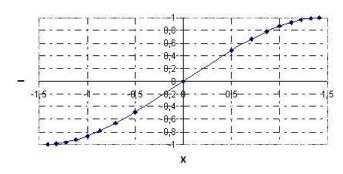

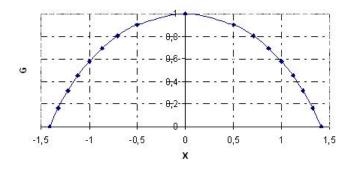

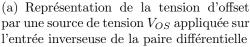

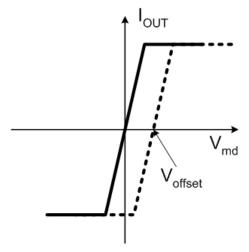

|                     | 4    | La pa  | ire différentielle                                                                   | 54 |

|                     |      | 4.1    | Le modèle comportemental                                                             | 54 |

|                     |      | 4.2    | Implémentation VHDL-AMS                                                              | 58 |

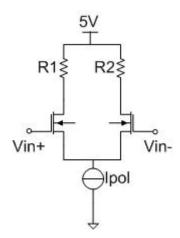

|                     |      | 4.3    | Simulation et représentation graphique                                               | 58 |

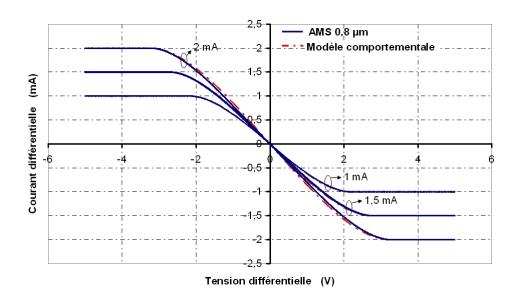

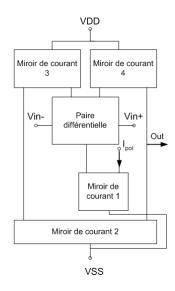

|                     | 5    | L'amı  | plificateur opérationnel à transconductance                                          | 61 |

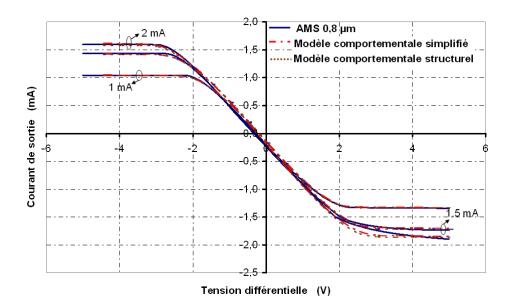

|                     |      | 5.1    | Le modèle comportemental « structurel »                                              | 61 |

|                     |      | 5.2    | Le modèle comportemental simplifié                                                   | 62 |

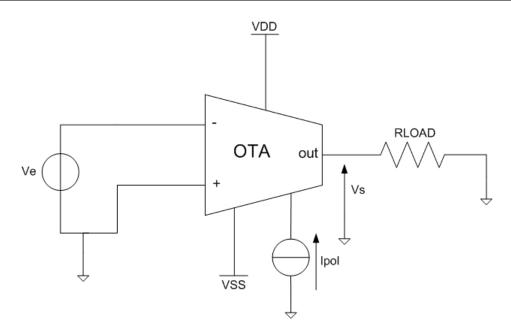

|                     |      | 5.3    | Simulation et représentation graphique des modèles                                   | 64 |

|                     | 6    | Concl  | lusion                                                                               | 66 |

|                     |      |        |                                                                                      |    |

| 3                   |      |        | n du vieillissement électrique des circuits intégrés : développement d'une           |    |

|                     | stra |        | de conception en vue de la fiabilité                                                 | 67 |

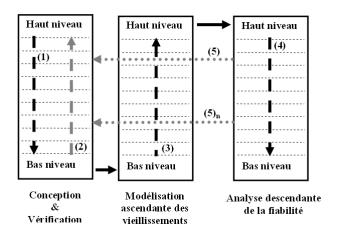

|                     | 1    | Strate | égie de conception en vue de la fiabilité                                            | 68 |

|                     |      | 1.1    | Concept général                                                                      |    |

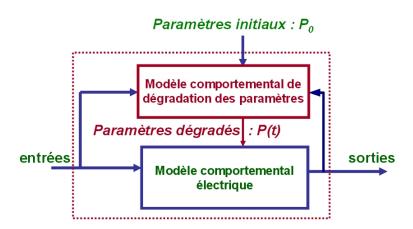

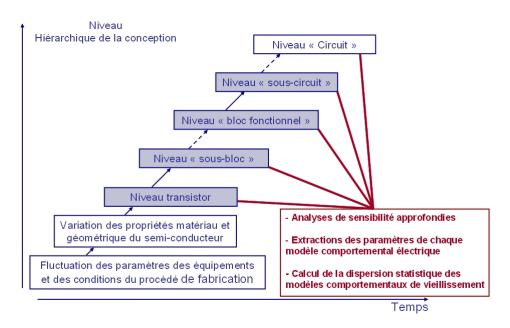

|                     |      | 1.2    | Modélisation ascendante du vieillissement des circuits intégrés                      | 68 |

|                     |      | 1.3    | Analyse descendante de la fiabilité des circuits intégrés                            | 71 |

|                     |      | 1.4    | Conclusion                                                                           | 74 |

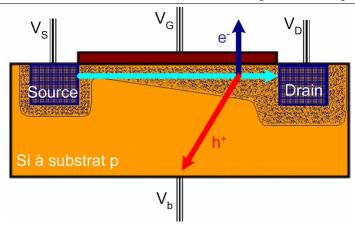

|                     | 2    | Modé   | lisation comportementale du vieillissement électrique des transistors MOS induit     |    |

|                     |      | par in | njection de porteurs chauds (HCI)                                                    | 75 |

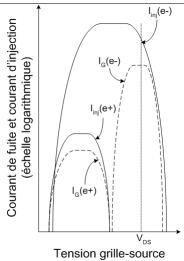

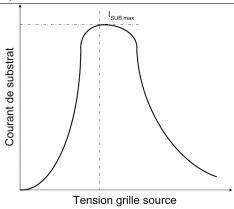

|                     |      | 2.1    | Rappel sur l'injection de porteurs chauds                                            | 75 |

|                     |      | 2.2    | Modélisation de la durée de vie                                                      | 79 |

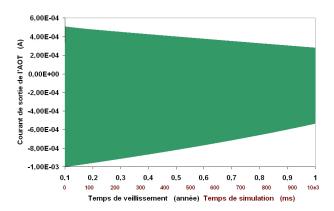

|                     |      | 2.3    | Simulations comportementales du vieillissement électrique du transistor ${ m MOS}$ . | 83 |

|                     |      | 2.4    | Conclusion                                                                           | 88 |

|                     | 3    | Modé   | lisation ascendante des dégradations d'un AOT induites par HCI                       | 90 |

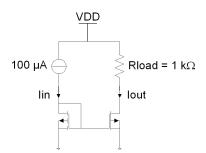

|                     |      | 3.1    | Le miroir de courant simple                                                          | 90 |

|                     |      | 3.2    | La paire différentielle                                                              | 92 |

|                     |      | 5.4    | La paire differentiere                                                               | 34 |

# TABLE DES MATIÈRES

|   | 4    | Anal    | yse descendante de la fiabilité de l'AOT                                      | 100          |

|---|------|---------|-------------------------------------------------------------------------------|--------------|

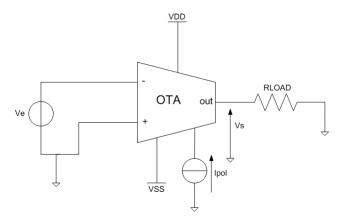

|   |      | 4.1     | Transconducteur à un AOT                                                      | 100          |

|   |      | 4.2     | Amplification à un AOT                                                        | 104          |

|   |      | 4.3     | Discussion                                                                    | 105          |

|   | 5    | Conc    | elusion                                                                       | 109          |

| 4 | Pré  | vision  | n de la durée de vie d'un lot de composants : introduction à l'analys         | $\mathbf{e}$ |

|   | stat | tistiqu | ue lors de la phase de simulation de la fiabilité                             | 111          |

|   | 1    | Notic   | ons et outils statistiques pour l'analyse de la fiabilité                     | 113          |

|   |      | 1.1     | Fonctions de distribution                                                     | 113          |

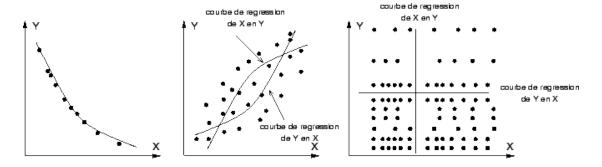

|   |      | 1.2     | Diagramme de dispersion ou de corrélation                                     | 113          |

|   |      | 1.3     | Coefficients de covariance et de corrélation                                  | 114          |

|   |      | 1.4     | Formules de transmission des moments                                          | 114          |

|   | 2    | Méth    | nodologie de modélisation statistique d'une famille de composants : du niveau |              |

|   |      | trans   | sistor au niveau circuit                                                      | 116          |

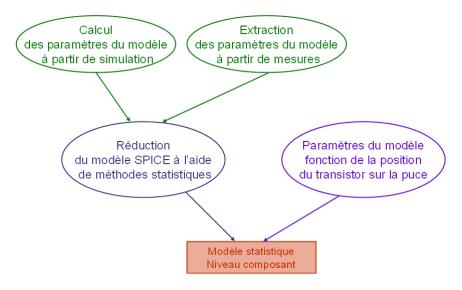

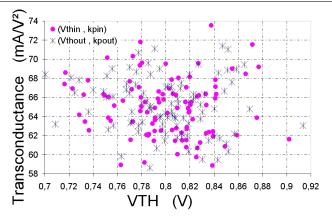

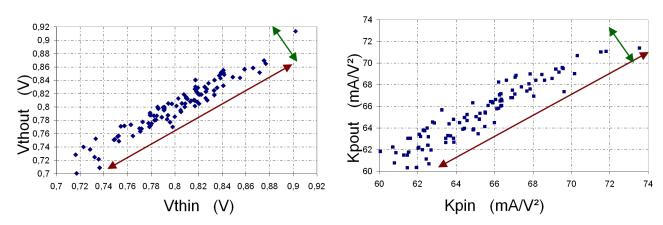

|   |      | 2.1     | Introduction                                                                  | 116          |

|   |      | 2.2     | Les erreurs paramétriques liées au procédé de fabrication                     | 117          |

|   |      | 2.3     | Modélisation statistique au niveau transistor                                 | 118          |

|   |      | 2.4     | Modélisation statistique au niveau circuit                                    | 118          |

|   |      | 2.5     | Détermination des propriétés statistiques des performances et des instants de |              |

|   |      |         | défaillance d'un lot de CIs                                                   | 119          |

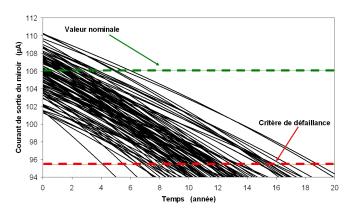

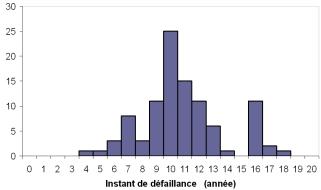

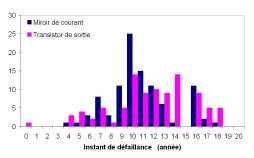

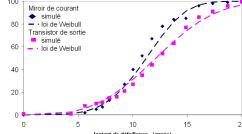

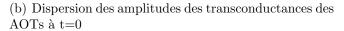

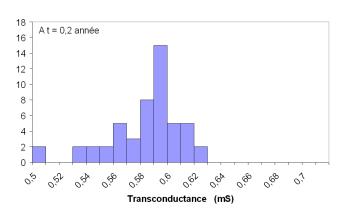

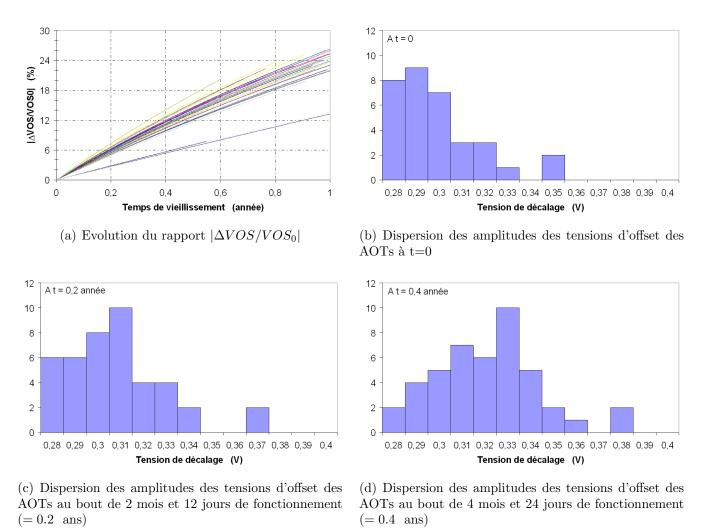

|   | 3    | Modé    | élisation statistique d'une famille d'AOTs                                    | 121          |

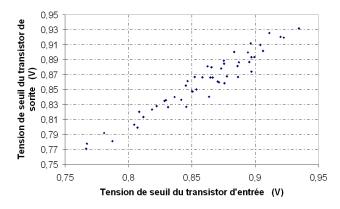

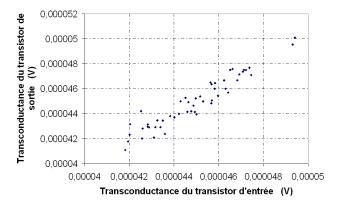

|   |      | 3.1     | Modèle statistique du transistor MOS                                          | 121          |

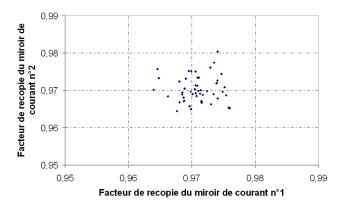

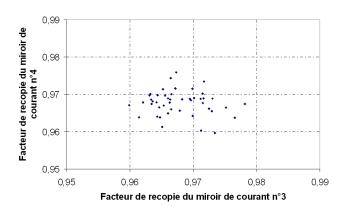

|   |      | 3.2     | Modèle statistique du miroir de courant simple                                | 122          |

|   |      | 3.3     | Modèle statistique de la paire différentielle                                 | 123          |

|   |      | 3.4     | Modèle statistique de l'AOT                                                   | 123          |

|   |      | 3.5     | Conclusion                                                                    | 125          |

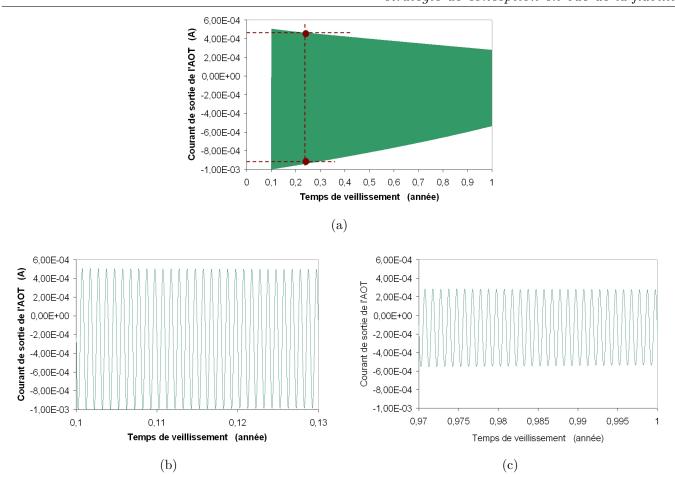

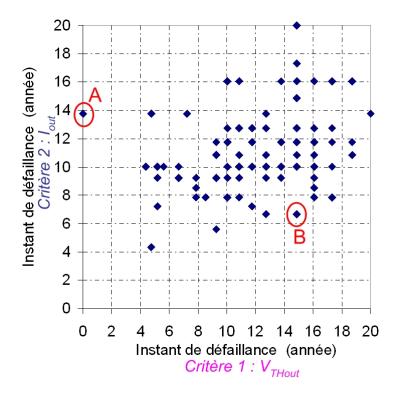

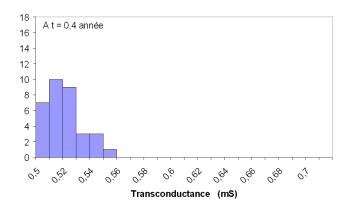

|   | 4    | Influe  | ence du critère de défaillance sur la dispersion des instants de défaillance  | 126          |

|   |      | 4.1     | Le circuit                                                                    | 126          |

|   |      | 4.2     | Le profil de mission                                                          | 126          |

|   |      | 4.3     | Les critères de défaillance                                                   | 126          |

|   |      | 4.4     | Détermination de la dispersion des instants de défaillance                    | 127          |

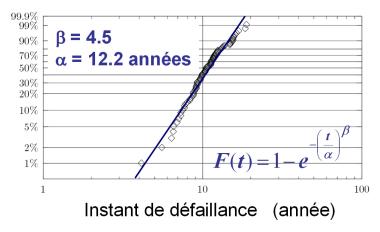

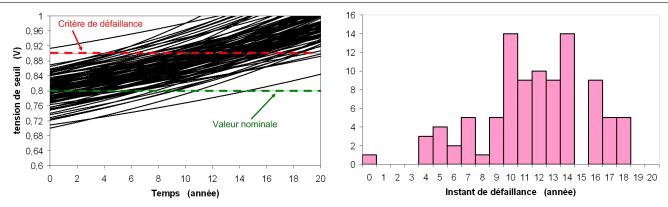

|   | 5    | Détei   | rmination de la durée de vie d'un circuit intégré                             | 133          |

|   |      | 5.1     | Le circuit                                                                    | 133          |

|   |      | 5.2     | Le critère de défaillance                                                     | 133          |

|   |      | 5.3     | Dispersion des instants de défaillance de l'AOT                               | 133          |

|   |      | 5.4     | Evolution de la robustesse de l'AOT $\dots$                                   | 133          |

|   |      | 5.5     | Conclusion                                                                    | 137          |

|   |      |         |                                                                               |              |

|                                                                 | 6                   | Concl                                                     | usion                                                                        | . 138 |

|-----------------------------------------------------------------|---------------------|-----------------------------------------------------------|------------------------------------------------------------------------------|-------|

| 5                                                               | Pré                 | vision                                                    | de la tenue aux radiations d'un circuit                                      | 139   |

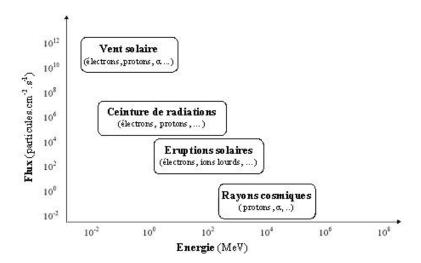

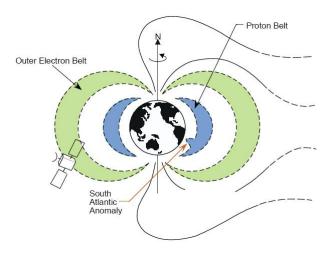

|                                                                 | 1                   | ironnement radiatif spatial                               | . 140                                                                        |       |

|                                                                 |                     | 1.1                                                       | Composantes de l'environnement spatial                                       | . 140 |

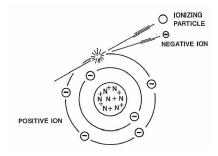

|                                                                 |                     | 1.2                                                       | Les mécanismes liés aux radiations                                           | . 142 |

|                                                                 |                     | 1.3                                                       | Synthèse                                                                     | . 143 |

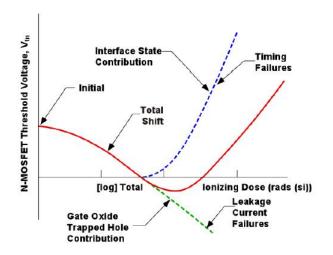

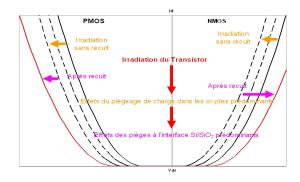

|                                                                 | 2                   | Micro                                                     | électronique et dose ionisante cumulée                                       | . 145 |

|                                                                 |                     | 2.1                                                       | Notions et définitions de base                                               | . 145 |

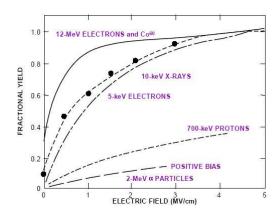

|                                                                 |                     | 2.2                                                       | Mécanismes mis en jeu                                                        | . 147 |

|                                                                 |                     | 2.3                                                       | Modélisation de l'effet de dose ionisante cumulée                            | . 149 |

|                                                                 |                     | 2.4                                                       | L'effet de dose ionisante cumulée dans les composants                        | . 150 |

|                                                                 |                     | 2.5                                                       | Conclusion                                                                   | . 152 |

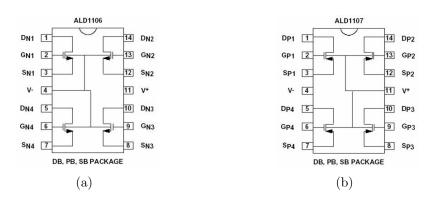

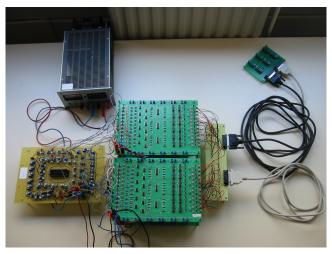

|                                                                 | 3 Plan d'expérience |                                                           | . 153                                                                        |       |

|                                                                 |                     | 3.1                                                       | Les structures à irradier                                                    | . 153 |

|                                                                 |                     | 3.2                                                       | Le protocole expérimental                                                    | . 156 |

|                                                                 |                     | 3.3                                                       | Le banc de vieillissement                                                    | . 157 |

|                                                                 |                     | 3.4                                                       | Le profil d'expérience                                                       | . 158 |

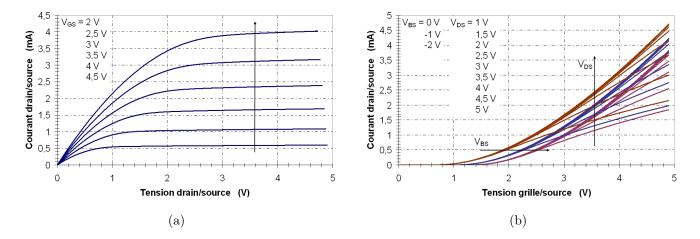

| 4 Modélisation du vieillissement électrique des transistors MOS |                     | lisation du vieillissement électrique des transistors MOS | . 159                                                                        |       |

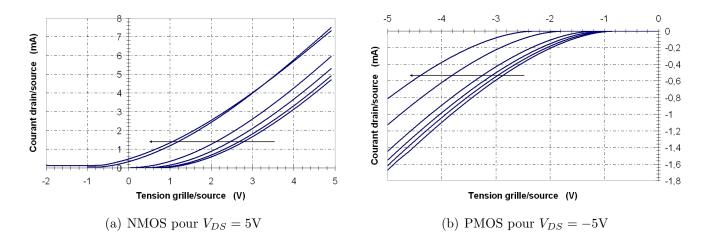

|                                                                 |                     | 4.1                                                       | Résultats expérimentaux                                                      | . 159 |

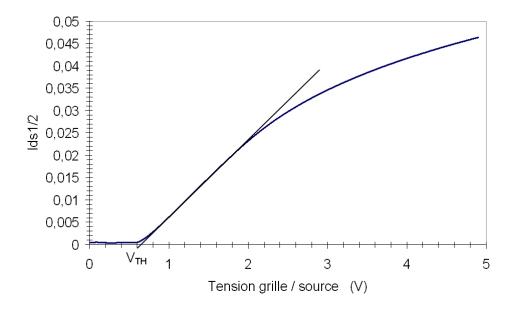

|                                                                 |                     | 4.2                                                       | Modèle électrique du transistor MOS                                          | . 159 |

|                                                                 |                     | 4.3                                                       | Extraction des paramètres du modèle et détermination des lois de dégradation | 161   |

|                                                                 |                     | 4.4                                                       | Construction du modèle comportemental                                        | . 163 |

|                                                                 |                     | 4.5                                                       | Validation du modèle                                                         | . 166 |

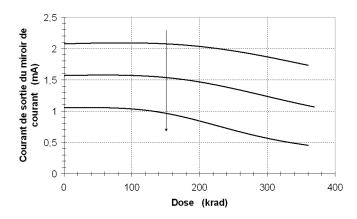

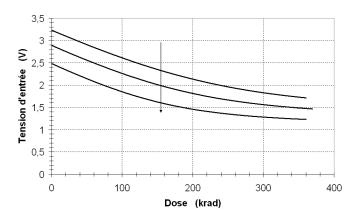

|                                                                 |                     | 4.6                                                       | Simulation du vieillissement du miroir de courant simple de type N $$        | . 166 |

|                                                                 |                     | 4.7                                                       | Conclusion                                                                   | . 167 |

|                                                                 | 5                   | Concl                                                     | usion                                                                        | . 169 |

| C                                                               | onclu               | ısion g                                                   | générale                                                                     | 169   |

| $\mathbf{A}$                                                    | Puk                 | olicatio                                                  | ons                                                                          | 181   |

# Introduction générale

De la médecine aux commodités de la vie actuelle, en passant par l'automobile, le spatial et l'aéronautique, l'électronique s'intègre partout. L'évolution des circuits intégrés (CIs) et des systèmes électroniques sur puce (SoC, systems on chips) a été rendue possible par le développement de nouveaux procédés de fabrication et un effort de miniaturisation des composants élémentaires réduisant, depuis 1960, leur taille d'un facteur dix mille. Dans le même temps, l'évolution de la fiabilité des CIs et des SoC vers de faibles taux de défaillance ( $\approx 1$  FIT selon le domaine d'application), rend les analyses statistiques via les essais accélérés de plus en plus coûteuses. Ce constat pousse les experts de la micro-électronique à anticiper le traitement de la fiabilité et à intégrer cette dernière dès la phase de conception des CIs et SoC. On parle alors de conception en vue de la fiabilité (DFR, Design for reliability).

Les stratégies DFR ont pour but d'estimer l'influence des phénomènes d'usure (par exemple : les porteurs chauds, les effets de dose, l'électromigration ...) des composants élémentaires d'un CI sur les dégradations de ses performances électriques et sa fiabilité. Cette estimation ne peut se faire qu'à l'aide de simulation de vieillissement des composants élémentaires. Malheureusement, la plupart des outils de simulation de vieillissement développés jusqu'à maintenant sont basés sur l'utilisation de deux simulateurs jumelés et ne réalisent des simulations qu'au niveau transistor, limitant ainsi leur utilisation qu'à des fonctions électroniques simples composées de quelques dizaines de transistors. Cet aspect négatif de ces stratégies DFR ne favorise pas la communication entre fiabilistes et concepteurs puisque les CIs, que ces derniers conçoivent, ont des fonctionnalités et des architectures de plus en plus complexes.

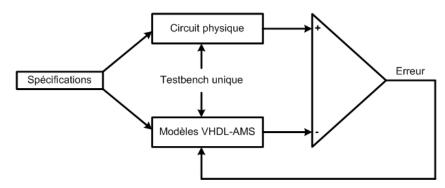

L'objectif des travaux menés au sein du laboratoire IMS par l'équipe « Fiabilité des circuits électroniques (Ficel) », dirigée par François Marc, est de développer et de mettre en œuvre des méthodologies de simulation de fiabilité fondées sur l'utilisation d'un unique simulateur. L'intérêt de la méthodologie, développée au cours de la thèse de Benoît Mongellaz, est de pouvoir simuler des circuits beaucoup plus complexes à l'aide de logiciels connus et reconnus par la communauté des concepteurs. Ces méthodes visent à construire un modèle comportemental compact d'un circuit, permettant de simuler son vieillissement [58][46] [55] [57]. Cette construction est fondée sur une analyse ascendante des relations entre les signaux d'entrées, les dégradations de chaque composant élémentaire et l'effet de ces dégradations sur le comportement du circuit. A chaque niveau de l'analyse ascendante, une simplification rigoureuse du modèle permet de ne prendre en compte que les effets significatifs des dégradations sur le comportement du circuit. L'intérêt de cette approche a été démontré. Cependant, ces méthodes doivent être consolidées et plusieurs développements restent à effectuer pour autoriser une mise en œuvre opérationnelle. Ces travaux de thèse s'inscrivent alors dans la suite des projets déjà menés.

## TABLE DES MATIÈRES

Le chapitre 1 présentera, tout d'abord, l'ensemble des définitions, les notions mathématiques et les moyens mis en œuvre pour l'analyse de la fiabilité. Nous aborderons ensuite l'environnement des outils de simulation de vieillissement existants ainsi que leurs principaux avantages et inconvénients.

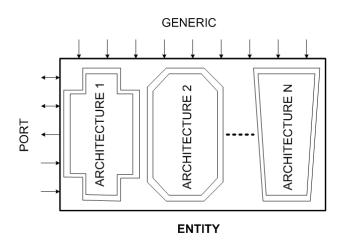

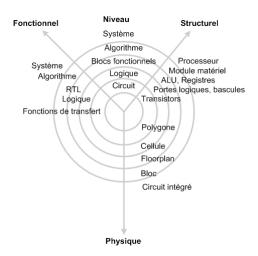

L'approche de simulation de la fiabilité, développée par l'équipe Ficel, nécessite la mise en place d'une première étape de modélisation électrique dont l'objectif principal est la définition de modèles comportementaux d'un circuit à différents niveaux hiérarchiques. Le chapitre 2 présentera, dans un premier temps, les différents types de modélisation d'un circuit et les langages qui leur sont associés. Dans un deuxième temps, la méthodologie, utilisée pour construire l'ensemble des modèles comportementaux électriques d'un amplificateur opérationnel à transconductance (AOT), développés pour les besoins de l'étude, sera présentée.

A partir des modèles comportementaux électriques, un modèle comportemental dit « dégradable », prenant en compte l'usure des composants élémentaires, peut être développé. Ce développement s'appuie sur une méthodologie de modélisation ascendante du vieillissement électrique de l'AOT. La première partie du chapitre 3 détaillera alors cette méthodologie ainsi que notre stratégie d'analyse de fiabilité, via des simulations de vieillissement électrique, développées et mises en œuvre durant ces travaux. La deuxième partie présentera une mise en œuvre opérationnelle de ces dernières afin de prédire le comportement de l'AOT vis-à-vis d'un mécanisme de dégradation : les porteurs chauds.

Le chapitre 4 présentera une première ébauche à l'introduction à l'analyse statistique durant la phase de simulation de vieillissement s'appuyant sur notre stratégie, dont l'objectif est la prévision des durées de vie d'un lot de CIs, par la prise en compte des dispersions technologiques liées au procédé de fabrication utilisé.

La validité des résultats de simulation de vieillissement dépend fortement de la validité des modèles de dégradation utilisés. Ces modèles doivent donc être construits sur des bases expérimentales. Plusieurs campagnes d'expériences ont été élaborées et mises en place afin de prédire la tenue aux radiations d'un AOT. La première partie du chapitre 5 présentera l'ensemble des notions et définitions nécessaires à l'étude des effets de dose ionisante sur la fonctionnalité des transistors MOS. L'ensemble des plans d'expériences élaborées, afin de permettre la construction de modèles comportementaux dégradables, seront définis dans la deuxième partie de ce chapitre. La troisième partie sera consacrée à la construction des modèles comportementaux de vieillissement, et la dernière, à la prévision de la tenue aux radiations du miroir de courant.

# Chapitre 1

# Du test à la simulation de la fiabilité : état de l'art

La fiabilité est la probabilité d'une entité à accomplir une fonction requise pendant un intervalle de temps donné, dans des conditions données. L'entité peut être un composant, un système, un réseau ou même un logiciel. La fonction requise, nécessaire pour la fourniture d'un service donné, doit être spécifiée dans un cahier des charges définissant les tolérances acceptables. Les conditions d'emploi sont liées à l'environnement climatique, mécanique, chimique et/ou électrique.

L'analyse de la fiabilité passe par la compréhension des modes de défaillance des CIs et la modélisation des mécanismes de dégradation qui en découlent. Pour atteindre les objectifs d'assurance fiabilité des dispositifs conçus, les outils et les méthodologies mis en œuvre ces dernières décennies sont nombreux.

Ce chapitre constitue un état de l'art des approches fiabilistes développées et des moyens utilisés. Ce chapitre se décompose en trois parties :

- la première partie rappelle l'ensemble des notions et des définitions de base nécessaires à la compréhension et à l'analyse de la fiabilité;

- la seconde partie présente les moyens mis en œuvre lors de l'évaluation de la fiabilité de circuits intégrés;

- la troisième partie, quant à elle, définit la notion de « conception en vue de la fiabilité »;

# 1 La fiabilité des semi-conducteurs

#### 1.1 Notions et définitions de base

Dans ce paragraphe, nous allons définir les principales notions et fonctions utilisées en fiabilité.

#### 1.1.1 La défaillance

Une défaillance est la cessation de l'aptitude d'une entité à accomplir une fonction requise. Deux types de défaillances sont définis :

- défaillance par dérive ou dégradation : défaillance partielle et progressive (par exemple : sous l'effet de rayonnements ionisants, les seuils de conduction des transistors MOS varient au cours du temps jusqu'à induire un mauvais fonctionnement des circuits). Une mesure de paramètre peut permettre de prévoir la défaillance selon le critère retenu.

- **défaillance catalectique :** défaillance soudaine et complète (par exemple : rupture de pistes, rupture de métallisation...).

#### 1.1.2 La fiabilité R(t)

Cette fonction représente la probabilité de fonctionnement sans défaillance pendant un temps t d'une famille de composants. Elle s'exprime de la manière suivante :

$$R(t) = \frac{Nombre \ de \ composants \ opérationnels \ \grave{a} \ l'instant \ t}{Nombre \ total \ de \ composants \ observés} \tag{1.1}$$

## 1.1.3 La fonction de distribution des défaillances F(t)

Cette fonction est la probabilité de non fonctionnement pendant un temps t d'une famille de composants. Elle représente la proportion de composants en panne à un instant t donné et s'exprime de la manière suivante :

$$F(t) = \frac{Nombre\ de\ composants\ d\'efaillants\ \grave{a}\ l'instant\ t}{Nombre\ total\ de\ composants\ observ\'es} \tag{1.2}$$

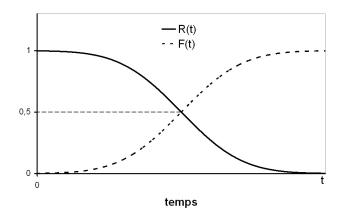

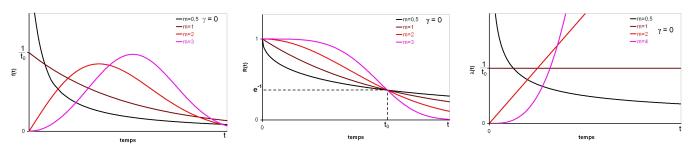

R(t) et F(t) sont respectivement strictement décroissante et strictement croissante (Cf. Fig. 1.1) pour des systèmes non réparables. De par leurs expressions, ces deux fonctions sont complémentaires :

$$R(t) + F(t) = 1 \tag{1.3}$$

Figure 1.1 – Exemple d'évolution de la fonction de fiabilité R(t) et de la fonction de distribution des défaillances F(t).

#### 1.1.4 La fonction de densité de défaillance f(t)

La fonction de densité de défaillance caractérise la vitesse à laquelle les défaillances surviennent par unité de temps. Elle s'exprime de la manière suivante :

$$f(t) = \frac{dF(t)}{dt} = -\frac{dR(t)}{dt} \tag{1.4}$$

R(t) et F(t) peuvent donc s'exprimer en fonction de f(t):

$$R(t) = \int_{t}^{\infty} f(t')dt'$$

(1.5)

$$F(t) = \int_0^t f(t')dt' \tag{1.6}$$

#### 1.1.5 Le taux de défaillance $\lambda(t)$

Le taux de défaillance à l'instant t d'un équipement est défini par l'équation 1.7.

$$\lambda(t) = \frac{f(t)}{1 - F(t)} = \frac{f(t)}{R(t)} = -\frac{d|\log R(t)|}{dt}$$

(1.7)

La fonction fiabilité peut donc s'exprimer en fonction de  $\lambda(t)$  :

$$R(t) = exp\left[-\int_0^t \lambda(t')dt'\right]$$

(1.8)

La fonction du taux de défaillance est aussi appelée taux de défaillance instantanée et est fréquemment utilisée pour évaluer la fiabilité des semi-conducteurs.

Le terme taux de défaillance instantanée est théoriquement précis. Toutefois, il est très difficile de calculer le taux de défaillance sur une courte période de temps ; une période de 1000 heures, d'un mois ou d'un an est donc souvent utilisée comme unité de temps. Cette fonction s'exprime souvent en FIT (Failure In Time) ; 1 FIT correspond à  $10^{-9}$  défaillances par heure de fonctionnement : parmi un millier de composants utilisés pendant un million d'heures une seule défaillance correspond à 1 fit ( 1  $année \approx 10^4 h$ ). En électronique, l'ordre de grandeur usuel pour des composants est de quelques fits à quelques milliers selon la complexité, la maturité de la technologie. . .

### 1.1.6 La durée de vie médiane MTTF (Median Time To Failure)

La durée de vie médiane représente la durée pour laquelle la moitié des composants est tombée en panne :

$$R(MTTF) = F(MTTF) = \frac{1}{2} \tag{1.9}$$

#### 1.1.7 La durée de vie moyenne MTBF (Mean Time Before Failure)

Tout comme le taux de défaillance, la durée de vie moyenne de bon fonctionnement est fréquemment utilisée. Elle s'exprime en fonction de la densité de défaillance f(t) ou de la fonction de fiabilité R(t):

$$MTBF = \int_0^\infty t' \ f(t') \ dt' \tag{1.10}$$

$$MTBF = \int_0^\infty R(t') \ dt' \tag{1.11}$$

## 1.2 La fiabilité des semiconducteurs

Avec la croissance exponentielle du taux d'intégration des circuits, les fonctions et les performances d'un équipement se complexifient, et les défaillances produites par les défauts augmentent. Un niveau de fiabilité élevé est donc devenu indispensable. Ceci signifie qu'un niveau de fiabilité encore plus élevé des différents composants qui composent le circuit ou le système est exigé. De grandes quantités de semi-conducteurs sont employées dans un équipement, et ils en réalisent souvent les fonctions principales, ainsi une fiabilité élevée est extrêmement importante.

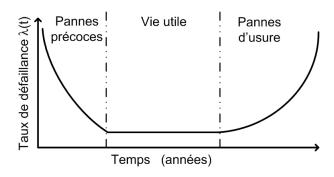

Le taux de défaillance est souvent employé comme un index général pour représenter la fiabilité des semi-conducteurs. Pour la plupart des systèmes, circuits ou composants électroniques étudiés, on peut distinguer trois phases successives dans l'évolution de ce taux. Cette dernière suit l'allure de la courbe de la figure 1.2. Cette courbe s'appelle la courbe en baignoire en raison de sa forme. Elle met en évidence que les durées de vie d'un composant électronique peuvent être réparties en 3 périodes :

Défaillances précoces : ces défaillances surviennent au début de l'utilisation du composant, lorsqu'un stress, telle qu'une température ou une tension, lui est appliqué. On parle alors de mortalité infantile ou de défaillances précoces. Elles sont caractérisées par un taux de défaillance

Figure 1.2 – Evolution du taux de défaillances d'une famille de composants en fonction du temps.

qui décroît rapidement au cours du temps. Elles sont essentiellement dues aux défauts générés, et qui ne peuvent être écartés, durant la phase de production et ce pour un procédé de fabrication donné. Ces composants potentiellement défaillants peuvent être écartés du marché par des procédures de déverminage, de contrôle du procédé de fabrication ou d'assurance qualité [64].

- Vie utile : cette notion de vie utile peut se rapporter à la fiabilité inhérente des produits dont le niveau est déterminé par la qualité de son design. Le produit a atteint sa pleine maturité, c'est la période utile de fonctionnement. Les défaillances qui surviennent sporadiquement durant cette phase de vie utile sont principalement la conséquence d'une mauvaise utilisation ou d'incidents (décharge électrostatique, humidité, variation de température ...). Toutefois, le taux de défaillance des composants peut être abaissé par l'intégration de modules au sein de la puce (circuits de protection contre les décharges électrostatiques et les surcharges électriques, blocs de correction en redondance passive ou active, ...), par la sous-sollicitation (« derating ») ou en les faisant évoluer sous des conditions environnementales normales d'utilisation.

- Pannes d'usure : La hausse du taux de défaillances au cours de la troisième phase correspond aux phénomènes d'usure des composants et marque ainsi la fin de vie utile de ce dernier. L'apparition de cette phase dépend directement des contraintes appliquées au composant et donc de son profil de mission. Le début de cette phase est très difficilement quantifiable. A ce stade, le vieillissement, induit par des dégradations accumulées au cours de la vie utile du composant, entraîne la dérive des caractéristiques électriques de ce dernier.

Il est vital de pouvoir influencer cette courbe afin de diminuer au maximum la première phase de défaillances précoces (contribuant ainsi à la diminution des coûts en service après-vente et en actions correctives), maintenir le taux de défaillance le plus bas durant la deuxième phase et anticiper la dernière phase afin d'améliorer le temps moyen de bon fonctionnement ou MTBF (Mean Time Between Failure) du système, circuit ou composant électronique.

Les semi-conducteurs, quant à eux, sont de plus en plus miniaturisés et fortement intégrés. Assurer leur fiabilité est donc devenu une question essentielle.

## 1.3 Estimation et analyse de la fiabilité

La plupart des fonctions de défaillances des circuits ou systèmes peuvent être classifiées en une (ou plusieurs) loi(s) de distribution. Cette section présente les quatre lois fréquemment utilisées lors de l'analyse de la fiabilité.

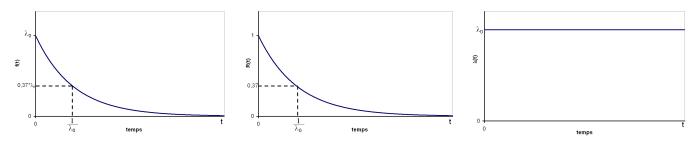

#### 1.3.1 Distribution exponentielle

Une loi de distribution exponentielle caractérise un circuit ou système ayant un taux de défaillance indépendant du temps, ce qui correspond à la période de vie utile d'une famille de composants (Cf. courbe en baignoire 1.2).

$$\lambda(t) = \lambda_0 \tag{1.12}$$

$$R(t) = \exp\left[-\lambda_0 \cdot t\right] \tag{1.13}$$

$$f(t) = \lambda_0 \exp\left[-\lambda_0 t\right] \tag{1.14}$$

$$MTBF = \frac{1}{\lambda_0} \tag{1.15}$$

Le MTTF correspond au temps pour lequel R(t) est équivalent à  $\frac{1}{2}$ , et est l'inverse du taux de défaillance. La loi de distribution exponentielle est la plus simple dans le domaine de la fiabilité.

(a) Évolution de la fonction de densité (b) Évolution de la fonction de fiabilité (c) Évolution du taux de défaillance de défaillance f(t).  $\lambda(t)$ .

Figure 1.3 – Évolution des fonctions caractéristiques de la fiabilité d'une famille de composants pour un taux de défaillance constant au cours du temps.

#### 1.3.2 Distribution normale ou gaussienne

La distribution normale est une loi très importante dans la théorie des statistiques et pour les applications actuelles. Elle est donc fréquemment utilisée lors de la modélisation des dispersions

statistiques des paramètres technologiques du CI, et rarement comme fonction de fiabilité.

$$\lambda(t) = \frac{exp\left[-\frac{(t-\mu)^2}{2\sigma^2}\right]}{\int_t^\infty exp\left[-\frac{(x-\mu)^2}{2\sigma^2}\right] dx}$$

(1.16)

$$R(t) = 1 - \frac{1}{\sqrt{2\pi} \sigma} \int_0^t exp \left[ -\frac{(x-\mu)^2}{2\sigma^2} \right] dx$$

(1.17)

$$f(t) = \frac{1}{\sqrt{2\pi} \sigma} exp \left[ -\frac{(t-\mu)^2}{2\sigma^2} \right]$$

(1.18)

$$MTBF = \mu \tag{1.19}$$

Où  $\mu$  est la valeur moyenne et  $\sigma$  l'écart type.

(a) Évolution de la fonction de densité (b) Évolution de la fonction de fiabilité (c) Évolution du taux de défaillance de défaillance f(t).  $\lambda(t)$ .

Figure 1.4 – Évolution des fonctions caractéristiques de la fiabilité d'une famille de composants pour une densité de défaillance suivant une distribution normale.

A partir de la figure 1.4, les temps pour lesquels les défaillances surviennent sont concentrés au centre de la courbe  $\mu \pm 3\sigma$  et correspondent aux défaillances dues au vieillissement d'une famille de composants (Cf. courbe en baignoire 1.2).

#### 1.3.3 Distribution Log-normale

Une distribution pour laquelle la variable lnt suit une loi normale est appelée distribution lognormale. Elle est donc équivalente à une substitution de t par lnt.

$$MTBF = exp\left[\mu + \frac{\sigma^2}{2}\right] \tag{1.20}$$

Où  $\mu$  est valeur moyenne et  $\sigma$  l'écart type.

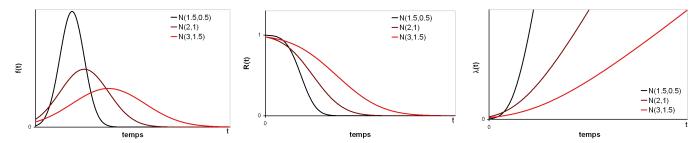

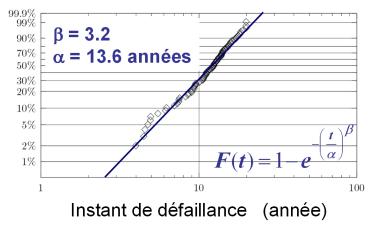

#### 1.3.4 Distribution de Weibull

La distribution de Weibull a été proposée par W. Weibull, un ingénieur suédois en mécanique. Chaque distribution des taux de défaillance, caractéristiques des trois zones de la courbe en baignoire (Cf. Fig.1.2), peut s'exprimer par la valeur du paramètre de Weibull m. Cette distribution est par conséquent très utilisée lors de l'analyse de la fiabilité des circuits et systèmes électroniques.

Les équations 1.21, 1.22 et 1.23 donnent respectivement les expressions du taux de défaillance  $\lambda(t)$ , de la fonction de la fiabilité R(t) et de la densité de défaillance f(t) en fonction des paramètres de Weibull m,  $\gamma$  et  $t_0$ .

$$\lambda(t) = \frac{m(t - \gamma)^{m-1}}{t_0} \tag{1.21}$$

$$R(t) = exp\left[-\frac{(t-\gamma)^m}{t_0}\right]$$

(1.22)

$$f(t) = \frac{m(t - \gamma)^{m-1}}{t_0} exp \left[ -\frac{(t - \gamma)^m}{t_0} \right]$$

(1.23)

$t_0$  est un paramètre d'échelle servant à la normalisation du temps.  $\gamma$  est un paramètre de position et correspond au temps à partir duquel la première défaillance survient. m est un paramètre de forme. A partir de la valeur de ce dernier, nous pouvons déterminer si le circuit ou système est dans sa période de vie infantile, utile ou d'usure.

- -m < 1: le taux de défaillance décroît au cours du temps caractérisant ainsi une défaillance précoce du circuit;

- -m=1: le taux de défaillance est indépendant du temps, ce qui correspond ainsi à une loi de distribution exponentielle. Le circuit se trouve dans sa période de vie utile;

- -m > 1: le taux de défaillance augmente au cours du temps et caractérise ainsi une défaillance due à l'usure du circuit ou système. Lorsque m est grand, les instants de défaillance sont faiblement dispersés.

(a) Évolution de la fonction de densité (b) Évolution de la fonction de fiabilité (c) Évolution du taux de défaillance de défaillance f(t). R(t).

Figure 1.5 – Évolution des fonctions caractéristiques de la fiabilité d'une famille de composants pour une répartition de leurs instants de défaillance suivant une distribution de Weibull.

# 1.4 Impact de la maturité d'une technologie sur la fiabilité intrinsèque d'une famille de composants

Lors de la conception d'un circuit intégré analogique, il est nécessaire non seulement de dimensionner chaque composant élémentaire pour satisfaire aux spécifications électriques nominales demandées à partir d'un modèle (déterministe), mais il faut également garantir que ces spécifications soient satisfaites compte tenu des dispersions technologiques susceptibles de modifier statistiquement certains paramètres du modèle.

D'un point de vue « fiabilité », l'influence des fluctuations des paramètres technologiques sur les dispersions statistiques des performances électriques d'un circuit entier constitue un indice sur la maturité de la technologie concernée.

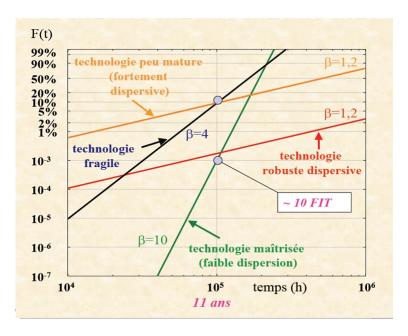

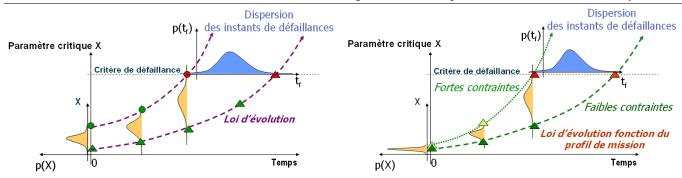

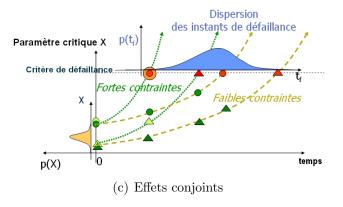

La figure 1.6 montre l'impact de la maturité de la technologie utilisée lors de la conception des circuits intégrés sur leur fiabilité intrinsèque. Ainsi, une technologie maîtrisée contribue à une faible dispersion des instants de défaillance d'une famille de circuits intégrés. A l'inverse, une technologie peu mature ou robuste peut induire une forte dispersion des instants de défaillance.

Figure 1.6 – Impact de la maturité de la technologie sur la fiabilité intrinsèque.  $\beta$  est le paramètre de forme de la loi de Weibull

Il est donc nécessaire, lors de la conception analogique en vue de la fiabilité, de prendre en compte ces inévitables dispersions technologiques afin d'évaluer l'impact de la maturité de la technologie ou encore la validité du dimensionnement des composants élémentaires sur les indices de performances électriques pour une famille de circuits intégrés donnée.

## 2 Le traitement de la fiabilité

L'évaluation de la fiabilité d'un circuit intégré est de vérifier à travers divers essais que ce circuit répondra à ses spécifications durant un temps t donné d'un profil de mission. Pour ce faire, les données expérimentales sont traitées statistiquement afin de déterminer les fonctions de défaillances précédemment définies.

Avant de réaliser toute série d'essais de fiabilité, il est important de définir l'ensemble des indicateurs de fiabilité. En premier lieu, il est essentiel de définir :

- la(les) fonction(s) réalisée(s) par le composant;

- les conditions de fonctionnement de ce dernier;

- les conditions environnementales dans lesquelles il va évoluer;

- le temps de la mission à laquelle il est destiné;

- l'ensemble des critères de défaillance;

- les indicateurs de fiabilité.

#### 2.1 Les essais de fiabilité

Tels que définis dans les standards industriels japonais JIS Z 8115, « les essais de fiabilité » est le terme général pour les essais permettant de déterminer le niveau de fiabilité, et les tests de conformité de la fiabilité. En d'autres termes, les valeurs caractéristiques de la fiabilité (taux de défaillance, fonction de fiabilité, durée de vie moyenne, MTTF...) sont évaluées et vérifiées statistiquement à l'aide des données résultant de ces essais. Ces tests jouent également un rôle important lors de l'amélioration de la fiabilité par l'analyse des mécanismes de défaillances qui se produisent au cours de ces derniers et de leur clarification.

Les essais de fiabilité doivent prendre en compte le niveau de stress nécessaire pour dégrader le circuit sous test, et simuler les conditions réelles d'utilisation de ce dernier. Bien que les conditions de ces tests doivent être les mêmes lors d'une utilisation normale du composant, il est très difficile d'obtenir des résultats précis et suffisants en des temps très courts et pour des coûts minimum.

En réalité, afin de réduire le temps, le nombre et les coûts des essais de fiabilité, les tests accélérés sont fréquemment utilisés en Industrie. Ces tests consistent à faire vieillir les composants en dehors de leurs gammes nominales d'utilisation. Généralement, l'intensité du stress lors de ces tests doit être non destructive et représentative pour permettre une analyse de défaillance cohérente et/ou une modélisation suffisamment précise de la fiabilité des circuits sous test.

Le domaine de validité des tests accélérés dépend du standard utilisé pour les effectuer. En effet, pour les circuits intégrés, différents standards ont été développés. Les plus connus sont les standards industriels japonais (JIS: Japanese industrial Standard), définis par l'association des industries en électronique du Japon (EIAJ: Electronic Industries Association of Japan) ou encore par la commission internationale en électrotechnique (IEC: International Electrotechnical Commission),

| Standard                                                                | Intitulé                                                                    |  |  |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| IEC Standard (International Electrotechnical Commission)                |                                                                             |  |  |

| Publication 68                                                          | Basic environment testing method                                            |  |  |

| Publication 147-5                                                       | Semiconductor Device Mechanical and climatic testing method                 |  |  |

|                                                                         | MIL Standard (Military Standard)                                            |  |  |

| MIL-STD-202F                                                            | Electronic and electric parts testing method                                |  |  |

| MIL-STD-750C                                                            | Discrete semiconductor devices testing method                               |  |  |

| MIL-STD-883C                                                            | Microelectronics testing method                                             |  |  |

|                                                                         | BS (British Standard)                                                       |  |  |

| BS-9300                                                                 | Semiconductor devices testing method                                        |  |  |

| BS-9400                                                                 | IC testing method                                                           |  |  |

|                                                                         | JIS Standard (Japanese Industrial Standard)                                 |  |  |

| JIS C7021                                                               | Environmental and endurance test methods for discrete semiconductor devices |  |  |

| JIS C7022                                                               | Environmental and endurance test methods for ICs                            |  |  |

| EIAJ Standard (Standards of Electronic Industries Association of Japan) |                                                                             |  |  |

| SD-121                                                                  | Environmental and endurance test methods for discrete semiconductor devices |  |  |

| IC-121                                                                  | Environmental and endurance test methods for ICs                            |  |  |

Tableau 1.1 – Principaux standards pour les essais de fiabilité.

les standards militaires américains (MIL-STD : MILitary STanDard) ou les standards britanniques (BS : British Standard).

Les essais de fiabilité sont utilisés pour évaluer la fiabilité d'un composant, ou mettre en évidence les mécanismes de dégradation ou des défauts de jeunesse de ce dernier. Les résultats de ces essais sont ensuite utilisés pour faire des prévisions sur la durée de vie réelle, les performances de ce composant ou pour établir ses conditions d'utilisation. Il est important de tester le composant hors de ces spécifications lors de ces essais afin de définir les conditions nominales de fonctionnement réelles de ce produit.

#### 2.2 Notion de « critère de défaillance »

Avant tout essai de fiabilité, il est nécessaire de définir le(s) critère(s) de défaillance qui va (vont) permettre de juger de la qualité d'un composant. Cependant, il existe plusieurs types de défaillances, et les résultats des essais de fiabilité différeront considérablement selon la validité du (des) critère(s) de défaillance choisi(s). En effet, la distinction entre un défaut dit catastrophique (tel qu'un court circuit ou une fusion de la métallisation) et un défaut dit paramétrique (tel que l'augmentation d'un courant de fuite) dépend essentiellement du niveau de la dégradation et de l'impact de cette dernière sur la fonctionnalité du composant.

Plusieurs paramètres caractéristiques du composant évoluent au cours d'un test de fiabilité. Par conséquent, il y a deux points importants à définir lors de la détermination d'un critère de défaillance :

- fixer une marge de tolérance à partir des caractéristiques et des conditions de fonctionnement

du composant;

- déterminer les limites du contrôle de fiabilité.

Le premier fait appel à une méthode de détermination à partir des caractéristiques nominales requises d'un composant pour lesquelles on prend en compte une tolérance supplémentaire à la spécification du composant; le second est relatif à une méthodologie de détermination basée sur la physique des défaillances, tels les modes de défaillances ou les mécanismes de défaillances de ces composants.

Le tableau 1.2 présente des exemples de critères de défaillance, déterminés à partir des données fournies par le constructeur, pour des circuits intégrés linéaires. Généralement, ces critères de défaillance ne montrent pas les limites à partir desquelles un système est probablement défaillant lors d'une utilisation réelle de ce dernier, mais ils sont basés sur les notions de niveaux de dégradations des paramètres, dues aux tests de fiabilité, et d'évaluation de la qualité et de la fiabilité en des temps très courts.

| Caractéristiques électriques      | Caractéristiques électriques Critères de défaillance |                                  | Unité         |

|-----------------------------------|------------------------------------------------------|----------------------------------|---------------|

|                                   | Limite inférieure                                    | Limite supérieure                |               |

| Voltage gain                      | L - 3                                                | U+3                              | dB            |

| Output power                      | L - 0.9                                              | _                                | W             |

| Full harmonic distorsion factor   | _                                                    | U x 1.5                          | %             |

| Output noise voltage              | _                                                    | U x 1.5                          | mV            |

| Input limiting voltage            | _                                                    | $U + 3 \text{ or } U \times 1.5$ | dB or $\mu V$ |

| Suplly current                    | _                                                    | U x 1.1                          | A             |

| Input offset voltage              | _                                                    | U x 1.5                          | V             |

| Input offset current              | _                                                    | U x 1.5                          | A             |

| Input current, Input bias current | _                                                    | U x 1.3                          | A             |

| Maximum output voltage amplitude  | L x 1.1                                              | U x 0.9                          | V             |

**Tableau 1.2** – Exemples de critères de défaillance pour des circuits intégrés linéaires. L et U sont respectivement les limites minimales et maximales définies par la spécification du constructeur.

# 2.3 Les mécanismes de défaillances physiques

Les composants semi-conducteurs n'échappent pas aux phénomènes physiques de dégradation. Plusieurs mécanismes physico-chimiques peuvent provoquer des défaillances. Ces défaillances peuvent être de type catastrophique : le composant ne fonctionne plus du tout. Ou elles peuvent être de type paramétrique : le composant voit ses caractéristiques électriques dériver. Cette section a pour objectif de donner un aperçu des mécanismes de dégradation affectant les performances des circuits intégrés. Cet aperçu (tableau 1.3) comprend les défaillances affectant aussi bien le composant élémentaire comme le transistor, le circuit intégré ou un système électronique, sans oublier les défaillances dues

aux assemblages et interconnexions. Les défaillances et les mécanismes de dégradation en électronique se classent selon deux catégories : les défaillances intrinsèques et les défaillances extrinsèques.

#### 2.3.1 Les défaillances intrinsèques

Les défaillances intrinsèques surviennent pour des conditions d'utilisation répondant aux spécifications du composant et sont liées à plusieurs facteurs :

- 1. la conception du composant

- 2. les matériaux utilisés

- 3. les procédés de fabrication

- 4. l'assemblage du composant

- 5. l'encapsulation du composant

- 6. le vieillissement des matériaux

Elles sont à l'origine des défaillances précoces ou d'usures des composants et surviennent sur la première et la troisième régions de la courbe en baignoire (Cf figure 1.2, page 9).

#### 2.3.2 Les défaillances extrinsèques

Les défaillances extrinsèques sont causées par des conditions d'utilisation provoquant le dépassement de valeurs critiques :

- 1. les surcharges électriques (EOS)

- 2. les décharges électrostatiques (ESD)

- 3. la manipulation du composant

- 4. les surcharges mécaniques, thermiques, chimiques

- 5. l'utilisation non correcte du composant

Ces défaillances extrinsèques surviennent sur la période de vie utile du composant.

## 2.3.3 Effets sur les performances électriques

Un classement des différentes défaillances rencontrées en électronique est proposé dans le tableau 1.3. Nous faisons une description sommaire des effets induits par les modes de dégradation sur le fonctionnement électrique d'un composant élémentaire, d'un circuit ou d'un système électronique.

Du procédé de fabrication, où le silicium est à l'état pur, à la mise sur le marché et son intégration dans un système électronique complexe, le composant électronique subit des contraintes variées et plus ou moins actives selon l'étape de production.

| Mécanisme de défaillance                               | Effets                                                                                  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Défauts cristallins                                    | Dérives des paramètres électriques                                                      |

| Fissures                                               | Circuits ouverts dans les cas extrêmes                                                  |

| Contamination ionique                                  | Modification de la tension de seuil (MOS) ou variation du gain (BIP)                    |

| Charge de surface                                      | Modification des courants de fuite et tensions de claquage (pour les composants actifs) |

| Porteurs chauds                                        | Création d'une charge fixe dans l'oxyde,                                                |

|                                                        | Dérive de la tension de seuil (MOS), dégradation de la mobilité des porteurs            |

| Claquage de diélectrique                               | Court-circuit, défauts d'isolement                                                      |

| Défauts d'oxyde                                        | Courant de fuite excessif, pertes de données (pour les mémoires)                        |

| Electromigration                                       | Circuit-ouvert (lignes de métallisation)                                                |

| Migration métallique                                   | Court-circuit (dépôt d'aluminium), apparition de dendrites                              |

| Fissures des pistes métalliques                        | Circuit-ouvert/court-circuit (fissures et déformation, corrosion),                      |

| Fissures de la passivation                             | Fuite des transistors (fissures dans la grille en polysilicium)                         |

| Oxydation & Corrosion des<br>broches                   | Circuit-ouvert                                                                          |

| Croissance d'inter-métallique<br>au niveau des broches | Augmentation des résistances électriques                                                |

| Décollement de la puce                                 | Variation des résistances électriques et thermiques,                                    |

| Fractures/trous                                        | Circuit-ouvert                                                                          |

| Croissance d'inter-métalliques                         | Fragilisation(circuit-ouvert), augmentation de la résistance du fil d'in-               |

| Au/Al                                                  | terconnexion                                                                            |

| Rupture & Décollement                                  | Circuit-ouvert, court-circuit(fils trop longs)                                          |

| des fils d'interconnexion                              | Augmentation des densités de courant                                                    |

| Décharges électrostatiques                             | Court-circuit (claquages des oxydes)                                                    |

| Surcharges électriques                                 | Effet thermique, forte intensité (fusion des matériaux)                                 |

**Tableau 1.3** – Effets des mécanismes de défaillance physique sur les performances électriques des composants.

L'électromigration, le claquage d'oxyde, la contamination ionique ou d'autres participent aussi bien à la mortalité infantile qu'aux phénomènes d'usure qui induisent une modification des caractéristiques électriques d'un circuit intégré. D'autres phénomènes contribuent essentiellement au vieillissement électrique comme l'injection de porteurs chauds ou l'étalement de charges en surface.

Des travaux expérimentaux conduisent à la définition de modèles physiques (souvent empiriques) des mécanismes physiques de défaillance. Aujourd'hui, ces modèles sont intégrés dans les bibliothèques d'outils de simulation. Ces outils proposent des modèles physiques destinés à l'analyse de mode de dégradation comme l'électromigration, l'injection de porteurs chauds ou le claquage d'oxyde. Ces outils offrent la possibilité de **simuler** ces mécanismes de dégradation **au niveau transistor**.

## 2.4 La physique des défaillances

La physique des défaillances (*POF*, *Physics of Failure*) [48] [64] est le terme général pour l'identification et la compréhension des processus physiques et des mécanismes de défaillance. Elle consiste à modéliser par une loi physique analytique chaque mécanisme de défaillance qui intervient au cours des essais de fiabilité. Elle se base sur les connaissances de la physique des composants pour évaluer les modes de dégradation. Elle vise à isoler les différentes causes de défaillance possibles et à les caractériser séparément en appliquant pendant les tests des contraintes plus importantes que celles rencontrées durant l'utilisation normale du composant. Il est important dans ces conditions de bien comprendre les mécanismes responsables des dégradations afin de déterminer les paramètres qui permettront d'accélérer suffisamment le phénomène de dégradation tout en restant représentatif des conditions nominales d'utilisation. La compréhension du mécanisme de dégradation permet, grâce à des modèles plus ou moins empiriques, de se replacer dans les conditions nominales de fonctionnement à partir des données collectées lors des tests de vieillissement accélérés.

## 2.5 Conclusion

L'analyse de la fiabilité permet d'évaluer le niveau de dégradation d'une famille de circuits intégrés à travers divers essais. A la différence de la méthode statistique, l'approche « physique des défaillances » s'oriente vers une approche physique de la fiabilité et propose, pour une mission donnée, de relier les causes, donc les contraintes, aux effets induits par les défaillances physiques sur les performances électriques des composants [32] [43]. L'information résultante est utilisée pour construire des modèles de fiabilité des composants élémentaires.

Cependant, l'évolution du taux d'intégration suivant la deuxième loi de Moore [59] rend l'analyse de la fiabilité via la physique des défaillances de plus en plus difficile à cause de l'apparition de nouveaux mécanismes de dégradation. En plus d'une évolution rapide du taux d'intégration, la complexité des circuits et des fonctions réalisées augmente considérablement et les environnements sévères se banalisent. Pour répondre aux niveaux de fiabilité demandés aux composants intégrés dans des systèmes, des taux de défaillance inférieurs à 1 FIT (10<sup>-9</sup>panne/heure) sont indispensables. Cette exigence est impossible à démontrer par des méthodes statistiques traditionnelles car elles conduisent à des temps et des coûts prohibitifs.

Afin de réduire les coûts de conception et de test, le traitement de la fiabilité doit donc intervenir au plus tôt dans le cycle de production des circuits intégrés.

# 3 La conception en vue de la fiabilité : de la modélisation SPICE à la modélisation comportementale

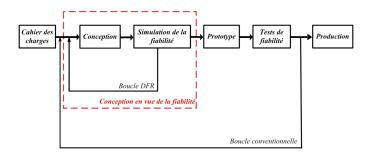

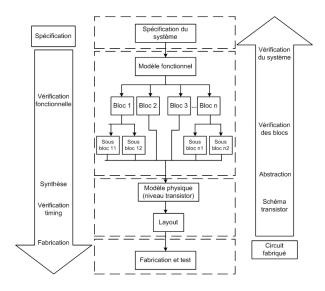

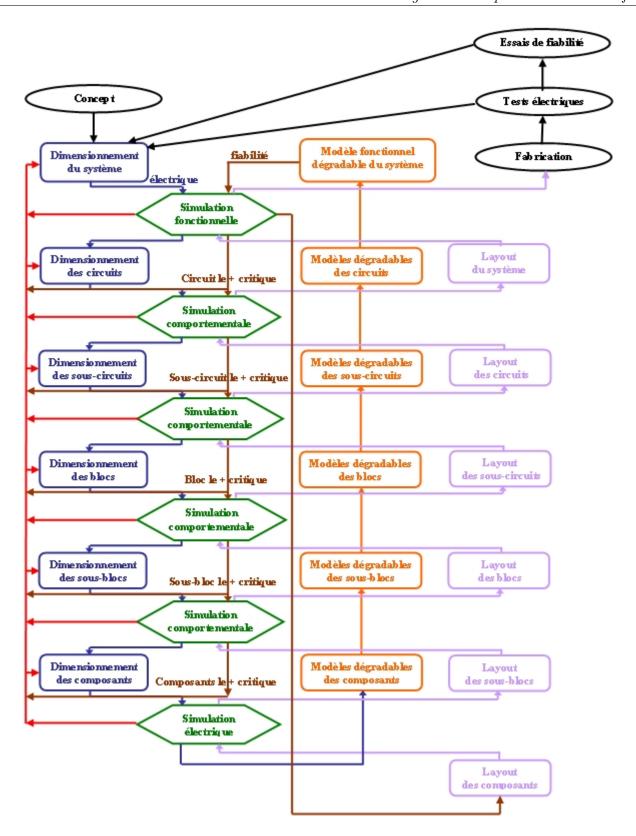

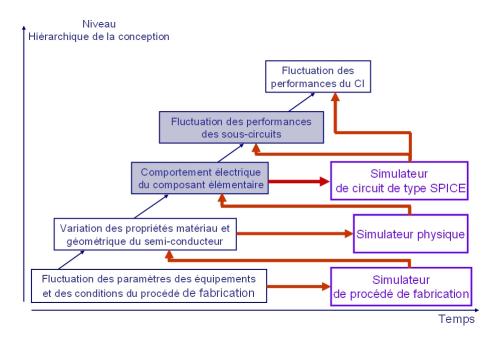

L'évolution croissante des fonctionnalités des circuits, ainsi que la croissance exponentielle du taux d'intégration, amènent les experts de la microélectronique à se diriger vers une fiabilité construite. Le traitement de la fiabilité doit donc être réalisé dès la phase de conception des circuits intégrés afin de réduire les coûts en actions correctives. On parle alors de conception en vue de la fiabilité. La plupart des stratégies DFR (Design for Reliability) sont basées sur le synoptique de la figure 1.7 [75] [36] et consistent en l'étude de la fiabilité par des simulations électriques. La simulation de la fiabilité devient dès lors une activité à part entière et est un véritable challenge pour les experts.

Figure 1.7 – Cycle de production des circuits intégrés incluant la conception en vue de la fiabilité.

Divers travaux [70] [71] se focalisent alors sur le développement d'outils de simulations électriques dédiés à la fiabilité des semi-conducteurs. On parle alors de simulation de la fiabilité.

L'objectif premier de celle-ci est de prévoir le comportement d'un circuit ou système pour un profil de mission donnée. En d'autres termes, la simulation de la fiabilité doit permettre d'évaluer le niveau de dégradation (ou encore le vieillissement) du comportement de ce circuit ou système pour un ou plusieurs mécanisme(s) de dégradation, et ce pour une durée de mission donnée. A l'aide de ces outils de simulation, le concepteur doit pouvoir estimer l'effet d'un mécanisme de dégradation sur les fonctionnalités d'un circuit, au même titre qu'il effectue des simulations fonctionnelles pour contrôler les performances de ce circuit.

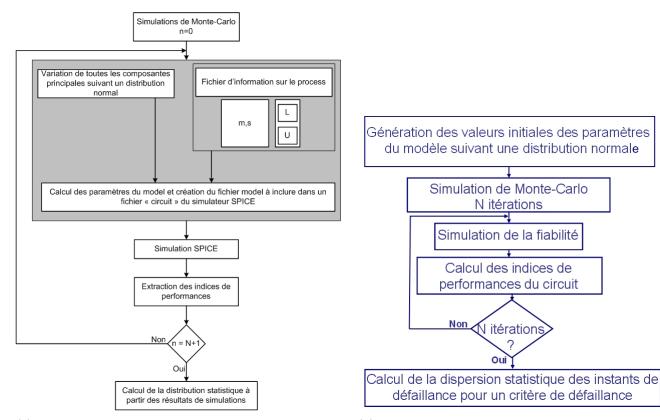

## 3.1 Environnement de simulation de la fiabilité

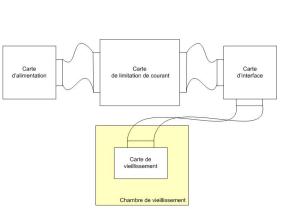

Les outils existants de simulation de la fiabilité sont développés autour d'un simulateur de type SPICE (Simulation Program with Integrated Circuit Emphasis). SPICE [60] [82] a été développé à l'origine par l'université de Californie, Berkeley. Ce simulateur est jumelé à des modules de dégradations physiques pour estimer la dégradation au cours du temps des composants élémentaires, et naturellement celle du circuit intégré. L'environnement de simulation de tels outils est défini par le synoptique de la figure 1.8.

Figure 1.8 – Schéma synoptique d'un simulateur de fiabilité des circuits intégrés.

La simulation de la fiabilité d'un système implique l'utilisation de deux modules assurant l'interface entre le simulateur électrique SPICE et les modules de dégradations physiques :

- un pré-processeur qui analyse le fichier d'entrée et le modifie pour le rendre compatible avec le logiciel de simulation électrique; il rajoute éventuellement des instructions pour demander au simulateur les tensions et/ou courants dans le circuit dont il a besoin pour calculer les dégradations;

- et un post-processeur qui récupère les données de sortie du simulateur électrique et calcule le niveau d'usure de chaque transistor. La plupart du temps, c'est le même modèle qui est utilisé à savoir une approche quasi-statique des dégradations.

# 3.2 Simulation du vieillissement des circuits intégrés

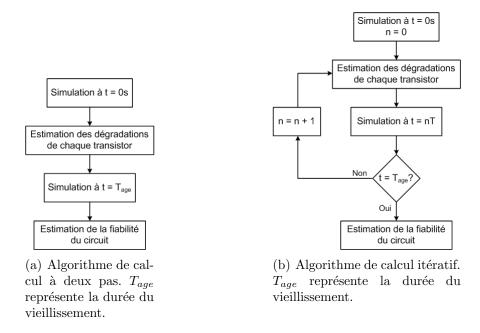

La simulation de vieillissement électrique nécessite la prise en compte d'une échelle temporelle qui s'avère être supérieure de plusieurs ordres de grandeur à la durée d'une analyse transitoire traditionnelle. Elle doit donc être réalisée à l'aide d'une analyse transitoire pouvant avoir une durée équivalente à quelques heures, voire plusieurs mois ou années. Le simulateur SPICE doit donc être capable de gérer ces deux échelles de temps. La gestion de cette double échelle de temps est réalisée par l'intermédiaire de deux méthodes : la double simulation et la simulation itérative.

Le principe de la double simulation [41] (figure 1.9(a)) est de lancer une première simulation électrique afin de déterminer, à partir du point de polarisation, les contraintes courant/tension du circuit et des transistors élémentaires. A la fin de cette simulation, les modules de dégradations physiques estiment d'abord l'importance de la dégradation au bout d'un temps donné puis l'effet de cette dernière sur les paramètres de chaque transistor élémentaire par rapport à leurs contraintes. Une seconde simulation est alors lancée en prenant en considération les paramètres dégradés obtenus des transistors. Le but de cette seconde simulation est d'estimer l'évolution du comportement électrique des transistors après une durée de vieillissement donnée, puis d'évaluer l'impact de ces dérives électriques élémentaires sur les caractéristiques électriques du circuit. Cette méthode a pour objectif de faire une estimation rapide de la fiabilité d'un circuit intégré pour une durée  $T_{age}$  de vieillissement donnée.

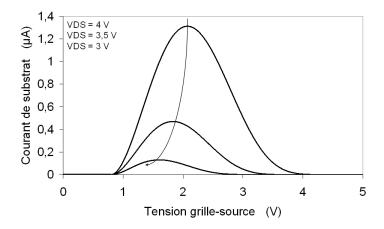

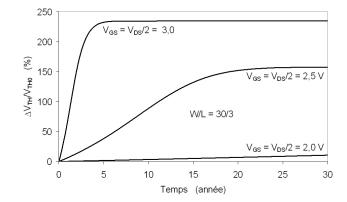

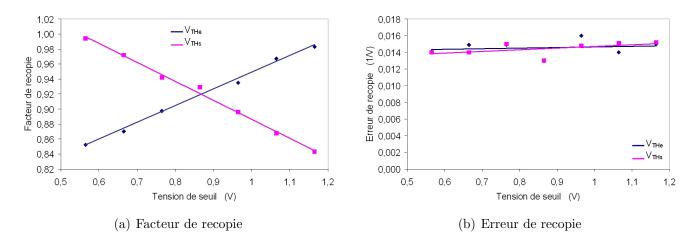

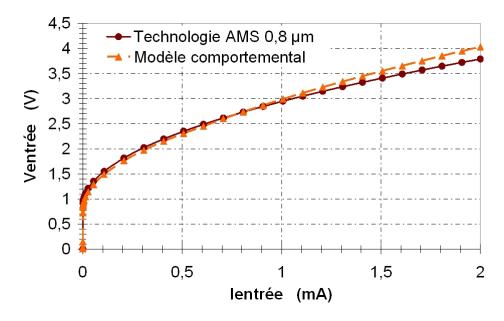

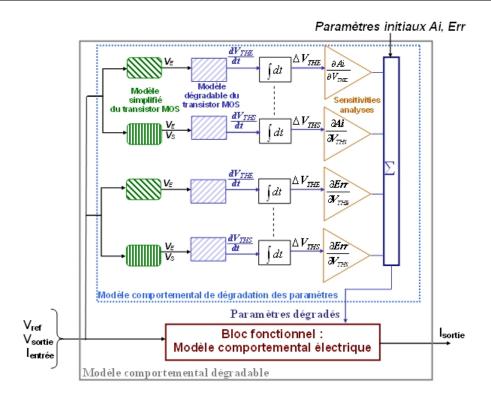

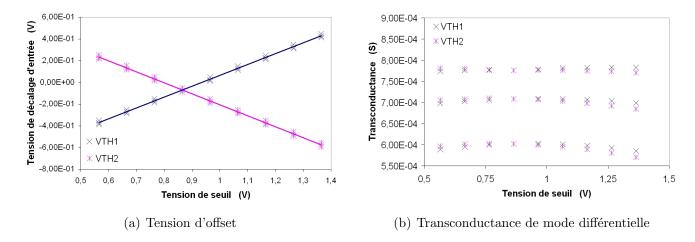

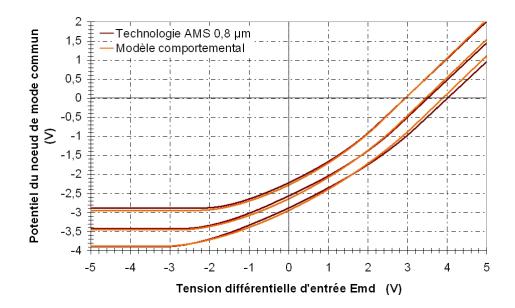

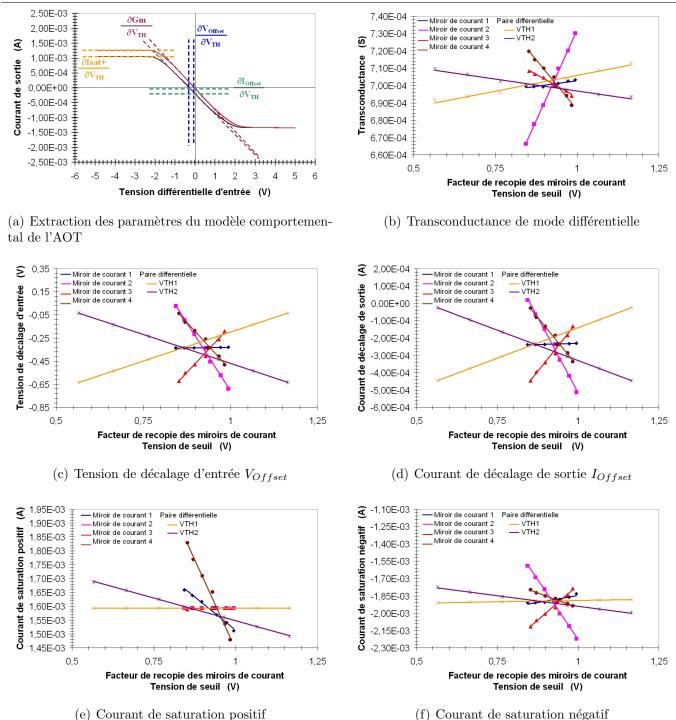

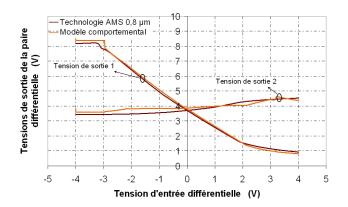

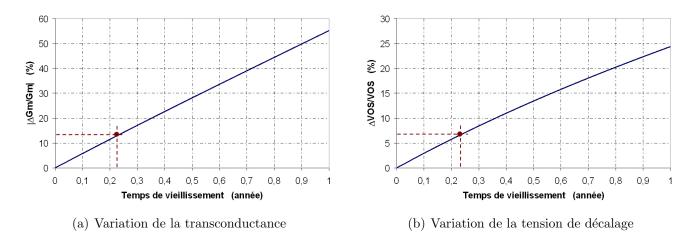

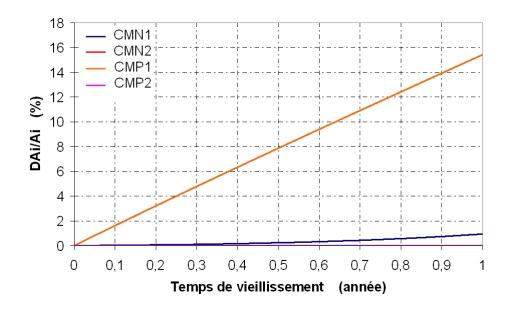

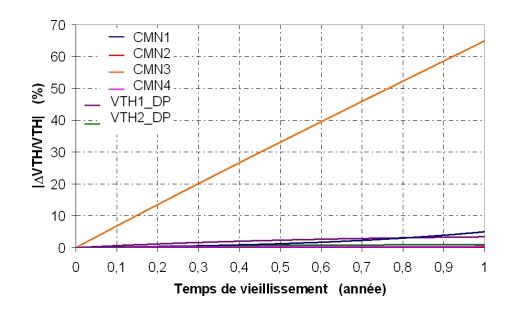

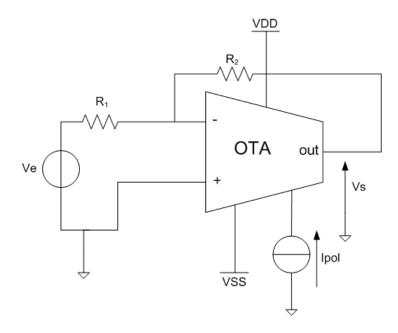

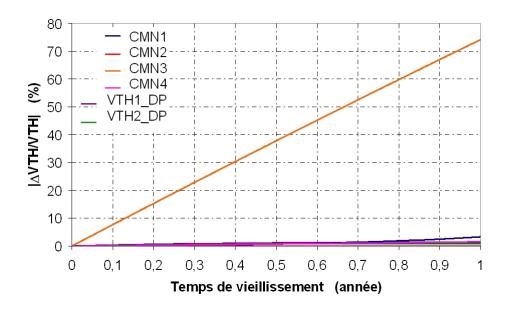

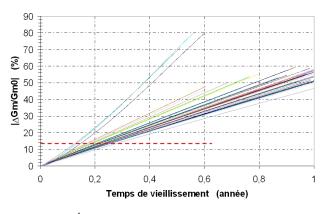

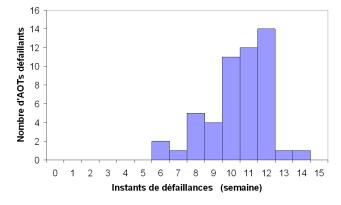

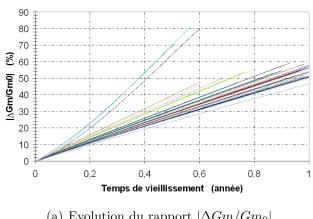

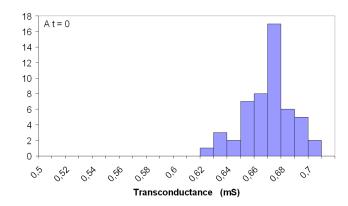

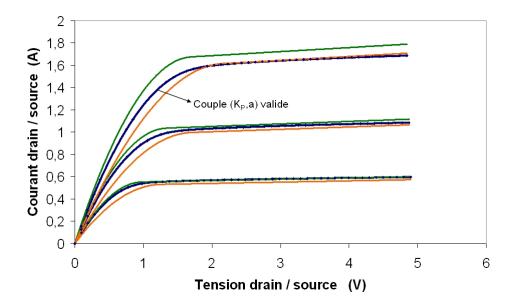

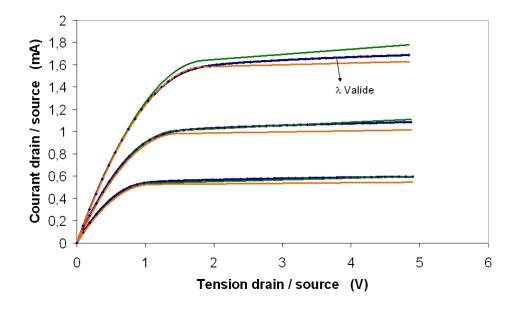

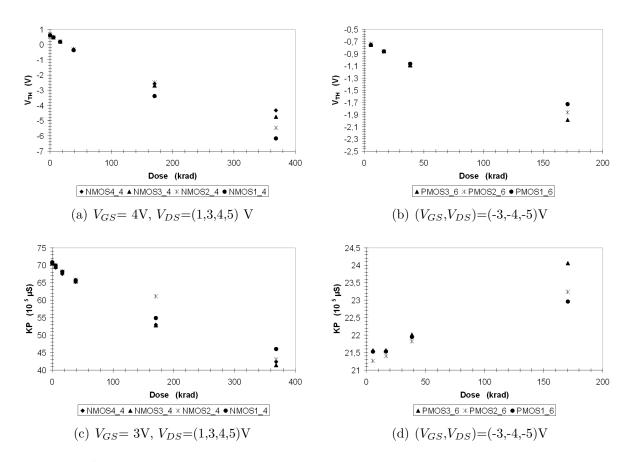

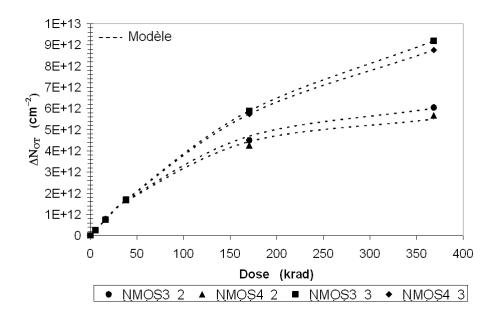

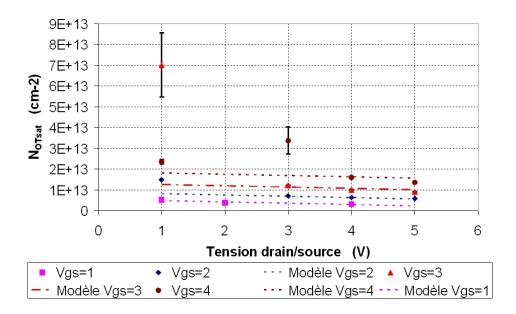

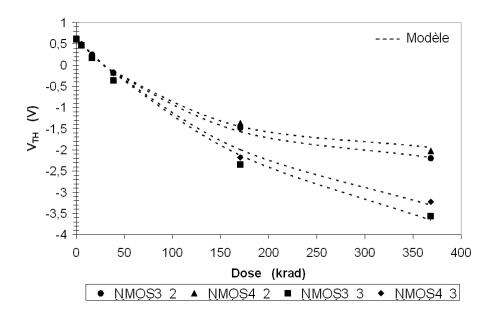

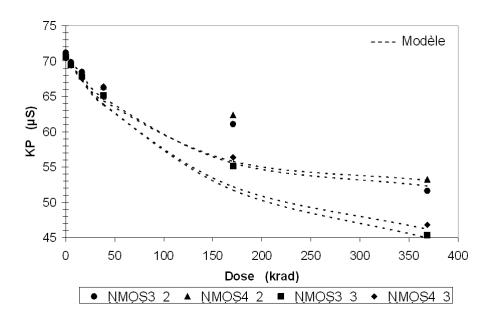

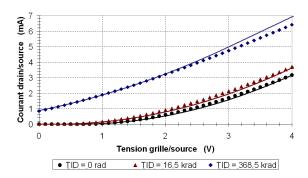

Le principe de la simulation itérative [35] [29] (figure 1.9(b)) reprend celui de la simulation double à