### AIX-MARSEILLE UNIVERSITÉ STMICROELECTRONICS ED 353 – SCIENCES POUR L'INGÉNIEUR

INSTITUT MATERIAUX MICROÉLECTRONIQUE NANOSCIENCES DE PROVENCE

Thèse présentée pour obtenir le grade universitaire de Docteur

Discipline : Sciences pour l'ingénieur Spécialité : Micro et Nanoélectronique

### Guénolé LALLEMENT

#### Extension of SoCs Mission Capabilities by Offering Near-Zero-Power Performances and Enabling Continuous Functionality for IoT Systems

Circuits à empreinte énergétique quasi nulle permettant une extension des profils de mission et un fonctionnement continu des systèmes destinés à l'Internet-des-Objets

Soutenue le 12/11/2019 devant le jury composé de :

- Pr. Massimo Alioto, National University of Singapore *Président & Rapporteur*

- Pr. David Bol, Université Catholique de Louvain Rapporteur

- Dr. Édith Beigné, Facebook Examinateur

- Dr. Pascal Vivet, CEA-Leti Examinateur

- Dr. Martin Cochet, IBM Research Examinateur

- M. James Myers, ARM Ltd. Invité

- Dr. Fady Abouzeid, STMicroelectronics *Encadrant industriel*

- Pr. Jean-Luc Autran, Aix-Marseille Université Directeur de thèse

- Dr. Daniela Munteanu, Aix-Marseille Université Co-Directrice de thèse

Numéro national de thèse/suffixe local: 2019AIXM0573/033ED353

Cette œuvre est mise à disposition selon les termes de la Licence Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International

À mes parents.

### Abstract

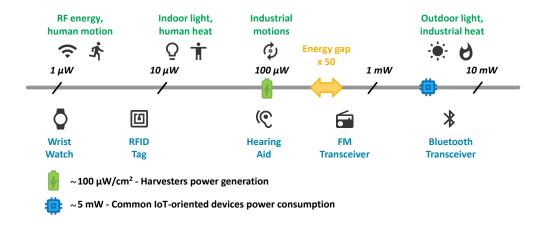

Recent developments in the field of low voltage Integrated Circuits (IC) have paved the way towards energy efficient electronic devices in a booming global network called the Internet-of-Things (IoT) or the Internet-of-Everything (IoE). However, the sustainability of all these interconnected sensors is still undermined by the constant need for either an on-board battery – that must be recharged or replaced – or an energy harvester with very limited power efficiency. The power consumption of present consumer electronic systems is fifty times higher than the energy available by cm<sup>2</sup>-size harvester or limited to a few months on a small battery, thus hardly viable for lifetime solutions. Upcoming Systems-on-Chip (SoCs) must overcome the challenge of this energy gap by architecture optimizations from technology to system level.

The technical approach of this work aims to demonstrate the feasibility of an efficient Ultra-Low-Voltage (ULV) and Ultra-Low-Power (ULP) SoC using exclusively latest industrial guidelines in 28 nm and 22 nm Fully Depleted Silicon On Insulator (FD-SOI) technologies. A hundred of nano watts leakage-based oscillator has been designed for synchronous digital clocking of the system's always-on parts. Dynamic self-biasing techniques enabled in FD-SOI are implemented to provide system speed-up during SoCs active operations, without incurring leakage current penalties during standby periods. Temperature compensation is also evaluated to increase robustness at low voltages. Several multi-power-domain SoCs based on Advanced RISC Machines (ARM) cores are implemented to demonstrate wake up strategies based on sensors inputs. By optimizing the system architecture, properly selecting and designing components with technology features chosen adequately, carefully tuning the implementation, a fully energy-optimized SoC is realized. Lastly, machine learning techniques coupled with the different power modes offered by the core enhance the system state restoration mechanisms. Depending on the application timing constraints (real-time vs. energy-saving) the proper standby mode can be selected to minimize the overall power consumption.

*Keywords* — 22 nm FDX, 28 nm FD-SOI, adaptive power management, body biasing, digital circuit design, energy-efficiency, machine learning, microcontroller (MCU), minimum energy point, ultra-low-power (ULP), ultra-low-voltage (ULV).

## Résumé

Les développements récents dans le domaine des circuits intégrés (IC) à basse tension ont ouvert la voie à des dispositifs électroniques économes en énergie dans un réseau mondial en plein essor appelé l'Internet des objets (IoT) ou l'Internet des choses (IoE). Cependant, la durabilité de tous ces capteurs interconnectés est compromise par le besoin constant d'une batterie embarquée - qui doit être rechargée ou remplacée - ou d'un récupérateur d'énergie à rendement très limité. La consommation d'énergie des systèmes électroniques grand public actuels est en effet cinquante fois plus élevée que celle d'un collecteur d'une taille de l'ordre du cm<sup>2</sup>, ou limitée à quelques mois sur une petite batterie. Cela contraint la viabilité de solutions fonctionnant à l'échelle d'une vie humaine. Les systèmes sur puce (SoCs) à venir nécessitent donc de relever le défi de cette lacune énergétique en optimisant l'architecture de la technologie au niveau du système.

L'approche technique de ce travail vise à démontrer la faisabilité d'un SoC efficient, ultra-basse tension (ULV) et ultra-basse puissance (ULP) utilisant exclusivement les dernières directives industrielles en matière de technologies FD-SOI (Fully Depleted Silicon On Insulator) 28 nm et 22 nm. Un oscillateur à courants de fuite consommant une centaine de nanowatts a été conçu pour fournir aux éléments toujours actifs du système une horloge numérique synchrone. Des techniques de polarisation automatiques et dynamiques, disponibles en FD-SOI, sont mises en œuvre pour accélérer le SoC pendant les opérations actives, sans encourir de pénalité liée aux courants de fuite pendant les périodes de veille. La compensation de température est également évaluée pour augmenter la robustesse à basse tension. Plusieurs SoCs multi-domaines basés sur des cœurs Advanced RISC Machines (ARM) sont implémentés pour démontrer des stratégies de réveil basées sur les entrées des capteurs. Ainsi, en optimisant l'architecture du système, en sélectionnant et en concevant correctement les composants avec des caractéristiques technologiques choisies de manière adéquate, et en ajustant soigneusement l'implémentation physique, on obtient un SoC entièrement optimisé en énergie. Enfin, des techniques d'apprentissage machine couplées aux différents modes de consommation offerts par le SoC améliorent les mécanismes de restauration de l'état du système. En fonction des contraintes de temps de l'application (temps réel vs. économie d'énergie), un mode de veille approprié peut être sélectionné pour minimiser la consommation d'énergie globale.

*Mots-clés* — 22 nm FDX, 28 nm FD-SOI, apprentissage machine, conception de circuits numériques, efficience énergétique, gestion de puissance adaptative, microcontroleur (MCU), point energétique minimum, polarisation du substrat, ultra-basse-consommation (ULP), ultra-basse-tension (ULV).

### Résumé en français

POUSSÉ par la multiplication des applications sans fil, interconnectées et à faible coût, il est établi que l'Internet des Objets (*Internet-of-Things*, IoT) occupera une position prédominante dans nos sociétés de plus en plus connectées [1]. Cependant, cette croissance est limitée par la consommation d'énergie des éléments embarqués sur ces objets de plus en plus complexes.

Ainsi, dans nos sociétés qui cherchent à réduire leur consommation, un double problème se pose. D'un côté, une augmentation rapide des besoins en énergie est nécessaire pour répondre au nombre croissant d'appareils. De l'autre, les applications hétérogènes proposées souffrent d'une autonomie limitée et de la détérioration des batteries embarquées, ce qui impose un remplacement des appareil au fur et à mesure de leur utilisation.

Ces tendances établissent le contexte général de ce travail; promouvoir un fonctionnement continu des systèmes destinés à l'IoT, tout en garantissant un large éventail de profils de mission. Ce manuscript étant rédigé en langue anglaise, un résumé en français des recherches menées lors de cette thèse est proposé dans les pages suivantes.

#### Introduction

Les appareils électroniques reposant sur la simple utilisation de piles inter changeables n'étant plus une option pérenne [2], les prochains Systèmes-sur-Puce (*System-on-Chip*, SoC) doivent relever le défi de la collecte, du stockage et de la gestion de l'énergie pour une consommation et une distribution efficace et durable [3].

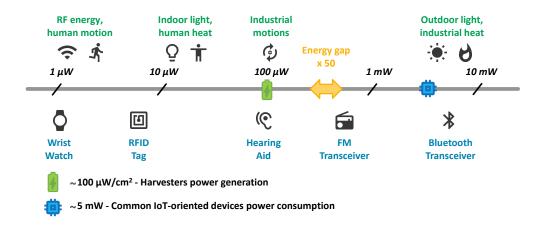

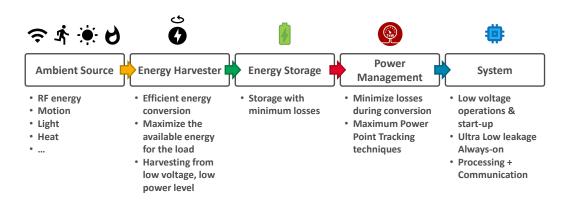

Un aperçu des différentes sources d'énergies qui peuvent être exploitées pour alimenter directement ou indirectement un système est proposé Figure 1. Pour chaque source, l'estimation de la puissance disponible est rapportée pour une surface unitaire de 1 cm<sup>2</sup>. En raison de l'efficacité limitée du dispositif qui collecte l'énergie (*energy harvester*), cette puissance disponible n'est jamais exploitée avec un processus de conversion parfait (*i.e.:* avec 100% d'efficacité). Afin d'estimer les fonctions actuellement réalisables avec ces budget énergétiques, la consommation de divers appareils électroniques grand public est reportée au bas du graphique. Pour les SoCs destinés à l'IoT, un budget énergétique réaliste de ~100 $\mu$ W/cm<sup>2</sup> peut être défini, tandis que la consommation d'énergie des systèmes de type IoT est de l'ordre de 5 mW selon l'application demandée [1]. La consommation d'énergie de ces systèmes est donc 50 fois plus élevée que l'énergie disponible.

Figure 1: Puissance disponible par un collecteur d'énergie pour une surface équivalente de 1 cm<sup>2</sup> comparée à la consommation de dispositifs électroniques standards.

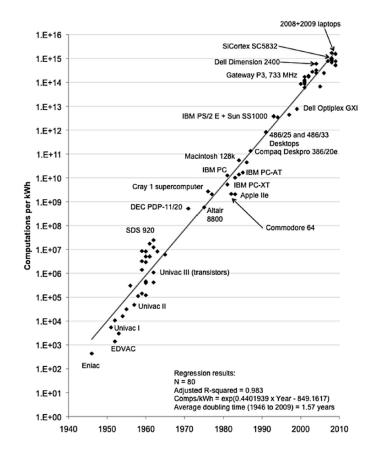

Suite aux implications de la loi de Koomey – qui suppose que la quantité de puissance requise pour une charge de calcul donnée diminue d'un facteur 2 tous les 1,5 ans [4] – cet écart peut être comblé au delà de 9 années (~2026). Des innovations de conception sont ainsi nécessaires pour disposer rapidement de nouveaux objets intelligents avec des opérations sans charge.

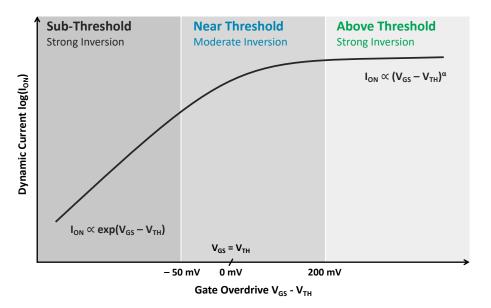

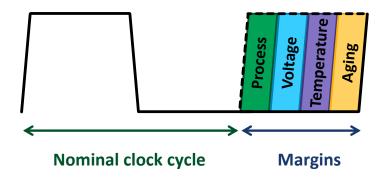

Afin d'offrir des appareils autonomes en énergie, un premier levier consiste à réduire la tension d'alimentation. Cependant, pour les nœuds technologiques avancés, cette solution accroît la sensibilité aux variations PVT (*Process, Voltage, Temperature*) et aux courants de fuite, limitant en retour les opérations en mode actif et en mode repos [5, 6]. Pour pallier ces lacunes, des techniques ont donc été déployées, mais elles entraînent logiquement une augmentation de la consommation d'énergie et des défis supplémentaires en termes de conformité aux normes de l'industrie.

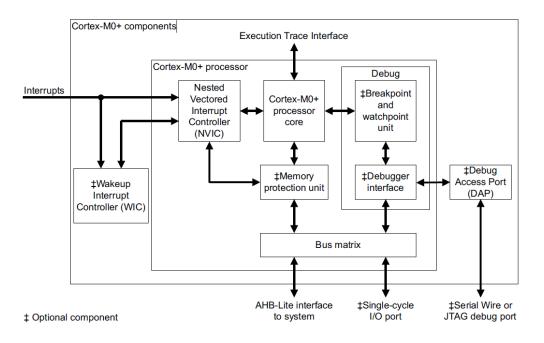

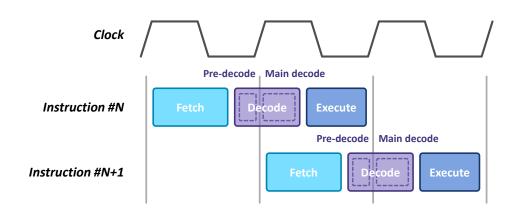

L'approche technique de cette thèse vise donc à démontrer la faisabilité d'un SoC efficace énergétiquement, à très faible consommation et tension, tout en utilisant exclusivement les dernières directives industrielles. Par conséquent le travail de manuscrit cherche à pousser le marché des microcontrôleurs (MCU) grand public vers une consommation de l'ordre du microWatt (*Ultra-Low-Power*, ULP). Pour cela, il convient de travailler sur l'optimisation de l'architecture, la sélection des composants, tout en suivant les caractéristiques technologiques adéquates. Une utilisation appropriée des différents modes de puissance offerts par le Cortex-M0+ est également associé à des solutions d'apprentissage machine (*Machine Learning*, ML).

#### **Contexte Applicatif et Technologique**

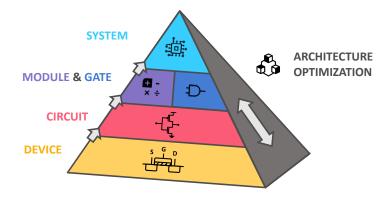

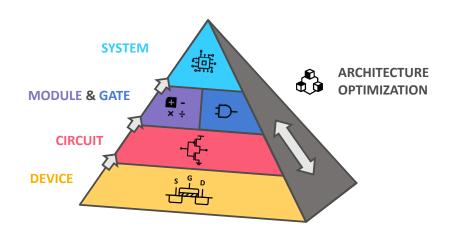

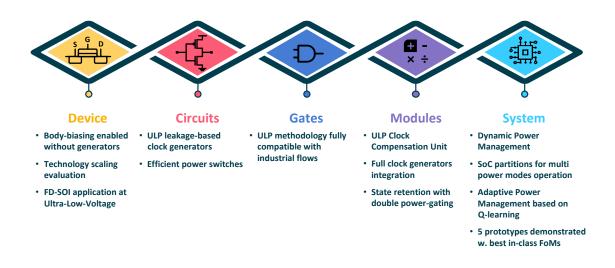

Une approche ascendante est abordée pour rechercher des techniques à tous les niveaux de conception afin d'optimiser l'efficacité énergétique et une diminution de la puissance consommée (voir Figure 2).

Figure 2: Pile d'implémentation d'un circuit intégré : de la technologie silicium au système.

Cette analyse de l'historique et de l'état de l'art nous éclaire sur le large éventail de solutions disponibles pour la réduction de la consommation d'énergie. Le fonctionnement à ultra-basse tension (*ultra-low-voltage*, ULV) appliqué à des technologies nanométriques n'est pas suffisant. En effet, l'efficacité énergétique doit aussi être optimisée jusqu'au niveau système, en tirant parti des interactions entre le matériel et le logiciel. De plus, pour permettre le déploiement industriel d'une architecture System-on-Chip (SoC) compatible avec les applications à faible consommation, certains critères ont été définis.

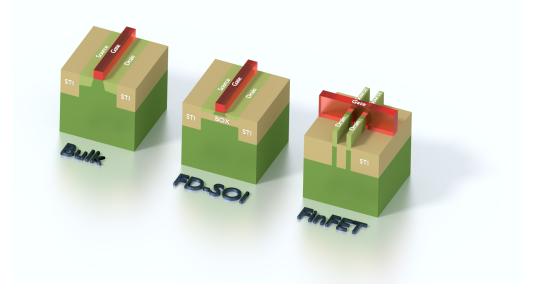

Premièrement, l'utilisation de la logique standard CMOS dans un nœud de technologie avancée comme le FD-SOI est nécessaire pour une efficacité en phase active maximale. L'ULV est également obligatoire pour atteindre le point d'énergie minimum du système (*Minimum Energy Point*, MEP). La sensibilité aux variations PVT qui en résulte doit être compensée par des méthodes simples ou en définissant des marges raisonnables.

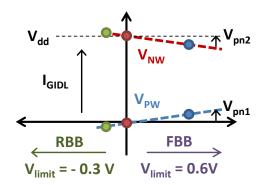

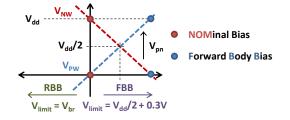

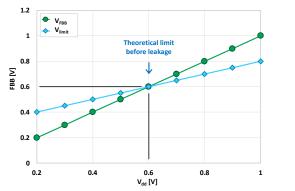

La polarisation des caissons (*body-biasing*) possible en FD-SOI offre un levier supplémentaire entre vitesse, efficacité et fiabilité et doit donc être envisagée. Cependant, pour des applications ULP, des solutions simplifiées doivent être développées pour ne pas impacter le budget énergétique du système. Bien que ce travail vise principalement des optimisations architecturales, une analyse complète des composants basse consommation constitutifs d'un SoC est nécessaire. Cela mène notamment à re-concevoir des composants pour les opérations ULV/ULP.

Un partitionnement du système est obligatoire pour implémenter des techniques basse consomation mais aussi intégrer efficacement des modules. De même, cela facilite des techniques à haut-niveau de gestion de puissance qui se basent sur les différents états de fonctionnement du SoC. Enfin, la gestion dynamique de la puissance (*Dynamic Power Management*, DPM) est une option prometteuse pour exploiter les modes d'alimentation du système en fonction de l'activité et de l'application.

#### Definition d'un Système Ultra-Basse Consommation

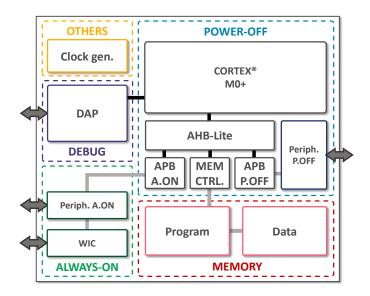

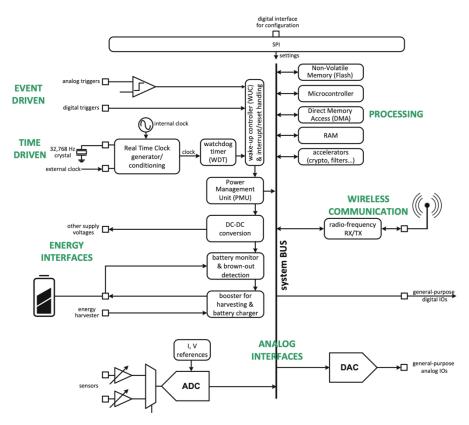

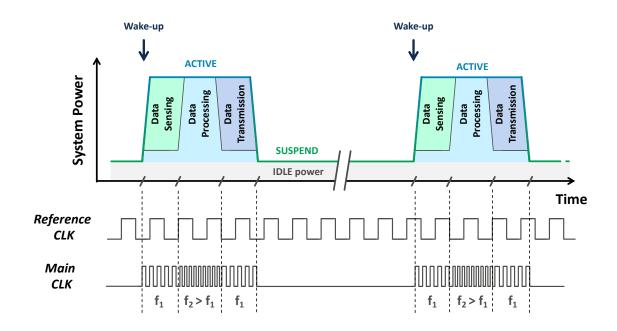

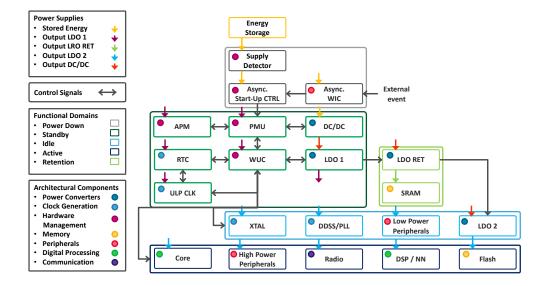

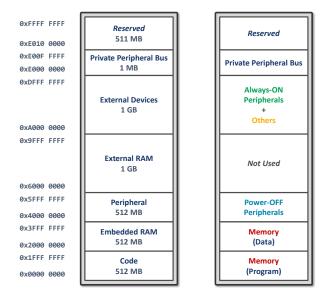

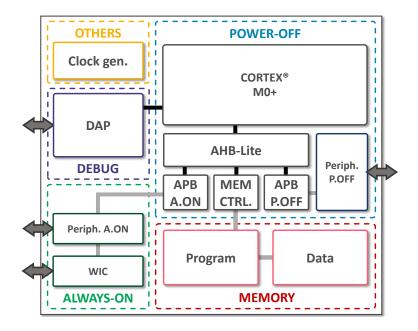

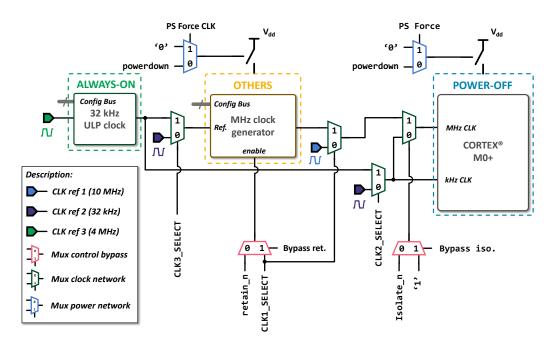

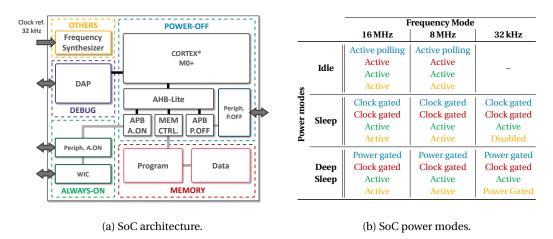

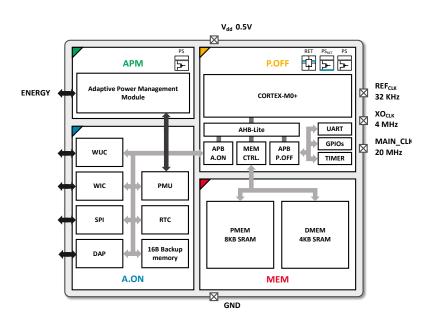

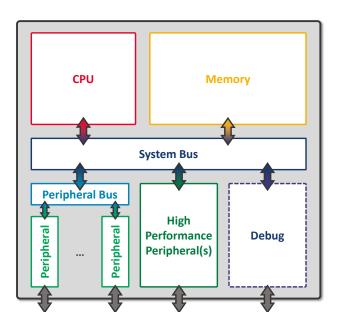

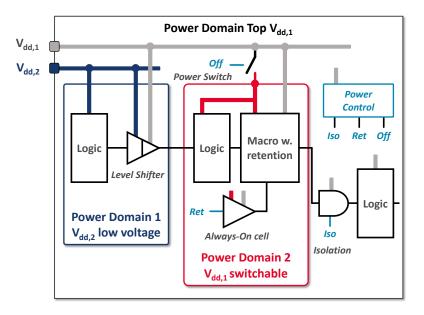

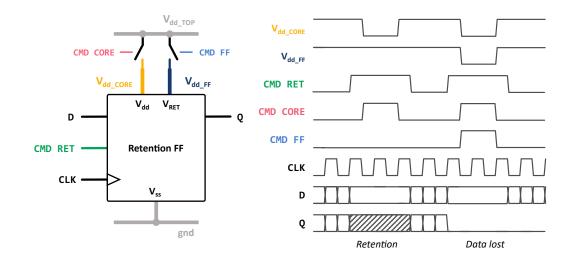

Une description fonctionnelle du SoC est proposée pour intégrer tous les sous-systèmes nécessaires à une architecture relativement générique. De plus, un partitionnement lors de l'implémentation permet la mise en place de modes liés à l'activité du système et de la disponibilité énergétique (voir Figure 3).

Comme tous les composants essentiels à un SoC ne peuvent être couverts dans ce travail, une mise en œuvre simplifiée est proposée pour démontrer les optimisations effectuées dans les chapitres suivants de ce travail. Ces améliorations se focalisent notamment sur l'intégration de la technologie, des composants et des systèmes basse consommation.

Figure 3: Partitionnement du système pour répondre à des applications Ultra-Low-Power.

#### Générateur d'Horloge Ultra-Basse Consommation

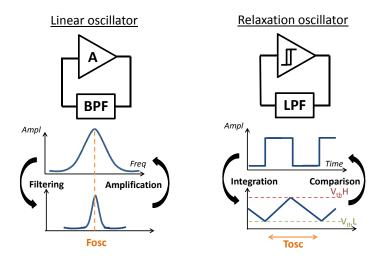

Pour assurer un fonctionnement correct, les systèmes de faible puissance nécessitent des sources de temps et de fréquence précises. De plus, afin de s'adapter aux budgets limités des applications ULP, des soins particuliers doivent être apportés à la réduction de la puissance globale, tout en améliorant la précision et la stabilité de l'horloge.

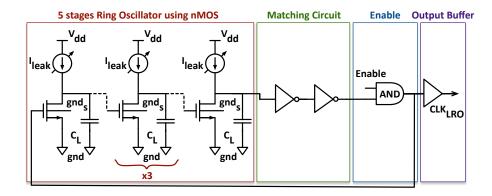

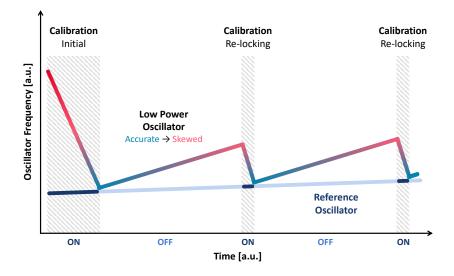

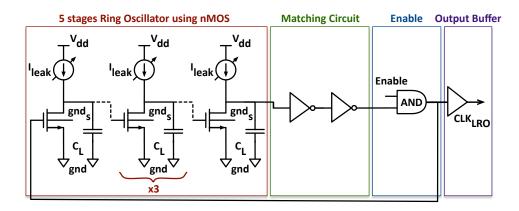

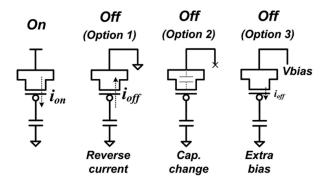

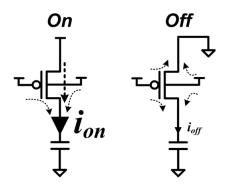

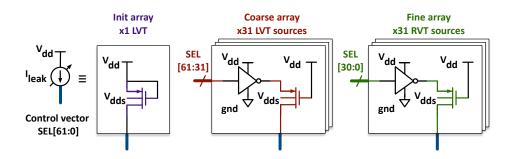

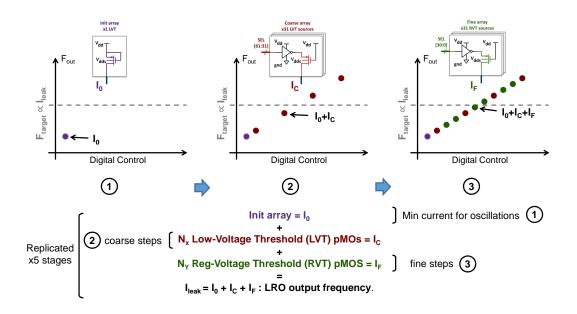

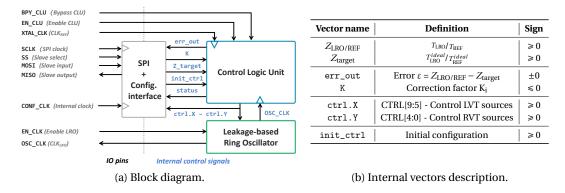

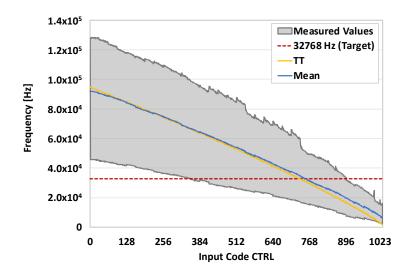

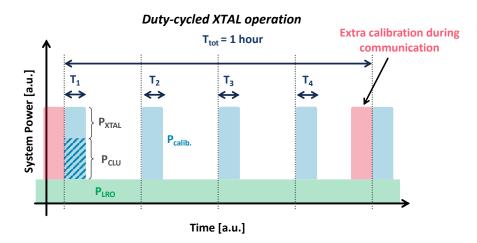

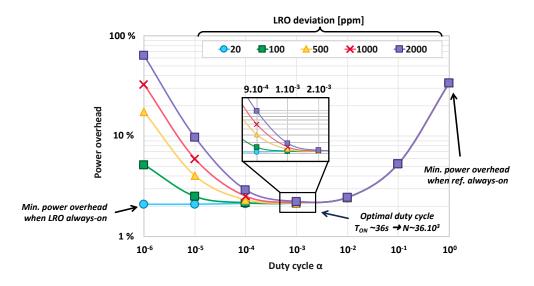

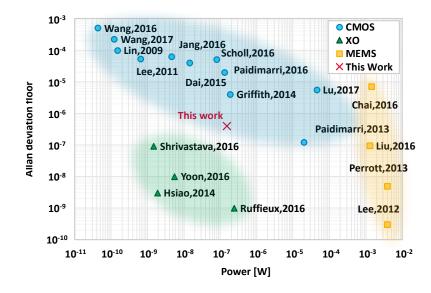

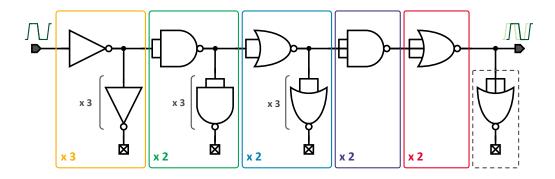

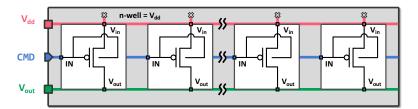

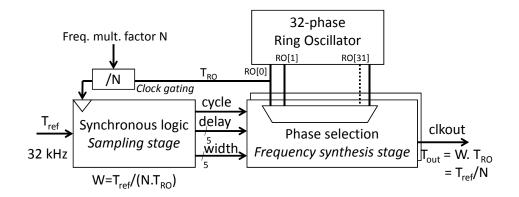

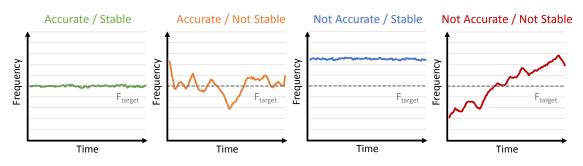

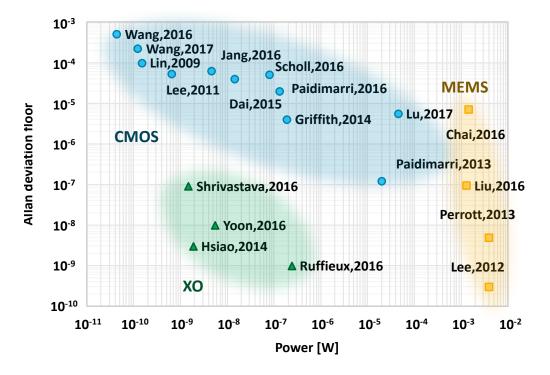

D'autre part, comme la référence de l'horloge reste active pendant la plupart des phases de fonctionnement du SoC, elle contribue de façon non-négligeable à la consommation totale du système. Ainsi, pour diminuer cet impact sans dégrader les performances, plusieurs solutions ont été explorées. Une solution compatible avec les technologie CMOS utilisant un oscillateur en anneau (*Ring-Oscillator*, RO) basé sur les courants de fuites apparaît comme le meilleur compromis en termes de puissance, de surface et de stabilité (voir Figure 4).

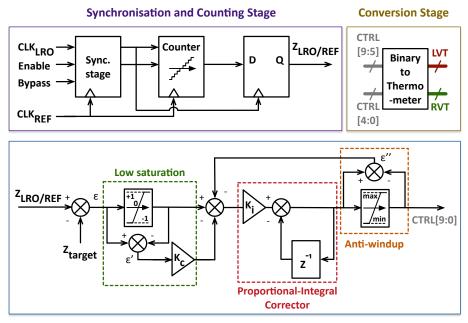

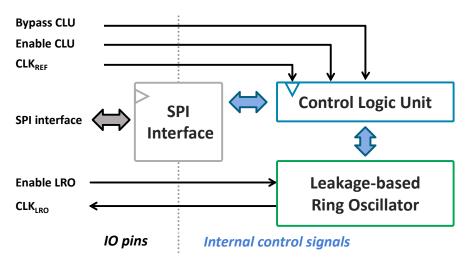

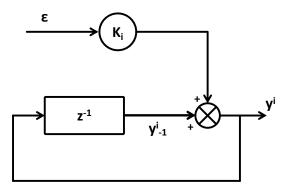

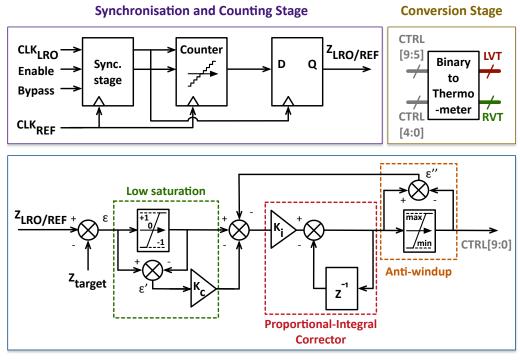

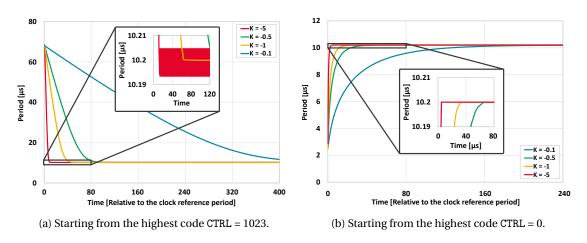

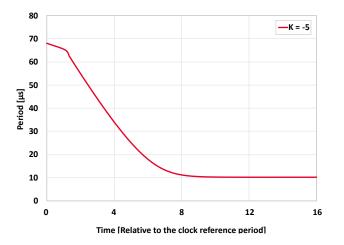

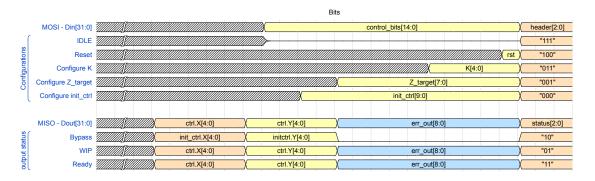

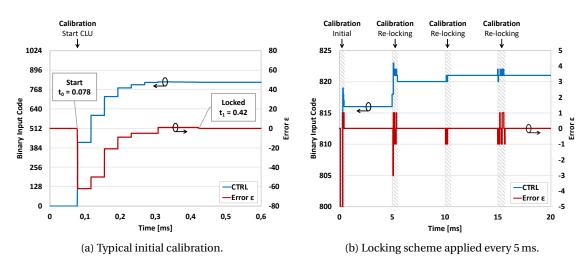

En raison de la haute sensibilité de l'oscillateur, une unité de compensation numérique nommée CLU pour *Control Logic Unit* est ajoutée. Construite autour d'un correcteur Proportionnel-Intégral (PI), elle intègre plusieurs optimisations pour une précision maximale avec un temps de convergence réduit (voir Figure 5).

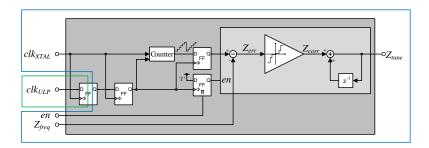

Figure 4: Schéma de l'oscillateur contrôlé en courant.

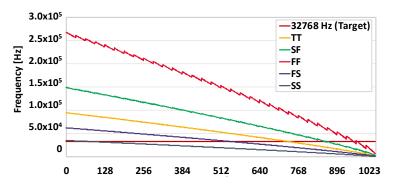

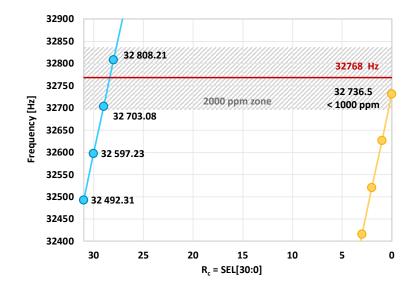

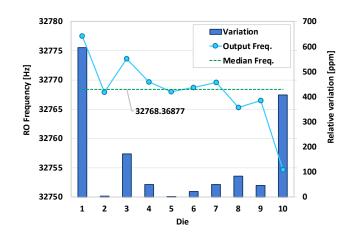

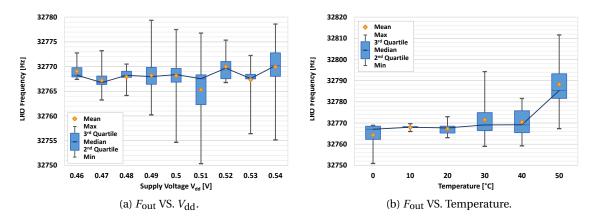

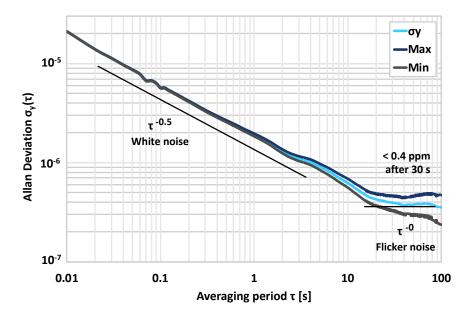

L'ensemble du système fonctionne à 0.5 V. Quarante-deux puces ont été testées et dix sélectionnées pour l'évaluation de la compensation numérique. Les résultats obtenus démontrent un système offrant un rendement énergétique élevé, combiné à de très faibles variations de tension et de température. Une consommation de 15 nW pour l'oscillateur et 125 nW pour la compensation est mesurée, tandis que le système assure une oscillation à 32.768 kHz avec 90 ppm/V pour  $V_{dd} \pm 8\%$  et 1.9 ppm/°C de 0 à 50 °C. Enfin, les capacités de stabilité à long terme sont caractérisées par une déviation d'Allan de 0.1 ppm. En faisant la démonstration d'une horloge efficace et peu coûteuse, ce travail offre une référence temporelle et une source polyvalente pour les systèmes numériques standards.

**Compensation Stage**

Figure 5: Schéma block de l'unité de compensation CLU.

#### Implémentation de Systèmes Ultra-Basse Consommation

L'approche technique de ce travail vise à démontrer la faisabilité d'un système efficace en énergie et adapté à l'énergie que peut collecter un récupérateur, tout en utilisant exclusivement les dernières directives ou outils industriels. Ainsi, les travaux présentés dans ce chapitre se distinguent des publications existantes par une approche reposant sur des méthodes simples mais très efficaces. En effet, afin de faciliter une adoption rapide des techniques basse consommation, le marché de masse des microcontrolleurs exige des solutions rentables et robustes.

Par conséquent, les anciennes techniques basse-consommation et les nouveaux concepts innovants sont explorés de la technologie jusqu'au niveau du système. Un SoC avec une consommation d'énergie active correspondant à une consommation de plusieurs centaines de micro watts est mise en œuvre grâce à l'utilisation de plusieurs techniques. Cela passe par une utilisation adéquate et un étalonnage des caractéristiques de la technologie, associés à un réglage spécifique du flot de conception. Dans un second temps, la sélection rigoureuse des composants et des techniques de faible consommation, l'optimisation de l'architecture système associée à un apprentissage des différents modes offerts par le Cortex-M0+ permettent de définir des modes de consommation pertinents.

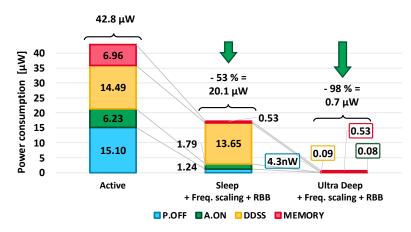

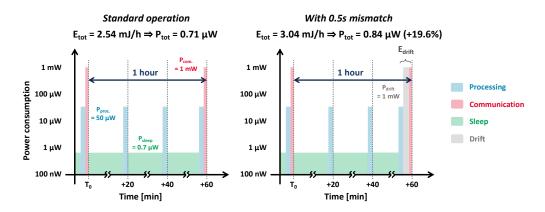

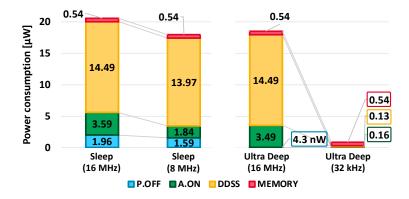

La consommation finale obtenue laisse également une marge dans l'ensemble du budget énergétique pour étendre le système avec des capacités de communication et de détection, ouvrant ainsi la voie à des systèmes totalement autonomes (voir Figure 6).

Figure 6: Répartition totale de la consommation du démonstrateur NZP28 – V1.0 à 0.5 V/25 °C.

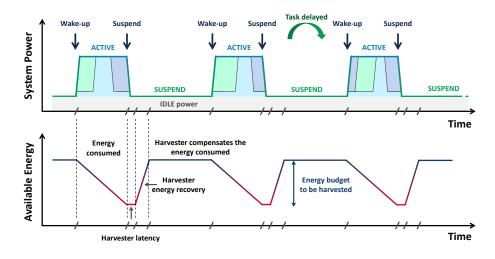

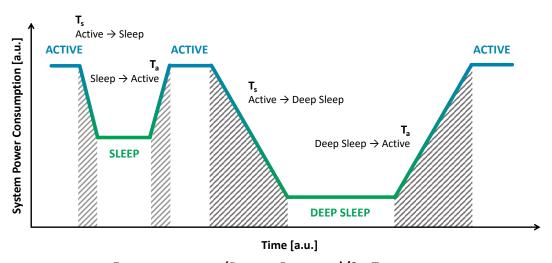

Cependant, les meilleurs modes ULP ne garantissent pas une consommation d'énergie efficace pendant toute l'activité du système. En raison de l'alternance entre les séquences actives et les séquences de repos, une gestion adaptative de la consommation est nécessaire pour une sélection optimale du mode du SoC en phase de repos. De plus, en raison des variations PVT, une caractérisation complète de la consommation électrique du système ne garantit pas la solution la plus favorable. Des efforts sont donc poursuivis pour mettre au point des techniques novatrices reposant sur l'apprentissage de l'activité du SoC.

#### Gestion Adaptative de la Consommation

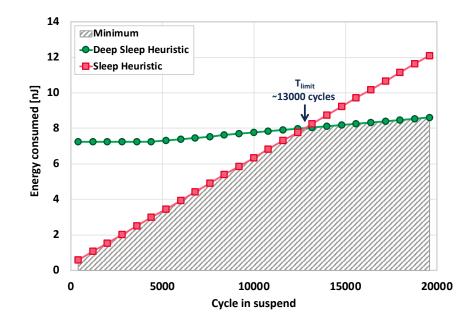

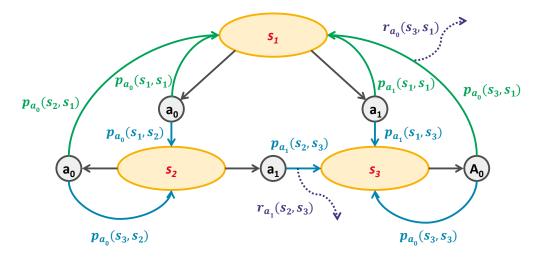

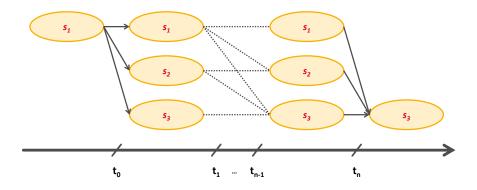

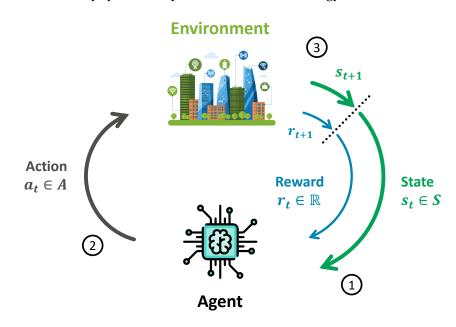

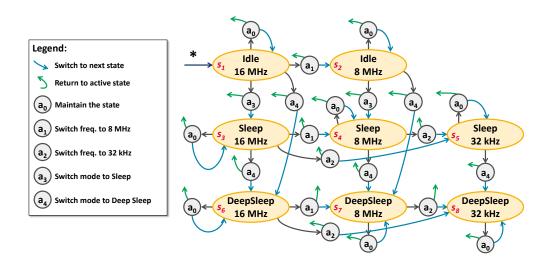

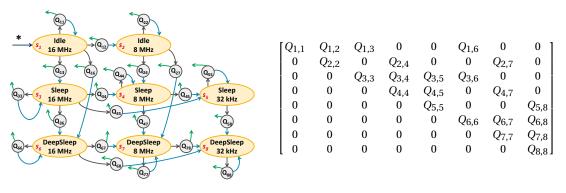

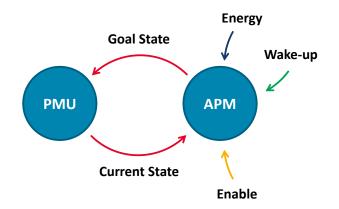

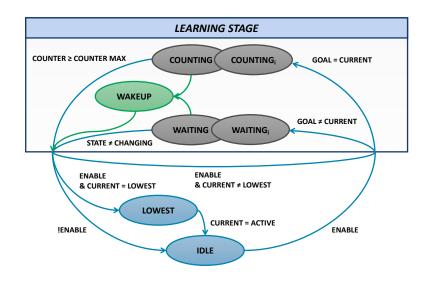

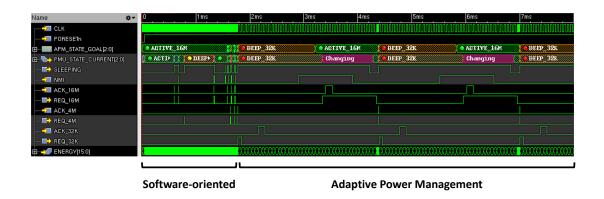

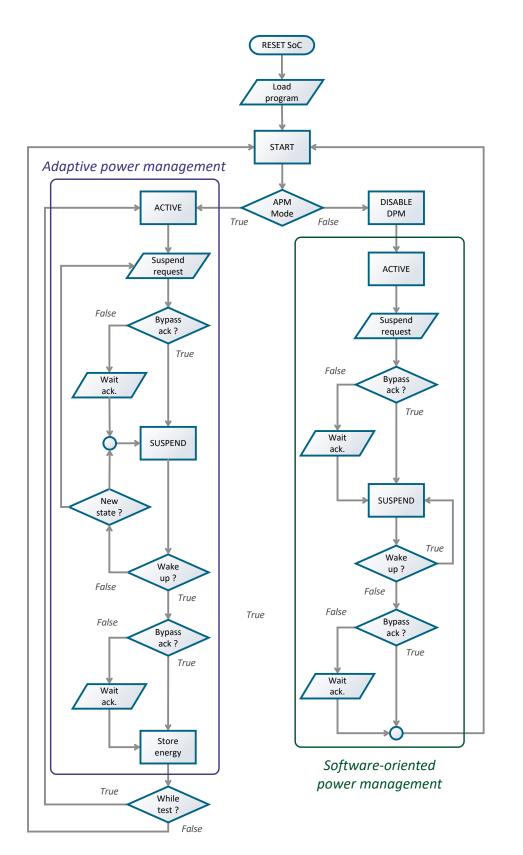

Ce chapitre présente un nouveau modèle de gestion adaptative de la consommation (*Adaptive Power Management*, APM) basé sur un algorithme d'apprentissage par renforcement (*Reinforcement Learning*, RL) pour optimiser la consommation du système relativement à son activité. Le module APM offre la possibilité de sélectionner le mode Ultra-Low-Power (ULP) le plus efficace en fonction du temps passé en phase de repos, de sa consommation d'énergie et de son environnement externe.

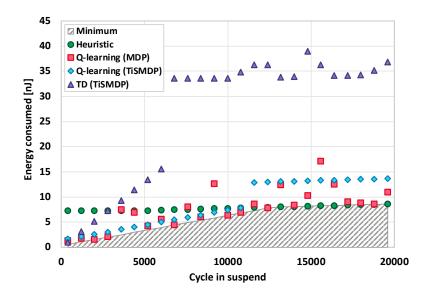

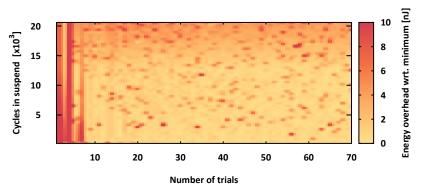

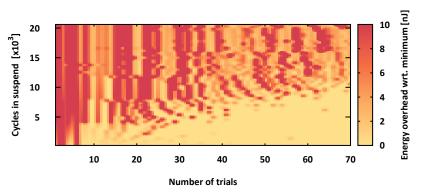

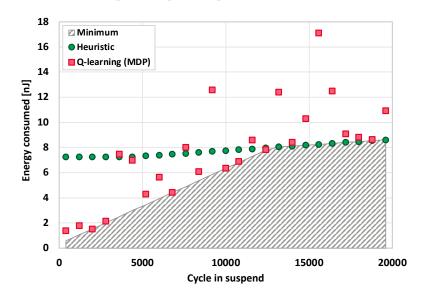

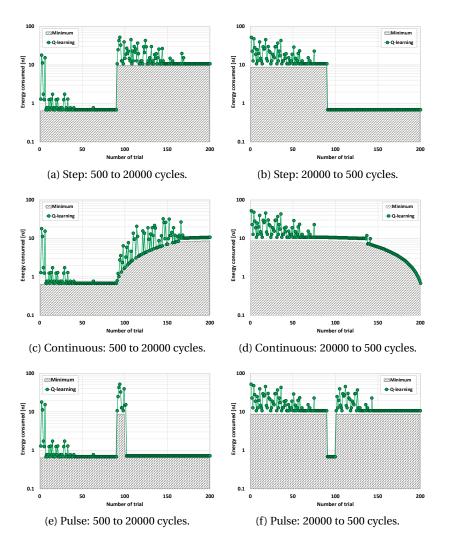

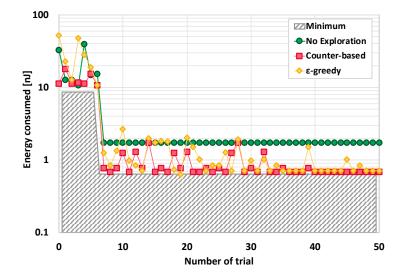

La théorie générale de l'algorithme est définie sur une architecture générique. Cette analyse préliminaire permet de définir correctement les paramètres pour maximiser l'apprentissage par renforcement. Finalement, l'algorithme *Q-Learning* (QL) est sélectionné. Sur cette première architecture, les simulations démontrent un gain moyen de 17% comparé à une solution heuristique. Cependant, un temps d'apprentissage de 10 essais est requis, correspondant à un coût d'apprentissage de 87 nJ.

Le module APM a été synthétisé en technologie 28 nm FD-SOI. Au vu de l'impact de ce module générique sur un SoC basse consomation, des optimisations matérielles spécifiques ont été identifiées pour améliorer la consommation d'énergie du module.

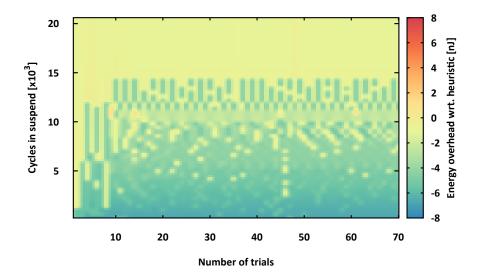

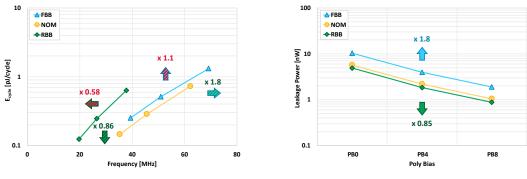

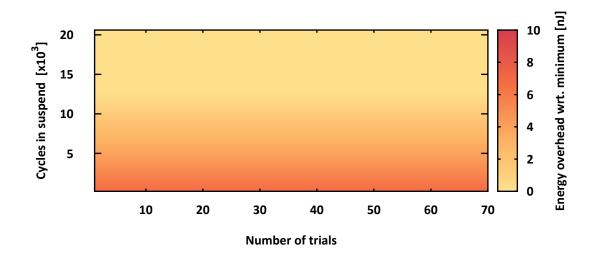

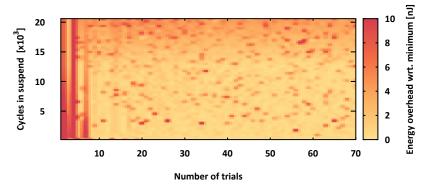

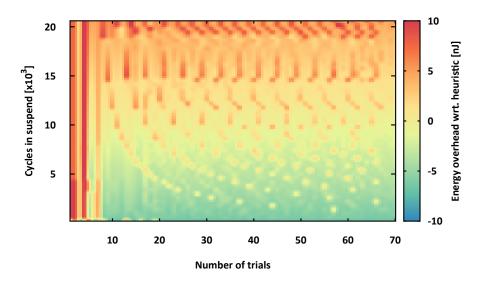

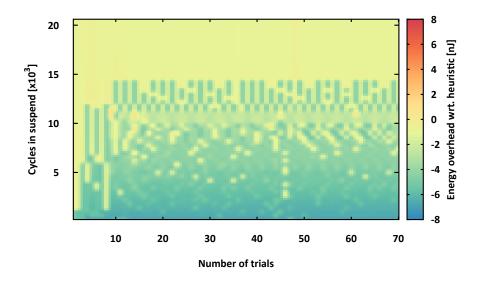

Ainsi, une seconde version du module APM est évaluée sur une architecture de type *Near-Zero-Power* (NZP). Grâce à la réduction du nombre d'états du système, de meilleures performances sont obtenues. Moins de 5 essais sont requis par l'algorithme pour faire son apprentissage, ce qui aboutit à un coût de 75 nJ. Par rapport à une heuristique de sommeil profond, on obtient des économies d'énergie de 150 % (voir Figure 7). De plus, l'impact de l'APM est estimé à 42% de l'architecture SoC. Ainsi, les bons résultats montrés par la technique restent mitigés pour de minuscules ULP SoCs. Cependant, la technique ouvre la voie à une gestion efficace de l'énergie à l'aide de techniques d'apprentissage machine.

Figure 7: Comparaison des gains et coûts énergétiques du module APM (architecture de type NZP) relativement à une solution heuristique. L'énergie consommée [nJ] est donnée en fonction du nombre de tests (*trials*) et du nombre de cycles (*cycle in suspend*) passés en mode repos.

L'ensemble du système est simulé et évalué à l'aide d'un environnement de cosimulation Python et Verilog. Combiné à des techniques de code évolutives, le module APM peut être adapté à plusieurs architectures de SoC. L'implémentation physique du module utilise aussi les techniques ULP présentées dans le chapitre précédent pour assurer une consommation minimale. Un démonstrateur complet de SoC intégrant le module APM est en cours de fabrication en technologie 22 nm FD-SOI. Les travaux futurs se concentreront sur la mesure de la performance in situ du module, y compris l'impact du module sur la consommation globale. Ce travail est le premier à implémenter Q-Learning (QL) dans un démonstrateur complet SoC pour une sélection optimale du mode de puissance pendant les séquences de suspension.

#### **Conclusions et Perspectives**

Cette thèse aborde un problème qui dépasse les solutions dédiées aux objets connectés actuels. Afin de garantir une utilisation viable à long terme des systèmes électroniques, l'émergence d'appareils connectés entièrement autonomes et durables est nécessaire. Ainsi, ce travail développe des circuits et systèmes-sur-puce présentant une empreinte énergétique réduite au maximum.

Pour les applications qui dépendent de la récupération d'énergie ou de petites batteries, l'efficacité énergétique est une mesure clé. Contrairement aux dispositifs IoT standards, qui offrent des services à faible et haute performance, en tirant parti d'une réserve d'énergie macroscopique offerte par leur batterie, les systèmes NZP effectuent des opérations très spécifiques à faible coût énergétique tout en consommant peu ou pas d'énergie quand ils sont en mode veille. Ce travail met également un accent particulier sur la réduction de la consommation d'énergie des microcontrôleurs génériques en utilisant la technologie FD-SOI combinée avec les derniers flots standards de conception et outils industriels.

L'empreinte énergétique quasi nulle permettra non seulement des applications de faible activité, comme des capteurs sans fils qui analysent les variations physiques et chimiques de l'environnement ou qui surveillent la santé, mais aussi la robotique en essaim et les applications à distance. Pour de tels systèmes, la petite source d'énergie embarquée, souvent associée a des récupérateurs d'énergie, présente des dimensions minimales et une énergie disponible réduite. Ces limitations nécessitent des innovations à tous les niveaux de conception d'un circuit intégré conventionnel - dispositif, circuits, portes/modules, système et architecture - et cela, afin de fournir un service pertinent tout en garantissant l'autonomie énergétique du système.

La faisabilité d'un SoC ULP est donc démontrée par l'utilisation de plusieurs techniques. Cela débute par l'utilisation du catalogue industriel de cellules standards et des caractéristiques de la technologie FD-SOI. Un partitionnement du système est également proposé et combiné à l'utilisation de solutions optimisées pour la faible consommation ainsi que des techniques d'apprentissage machine pour permettre de minimiser la consommation du système.

### Acknowledgment

As you might guess, carrying out a Ph.D. research project is a challenging task, especially when it comes to high-end technological topics such as microelectronics. Luckily, during three years of academic and industrial partnership between STMicroelectronics and Aix-Marseille Université I had the chance to meet outstanding people who filled my boundless curiosity, enriched my knowledge and supported my ideas. A few pages are definitely not enough to acknowledge what they have done but I will try to keep it short.

First, I would like to give infinite thanks to my industrial supervisor Fady Abouzeid. As far as I am concerned, he is THE most awesome supervisor a Ph.D. student might dream of. Sometimes using "forced autonomy", I had to learn a lot in a short amount of time, but in the end he was always there even at silly hours to do last-minute design fixes, paper reviews or simply discuss some ideas or technical aspects of electronic design. Thank you for always supporting me. I also warmly show my appreciation to my academic supervisor Prof. Jean-Luc Autran for his academic guidance all along this project. Thank you also for giving me the means to promote my work and present it in world-class conferences. I also wish you the best to finally solve the Phaistos disc mystery.

My gratitude also goes to the people who accepted to be part of my thesis examination committee and for their valuable feedback and insightful questions: Prof. David Bol and Prof. Masimo Alioto, Édith Beigné, Pascal Vivet and James Myers.

Many thanks to Philippe Roche, the manager of the radiation hardening and ultra-lowvoltage team at STMicroelectronics, who kindly welcomed me in this group. You gave me plenty of freedom and silicon opportunities to express my ideas. As a young designer eager to play with advanced technology nodes, I could not thank you enough for that. Moreover, your wise managing and technical advice also offered to my work credibility and visibility.

There are two people I consider as my "shadow" supervisors for their technical support and friendly discussions. Thank you Jean-Marc Daveau. Despite the years that separate us, I found an authentic nerd friend and sciences enthusiast. With you I could share my obscure computer and electronic related discoveries. Also bless you for the retard alerts. Take care of the triangle: Diling J Diling J. Thank you Martin Cochet. As a former student of my master degree you contacted me to let me know about a research opportunity which resulted in this Ph.D. thesis. This manuscript would not exist without you. Thanks for all the debates about electronics, the silly imperial units, the Tomazou transistor humpf principle, PhD comics. You are a great source of inspiration and some of my best ideas come from our discussions.

My fellow Ph.D. students are also a great source of wise (and sometimes silly) discussions. Victor Malherbe (OK technically you are not a Ph.D. student anymore) many thanks for the discussions around the understanding of the transistor behavior. Now, I get it, "It's only a model". I am also glad I could share my thesis writing complaints with you. Next, thank you Capucine Lecat–Mathieu de Boissac my fellow office companion. Since I don't have the space to write you the full acknowledgement page you deserve, I will principally thanking you for being my rubber duck debugging companion and comprehensive listener to all my thesis existential troubles. Finally, Sebastien Thomet, it was so nice having all these hacking discussions during our long biking commutes. Both of you, I wish you the best for the ending of your PhD.

I would like to extend my thanks to all my team member at STMicroelectronics. Thank you Dominic Zamora, for helping me when I was struggling with design tools. Thank you Dimitry Soussan, since you are a kind and friendly co-worker I wish you the best but I won't forget the painful gym sessions. Thank you Thomas Théry, even though I am still waiting for the 3D Tron game. Thank you Olivia Riewer for you precious advice on mastering SDC constraining. Thank you Vincent Lorquet, as a software enthusiast I am sure you will impose GIT to the team. Thank you Valérie Bertin for your software precious tips. Thank you Serge De Paoli, master of the digital debug. Thank you Anna Asquini and Calogéro Timineri, as digital designers who know the product experience, it was always nice exchanging with you. Lastly, thank you Gilles Gasiot, the Alpha and Omega of radiation hardening. I could not forget the interns and students who reminded me about my engineering school years. Thank you Patrick Temleitner, Mathieu Rodrigues, Florent Chartier, Mael Baudoin, Quentin Metras and Romain Demarets. A special thank to Yvan Debizet with whom I worked on Adaptive Power Management.

Thank you Soilihi Moindjie and Jeff Novakowski for your support during experimentation and testchips measurements. Thank you Gaelle Passeron for the Cadence Support during stressful tape-out deadlines. Thank you Sylvain Clerc and Thierry Di Gilio. With you guys I had the best conversation on body-bias utilization and FD-SOI ever. A special thanks to Ricardo Gomez–Gomez to whom I wish the best for his PhD. You did such a great work and talking with you was always so delighful. Thank you Andrej Suller for sharing the ST Ph.D. experience during our long Express 1 bus commutes. Thank you Andrea Cathelin for your support on the after PhD thesis life. Thanks also to Robin Bennarouch for the visit of BWRC and the explanations of RF-design. Moreover, I really appreciate the always available administrative and logistic support of Pascale Maillet-Contoz at ST and Zolika Djellouli at Aix-Marseille.

In addition, many thanks to all other amazing people, Hans and other KUL students, Maxence and CEA members, Pranay and others, I have met during conferences and events all over the world for all the insightful discussions we had (often around a beer or two...). I also want to thank my friend Yannick, for his Sunday PlayStation support to climb the Rocket League ladder. Thank you Nicolas and Chloé for welcoming me when I returned back to Paris. And lastly, thank you to all my friends from Saint-Louis, Télécom Paris and Imperial College for supporting me during these years in spite of the distance.

Pour finir, je voudrais également profiter de cette occasion pour remercier (en français) les membres de ma famille. Ma sœur Léonie, pour son aide lors de la rédaction de ce manuscript. J'ai également une pensée toute spéciale pour mon grand-père Jean qui était typographe. Tout comme tu pouvais ordonner des charactères d'imprimerie, j'organise des transistors pour "imprimer" des circuits. Par-dessus tout, je remercie chaleureusement mes parents pour leurs encouragements continus et leur soutien logistique. Ces trois dernières années n'auraient pas été possibles sans leurs dévouements continus. Ce travail vous est dédié !

Guénolé.

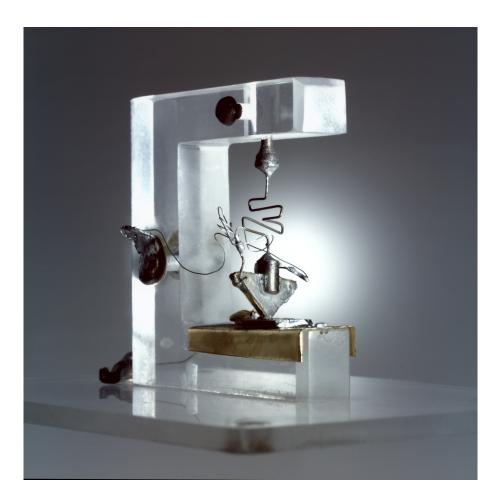

Figure 8: Picture of the first transistor ever assembled at Bell Labs in 1947.

### Preface

DECEMBER 23<sup>th</sup> 1947, three scientists – John Bardeen, William Shockley, and Walter Brattain – present the progress of their semiconductor researches to the higher-ups of the Bell Labs, New Jersey (USA). As detailed in Brattain's lab notes, a microphone and a headphone are connected to a PNP point-contact germanium device which operate as a speech amplifier "with no noticeable change in quality" [7]. A new keystone component of modern electronics is operating for the first time; the transistor is born.

Immediately convinced that a fundamental breakthrough had just occurred, an absolute secret is imposed, and the results disclosed to a limited number of collaborators. Fearing that other scientists could develop similar devices, patents are systematically filed. However, on June 30<sup>th</sup>, 1948, after having publicly announced their discovery, Bell Labs adopted a free policy of openness to avoid a military secret classification of their research. From there, the development of the transistor technology would be facilitated and stimulated by co-developments, communications, and conferences with other academic, industrial and military institutions. Less than 10 years later, the three scientists were honored "for their researches on semiconductors and their discovery of the transistor" with the 1956 Nobel Prize in Physics [8].

Nowadays, thanks to the progress of technology, the transistor is widely available and used in people's life. From the personal computer to the CMOS based DNA sequencer, this component is integrated everywhere in electronic devices, yet its applications in more and more complex circuits have become a major issue. The following of Moore's law [9] is declining and Dennard's scaling [10] limited by a slowdown of the supply voltage reduction, hence putting into jeopardy the improvement of transistor integration and performances.

Popular solutions for modern embedded applications integrate more and more components into Solid-State platforms, known as System-on-Chip. Those actual systems' power consumptions are limited in the milliwatt range, hardly sustaining lifetime operations. For perpetual operations, designers and manufacturers cannot rely on existing technology offers. Innovative design and Ultra-Low-Power solutions must be developed by taking challenges in the design of digital and analog circuits, systems and architectures for compact Internet-of-Things devices.

This current status sets the beginning of this research project. Seventy years after the prior discovery, now supplemented by thousands of contributions from researchers and engineers, this work humbly pursues the quest towards the significant reduction of electronic devices energy consumption. After reading this manuscript, I hope it will give plenty of ideas to others. Maybe one day, we will finally create the perpetual electronic machine.

## Contents

| Abstra  | act                                                |   | iii   |

|---------|----------------------------------------------------|---|-------|

| Résum   | né en français                                     |   | vii   |

| Acknow  | owledgment                                         |   | xvii  |

| Prefac  | xe                                                 |   | xxi   |

| Conter  | nts                                                |   | xxiii |

| List of | Figures                                            |   | xxix  |

| List of | Tables                                             |   | xxxv  |

| Abbrev  | viations                                           | x | xxvii |

| Introd  | luction                                            |   | 1     |

| Nev     | w Paradigms of Computer Hardware                   |   | 1     |

| Aut     | tonomy and Power Constraints for IoT Systems       |   | 4     |

| Pow     | wer Scaling                                        |   | 5     |

| Tow     | wards Near-Zero Power                              |   | 7     |

| Cha     | allenges                                           |   | 8     |

| The     | esis Outline                                       |   | 10    |

| Chapte  | er 1. Background                                   |   | 13    |

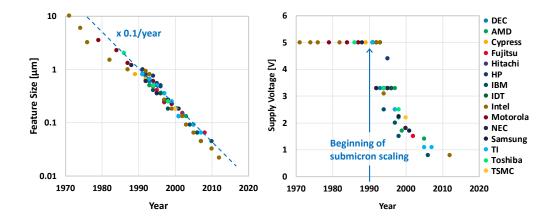

| 1.1     | Brief History of Voltage Scaling                   |   | 14    |

| 1.2     | Technology for Energy-efficient Design             |   | 16    |

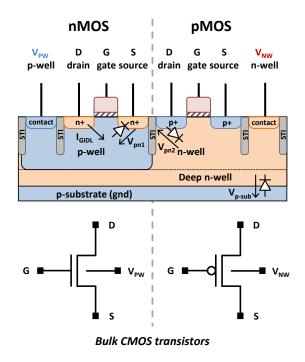

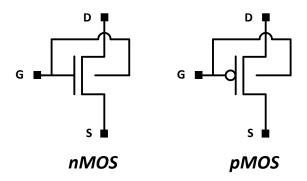

|         | 1.2.1 The MOSFET Transistor in CMOS Technology     |   | 16    |

|         | 1.2.2 Advanced Technologies for Nanometers Designs |   | 21    |

|         | 1.2.3 FD-SOI for Minimized Energy Consumption      |   | 22    |

| 1.3     | Energy-efficient Circuits                          |   | 24    |

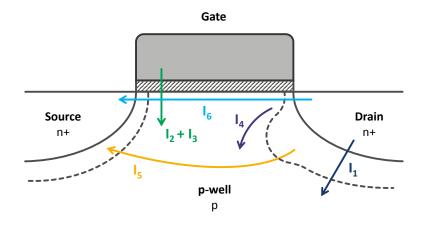

|         | 1.3.1 Circuit Topologies                           |   | 24    |

|        | 1.3.2          | Sources of Power Dissipation in CMOS Circuits                                  | 26         |

|--------|----------------|--------------------------------------------------------------------------------|------------|

|        | 1.3.3          | Minimum Energy Point                                                           | 28         |

|        | 1.3.4          | Circuit Techniques for Power Reductions                                        | 30         |

| 1.4    | Gate-          | level Building Blocks and Modules for Low-Power Operations                     | 32         |

|        | 1.4.1          | Design Constraints for Low-Voltage Operations                                  | 32         |

|        | 1.4.2          | Power Management Techniques                                                    | 33         |

| 1.5    | Syster         | m and Architectural Design                                                     | 36         |

|        | 1.5.1          | Total Energy Consumption                                                       | 36         |

|        | 1.5.2          | System Level Power Optimizations                                               | 38         |

| 1.6    | Sumn           | nary                                                                           | 42         |

|        | 1.6.1          | Review of Ultra-Low-Power Techniques                                           | 42         |

|        | 1.6.2          | Existing SoC Implementations                                                   | 43         |

|        | 1.6.3          | Conclusion                                                                     | 44         |

| Chante | ar? I          | Iltra-Low-Power System Definition                                              | 49         |

| 2.1    |                | Low-Power System-on-Chip Architecture                                          | <b>4</b> 5 |

| 2.1    | 2.1.1          | IoT Device Energy Flow                                                         | 50<br>50   |

|        | 2.1.1          | System and Processing Elements                                                 | 50<br>51   |

|        | 2.1.2          | Clock Generation and Time Keeping                                              | 52         |

|        | 2.1.3          | Use Cases Scenarios                                                            | 53         |

|        | 2.1.4          | Resulting Design Considerations                                                | 56         |

| 2.2    |                | Low-Power System-on-Chip Functional Description                                | 56         |

| 2.2    | 2.2.1          | SoC Description                                                                | 56         |

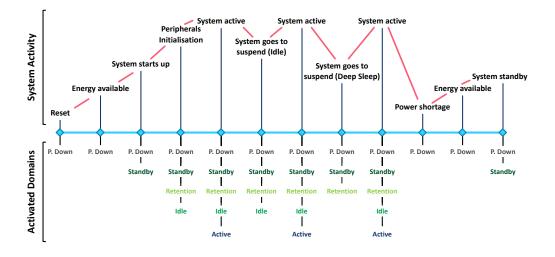

|        | 2.2.1          | Activity Timeline                                                              | 50<br>57   |

|        | 2.2.2          | Derivation of Power Modes                                                      | 58         |

| 2.3    |                | Low-Power System-on-Chip Implementation                                        | 50<br>59   |

| 2.3    |                |                                                                                | 59<br>59   |

|        | 2.3.1<br>2.3.2 | System Partition                                                               | 59<br>59   |

|        | 2.3.2          | Resulting Memory Mapping     Adopted Ultra Low Power Demonstrator Architecture |            |

| 2.4    |                | Adopted Ultra-Low-Power Demonstrator Architecture         usions               | 60         |

| 2.4    | Conci          |                                                                                | 61         |

| Chapte | er 3. C        | Clock Reference for Ultra-Low-Power Systems                                    | 63         |

| 3.1    | Ultra-         | Low Power Clock in IoT nodes                                                   | 64         |

|        | 3.1.1          | Design considerations: Power, Area and Stability                               | 64         |

|        | 3.1.2          | Evaluation of Existing Low Power Time References and Clock Sources             | 64         |

|        | 3.1.3          | Design Targets and Use Case                                                    | 67         |

|        | 3.1.4          | System Architecture                                                            | 68         |

| 3.2    | Clock                            | Generation using a CMOS-compatible Oscillator                                                                      | 69                |

|--------|----------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|

|        | 3.2.1                            | Existing Solutions                                                                                                 | 69                |

|        | 3.2.2                            | CMOS Current Controlled Ring Oscillator                                                                            | 70                |

|        | 3.2.3                            | Current Sources Sizing: Process Variations Compensation                                                            | 73                |

|        | 3.2.4                            | Leakage Sources Matching and Variability                                                                           | 75                |

|        | 3.2.5                            | Complete Physical Implementation                                                                                   | 78                |

| 3.3    | Digital                          | Locking Scheme                                                                                                     | 79                |

|        | 3.3.1                            | Evaluation of Various Digital Compensations                                                                        | 79                |

|        | 3.3.2                            | Proportional-Integral Corrector Analysis and Optimizations                                                         | 82                |

|        | 3.3.3                            | SPI Interface and Controls                                                                                         | 84                |

| 3.4    | Circuit                          | t Implementation and Measurements                                                                                  | 86                |

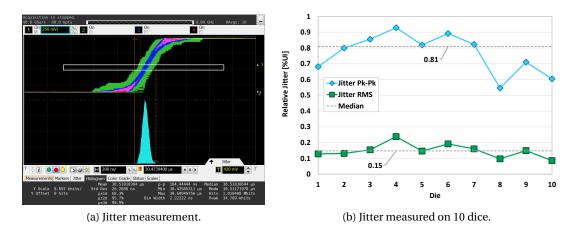

|        | 3.4.1                            | LRO Free Oscillations and Jitter                                                                                   | 86                |

|        | 3.4.2                            | Digital Compensation Evaluation                                                                                    | 87                |

|        | 3.4.3                            | Power and Drift Trade-off Resulting from the Relocking Scheme                                                      | 90                |

|        | 3.4.4                            | Comparison with the State of the Art                                                                               | 93                |

| 3.5    | Summ                             | ary                                                                                                                | 94                |

| Chante |                                  | ltra-Low-Power System Implementation                                                                               | 97                |

| -      |                                  | Low-Power Design Methodology in FD-SOI                                                                             |                   |

| 4.1    |                                  |                                                                                                                    | 98<br>08          |

|        |                                  | Minimum Energy Point Design Methodology          Transistor Features Selection                                     | 98<br>08          |

|        |                                  | Clock Tree and Standard Cell Selections                                                                            | 98<br>104         |

|        |                                  |                                                                                                                    |                   |

| 4.2    |                                  | Electronic Design Automation Flow Tuning       Power Reduction                                                     | 104               |

| 4.2    |                                  |                                                                                                                    | 105               |

|        |                                  | Power Gating                                                                                                       | 105               |

| 4.3    |                                  | State Retention with Double Power Gating                                                                           | 110               |

| 4.5    | •                                |                                                                                                                    | 113               |

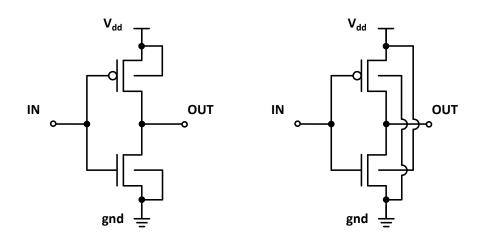

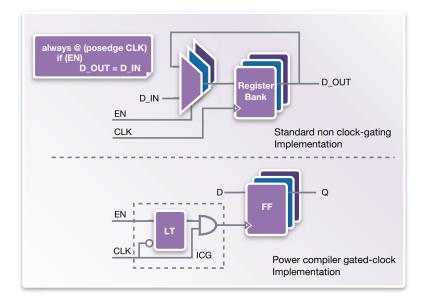

|        | 4.3.1                            | Dynamic Power Management       Clock Gating and Frequency Scaling                                                  | 117               |

|        | 4.3.3                            | Ultra-Low Voltage Memories                                                                                         | 117               |

| 4.4    |                                  | Ultra-Low Voltage Memories                                                                                         |                   |

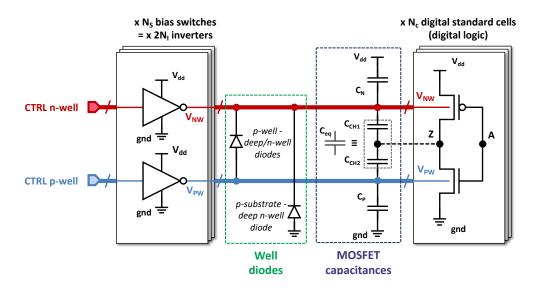

| 4.4    |                                  | Low Voltage Dynamic Rody Pissing                                                                                   | 121               |

|        |                                  | Low-Voltage Dynamic Body Biasing                                                                                   | 121<br>121        |

|        | 4.4.1                            | Concept of Back-Biasing at Ultra-Low-Voltage                                                                       | 121               |

|        | 4.4.1<br>4.4.2                   | Concept of Back-Biasing at Ultra-Low-Voltage                                                                       | 121<br>123        |

|        | 4.4.1<br>4.4.2<br>4.4.3          | Concept of Back-Biasing at Ultra-Low-Voltage         Evaluation in 28 nm FD-SOI         Evaluation in 22 nm FD-SOI | 121<br>123<br>126 |

| 4.5    | 4.4.1<br>4.4.2<br>4.4.3<br>4.4.4 | Concept of Back-Biasing at Ultra-Low-Voltage                                                                       | 121<br>123        |

|        | 4.5.1   | Testchips Realizations                                   | 134 |

|--------|---------|----------------------------------------------------------|-----|

|        | 4.5.2   | Power Consumption Evaluation                             | 138 |

|        | 4.5.3   | Impact of State Retention Power Gating                   | 143 |

|        | 4.5.4   | Technology Scaling Evaluation                            | 145 |

|        | 4.5.5   | Utilization of Self-Body Bias                            | 146 |

|        | 4.5.6   | Towards Adaptive Power Management                        | 150 |

| 4.6    | Sumn    | nary of Performances and Conclusions                     | 152 |

|        | 4.6.1   | Summary of Performances                                  | 152 |

|        | 4.6.2   | Conclusions                                              | 153 |

| Chapte | er 5. A | daptive Power Management                                 | 157 |

| 5.1    | Activi  | ty-oriented Power Management                             | 158 |

|        | 5.1.1   | Problem Statement                                        | 158 |

|        | 5.1.2   | Existing Solutions                                       | 158 |

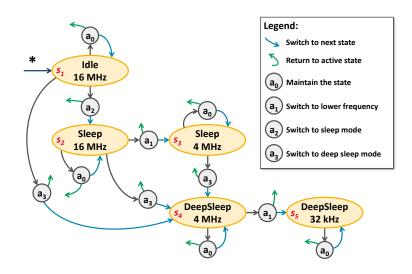

|        | 5.1.3   | System Definition                                        | 159 |

|        | 5.1.4   | System Representation                                    | 163 |

|        | 5.1.5   | Reinforcement-Learning through Q-learning                | 164 |

|        | 5.1.6   | Application on an ULP SoC                                | 167 |

| 5.2    | Gene    | ric SoC Application                                      | 172 |

|        | 5.2.1   | Simulation Environment and Methodology                   | 172 |

|        | 5.2.2   | Benchmarking of Several Reinforcement-Learning Solutions | 173 |

|        | 5.2.3   | Algorithm Robustness and Validations                     | 175 |

|        | 5.2.4   | Algorithm Optimizations                                  | 177 |

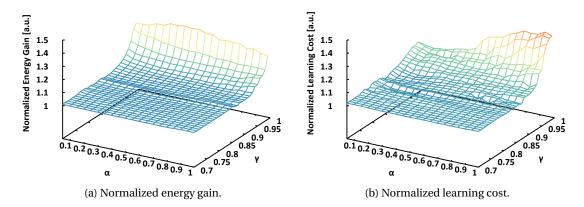

|        | 5.2.5   | Selection of Q-learning Coefficients                     | 180 |

|        | 5.2.6   | Partial Conclusions                                      | 181 |

| 5.3    | Appli   | cation to the NZP SoC                                    | 184 |

|        | 5.3.1   | Architecture Optimizations                               | 184 |

|        | 5.3.2   | Simulated Performances                                   | 185 |

|        | 5.3.3   | Area and Power Evaluation                                | 186 |

| 5.4    | APM     | Hardware Description and SoC Implementation              | 188 |

|        | 5.4.1   | APM Design                                               | 188 |

|        | 5.4.2   | Integration into an ARM Cortex-M0+ Based Architecture    | 193 |

|        | 5.4.3   | SoC physical implementation                              | 195 |

| 5.5    | Meas    | ured Performances                                        | 196 |

|        | 5.5.1   | Functional Validation                                    | 196 |

| 5.6    | Sumn    | nary and Perspectives                                    | 199 |

| Conclusion                                                                | 201     |  |

|---------------------------------------------------------------------------|---------|--|

| Appendix A. ARM Cortex-M0+ Presentation                                   | 209     |  |

| A.1 Reminders on Microprocessor Architectures                             | 209     |  |

| A.2 ARM Cortex–M0+ Presentation                                           | 211     |  |

| Appendix B. Introduction to the Allan deviation                           | 217     |  |

| B.1 Stability and Accuracy                                                | 217     |  |

| B.2 Frequency Stability Characterization                                  | 218     |  |

| B.3 State of the Art Analysis                                             | 219     |  |

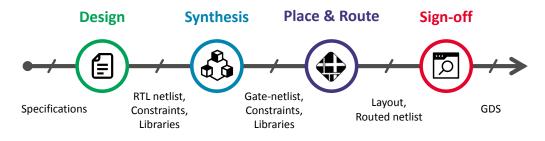

| Appendix C. Electronic Design Automation Flow                             | 221     |  |

| C.1 Synthesis, Place-and-Route, Sign-Off                                  | 221     |  |

| C.2 Unified Power Format                                                  | 223     |  |

| C.3 Simulations and Validation                                            | 224     |  |

| Appendix D. UPF Descriptions for Power Gating                             | 227     |  |

| D.1 Power Gating Implementation                                           | 227     |  |

| D.2 Double-Gated SRPG implementation                                      | 228     |  |

| Appendix E. Measurement Setup                                             | 233     |  |

| Appendix F. Register Configurations of the Hardware Power Management Modu | les 235 |  |

| F.1 Power Management Unit Register Mapping                                | 235     |  |

| F.2 Wake-Up Controller Register Mapping                                   | 236     |  |

| F.3 Adaptive Power Management Register Mapping                            | 236     |  |

| F.4 C-code memory mapping                                                 | 237     |  |

| Appendix G. Summary of Contributions                                      | 239     |  |

| Biography                                                                 |         |  |

| Bibliography                                                              | 245     |  |

# **List of Figures**

| 8    | Picture of the first transistor ever assembled at Bell Labs in 1947                | XX |

|------|------------------------------------------------------------------------------------|----|

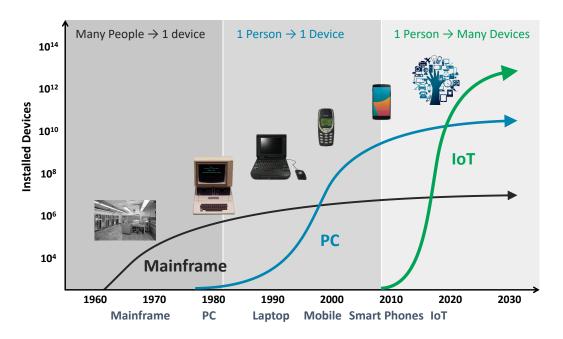

| 9    | Computer hardware paradigms shifting and available electronic devices              | 2  |

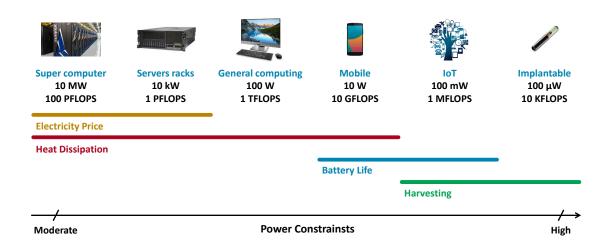

| 10   | Computer systems according to their performances and power consumption             | 3  |

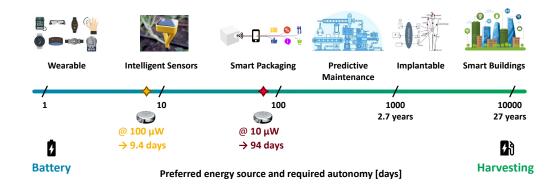

| 11   | Required autonomy of IoT devices depending on their area of application            | 4  |

| 12   | Harvesters power generation and power consumption of electronic devices            | 5  |

| 13   | Evolution of the computing efficiency at peak performance over time                | 6  |

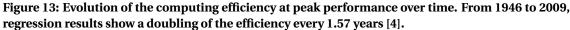

| 14   | Evolution of battery energy density over the years.                                | 7  |

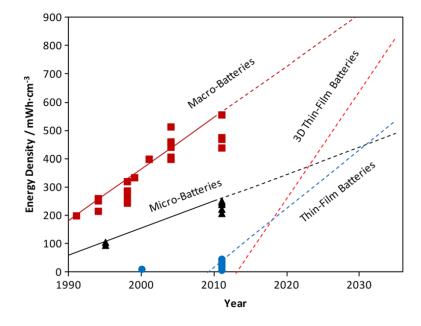

| 15   | Application contexts for NZP applications.                                         | 8  |

| 1.1  | Integrated Circuit implementation stack.                                           | 13 |

| 1.2  | Scaling of technology feature size and nominal supply voltage over time            | 15 |

| 1.3  | pMOS and nMOS transistors cross-sections in standard CMOS bulk process             | 16 |

| 1.4  | Summary of leakage current mechanisms in a deep-submicrometer transistors          | 17 |

| 1.5  | Transistor dynamic current according to the gate overdrive                         | 18 |

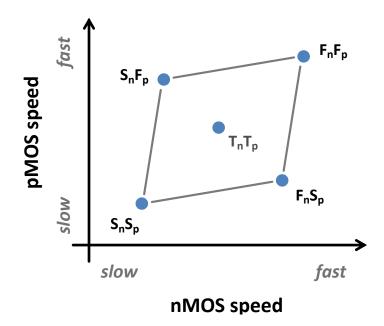

| 1.6  | Visualization of the different process corners.                                    | 19 |

| 1.7  | Body biasing capabilities in standard CMOS bulk process                            | 20 |

| 1.8  | Schematic views of three types of transistor: planar Bulk, UTBB FD-SOI and FinFET. | 21 |

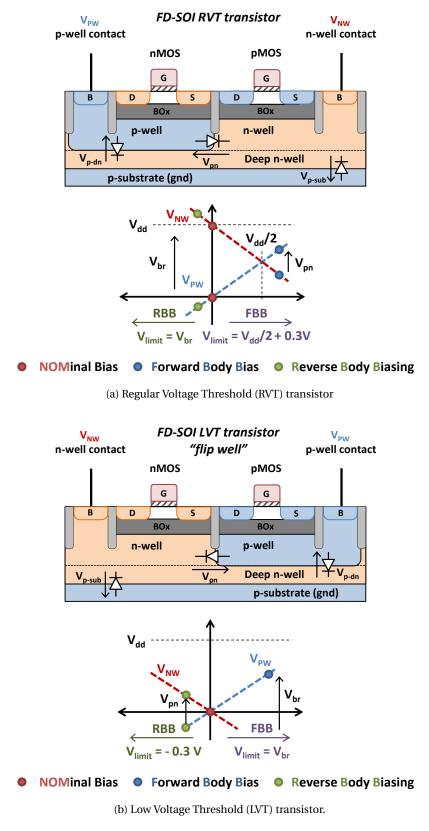

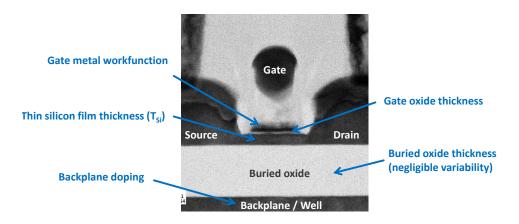

| 1.9  | 28 nm UTBB FD-SOI CMOS transistors cross section and biasing capabilities          | 23 |

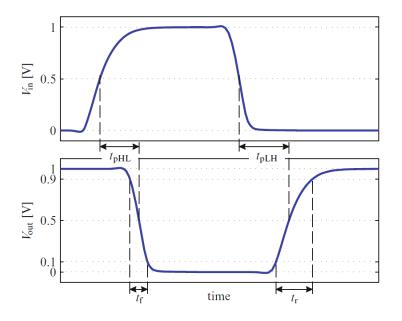

| 1.10 | Transient characteristics of an inverter.                                          | 24 |

| 1.11 | Impact of the $I_{ON}/I_{OFF}$ on the behavior of a standard inverter              | 25 |

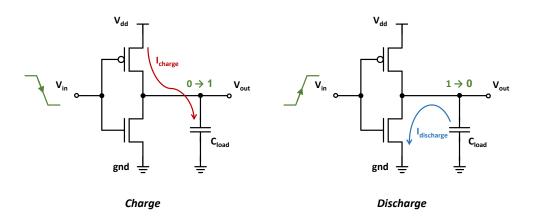

| 1.12 | Charge and discharge currents during the switching operation of a CMOS inverter.   | 27 |

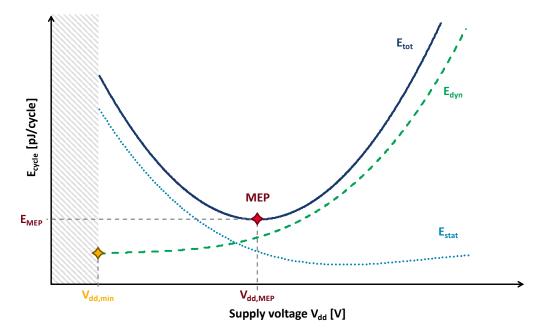

| 1.13 | Energy according to the supply voltage.                                            | 29 |

| 1.14 | Illustration of conventional DT-CMOS scheme.                                       | 30 |

| 1.15 | Schematic illustration of conventional biasing and SWBB configurations             | 31 |

| 1.16 | Nominal cycle period and additional PVT margins.                                   | 32 |

| 1.17 | Automatic clock gating performed by Synopsys design compiler tool.                 | 33 |

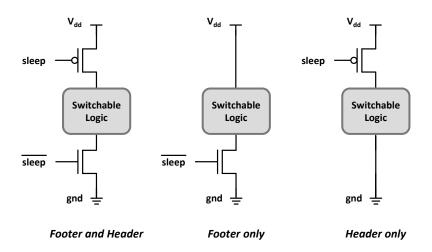

| 1.18 | Power gating implementations.                                                      | 34 |

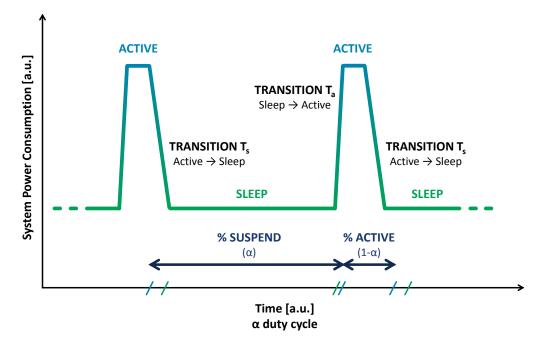

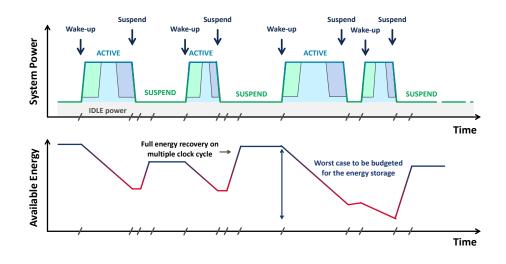

| 1.19 | Activity scenario of a duty-cycled Ultra-Low-Power system.                   | 36 |

|------|------------------------------------------------------------------------------|----|

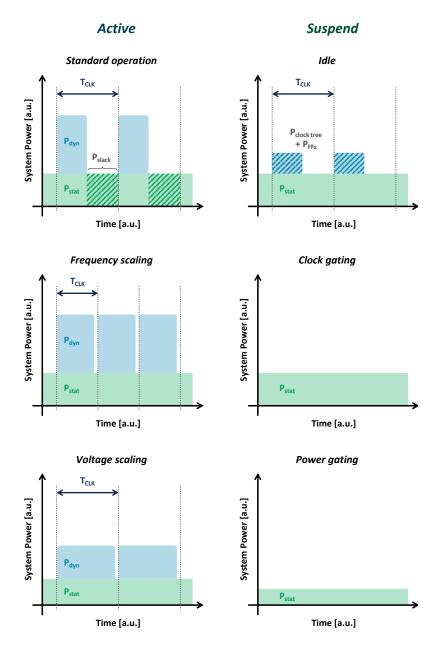

| 1.20 | Impact of system-level power management techniques on the power consumption. | 40 |

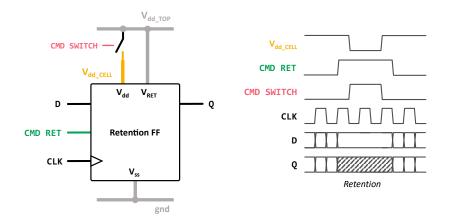

| 1.21 | Schematic of SRPG implementation.                                            | 41 |

| 2.1  | Energy flow for an ULP IoT device.                                           | 50 |

| 2.2  | Relatively general architecture of IoT nodes with detailed sub-systems       | 51 |

| 2.3  | Clock modulation during the duty-cycled operation of an IoT device.          | 53 |

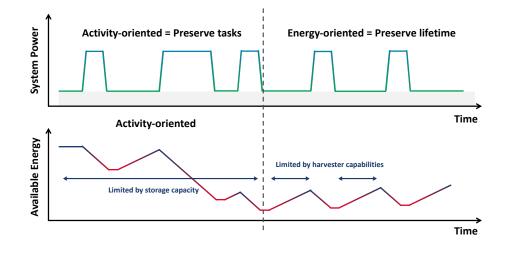

| 2.4  | Energy driven use case.                                                      | 54 |

| 2.5  | Activity driven use case.                                                    | 55 |

| 2.6  | From activity to energy driven mode.                                         | 55 |

| 2.7  | ULP SoC functional description.                                              | 57 |

| 2.8  | Timeline of the Figure 2.7 activated domains according to the activity       | 58 |

| 2.9  | Architecturally defined memory map of the Cortex-M0+ implementation          | 60 |

| 2.10 | Adopted system partition for ULP applications.                               | 61 |

| 3.1  | Oscillator classification based on their physical type of operation.         | 65 |

| 3.2  | Relocking principle to achieve ULP operations.                               | 67 |

| 3.3  | Block diagram of the clock generator architecture.                           | 68 |

| 3.4  | Schematic of the current controlled ring oscillator.                         | 71 |

| 3.5  | Current control schemes of a pMOS transistor                                 | 71 |

| 3.6  | Current modulation of a blocked pMOS transistor.                             | 72 |

| 3.7  | Schematic of the digitally controlled leakage sources                        | 72 |

| 3.8  | Current sources selection scheme to reach a given target frequency.          | 73 |

| 3.9  | Simulated LRO output frequency.                                              | 74 |

| 3.10 | Evaluation of the LRO accuracy.                                              | 75 |

| 3.11 | Main sources of variability for a FD-SOI transistor.                         | 76 |

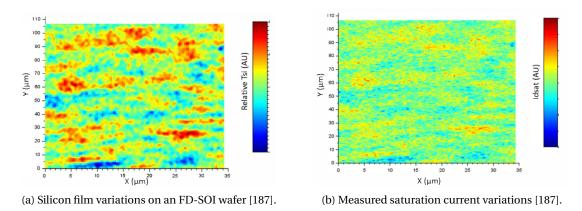

| 3.12 | Silicon thickness evaluation of a wafer used in 28 nm FD-SOI technology      | 76 |

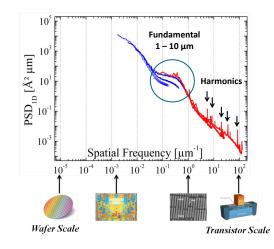

| 3.13 | PSD functions describing the surface topological variations of an SOI wafer  | 77 |

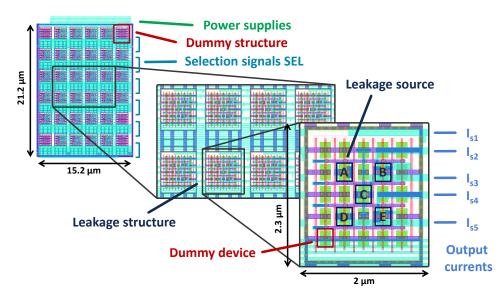

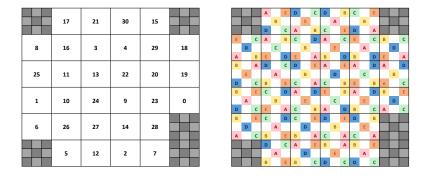

| 3.14 | Layout of the fine array composed of 31 leakage structures.                  | 77 |

| 3.15 | Chosen random distribution of the 31 leakage structure.                      | 78 |

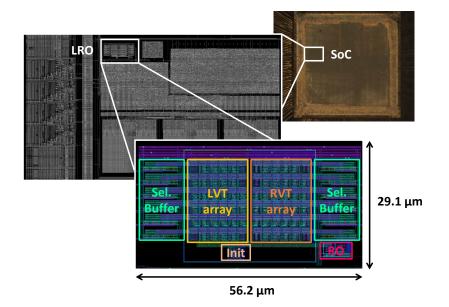

| 3.16 | Testchip micrograph and view of LRO implementation.                          | 78 |

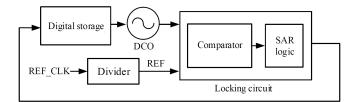

| 3.17 | DCO architecture using a SAR based locking circuit.                          | 79 |

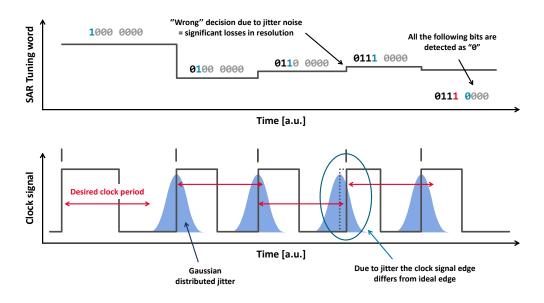

| 3.18 | Evaluation of the tuning word in a SAR relocking scheme and impact of jitter | 80 |

| 3.19 | Multi-level bangbang calibration.                                            | 80 |

| 3.20 | Structural diagram of an Integral corrector.                                 | 81 |

|      | Control Logic Unit block diagram.                                            | 83 |

| 3.22 | Stability analysis of the compensation stage.                                | 84 |

| 3.23 Stability analysis of the compensation stage with a corrector gain $K_c = -5$    | 84  |

|---------------------------------------------------------------------------------------|-----|

| 3.24 Block diagram of the complete system.                                            | 85  |

| 3.25 SPI and communication interface protocol with the system                         | 85  |

| 3.26 Comparison of simulated and measured LRO frequency ranges                        | 86  |

| 3.27 Measured peak-to-peak and RMS jitter for 10 dice.                                | 87  |

| 3.28 Evaluation of the locking scheme                                                 | 87  |

| 3.29 Evaluation of the output frequency when locked.                                  | 88  |

| 3.30 Measured output frequency when locked.                                           | 89  |

| 3.31 Measured LRO Allan deviation                                                     | 89  |

| 3.32 Example of a wireless sensor node operation scenario                             | 90  |

| 3.33 Evaluation of the total oscillator power and drift trade-off                     | 91  |

| 3.34 Power overhead resulting from the utilization of the relocking scheme.           | 93  |

| 3.35 Comparison of Allan Deviation/Power with State of the Art clock generators       | 95  |

| 4.1 qFO4 logical path schematic.                                                      | 100 |

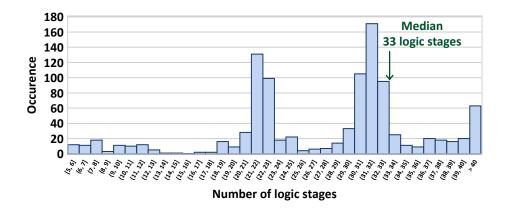

| 4.2 Evaluation of Cortex-M0+ critical paths length.                                   | 100 |

| 4.3 qFO4 frequency according to the PVT conditions.                                   | 101 |

| 4.4 Energy performance of qFO4 paths in 22 nm FD-SOI                                  | 102 |

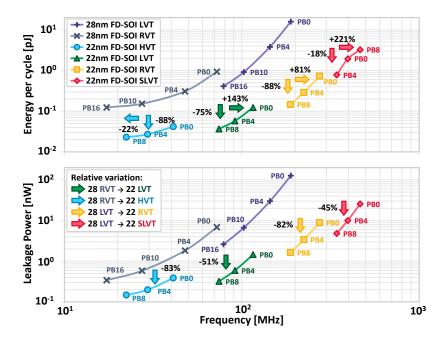

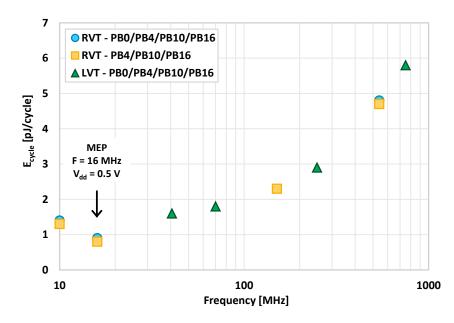

| 4.5 Comparison of FD-SOI technology nodes using qFO4 paths.                           | 102 |

| 4.6 Subset of Cortex-M0+ Synthesis loops performances                                 | 103 |

| 4.7 Global power switch design using LVT flavor pMOS.                                 | 105 |

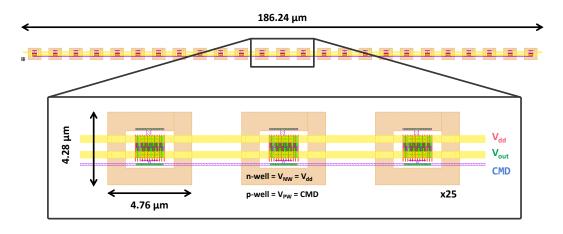

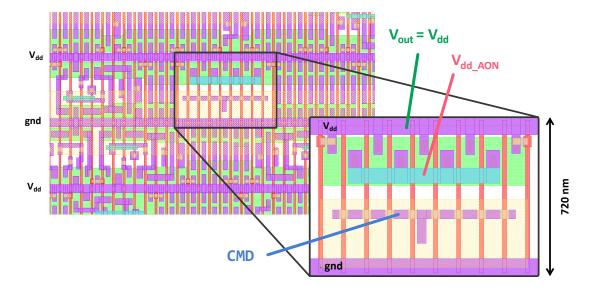

| 4.8 Layout view of the global pMOS power switch                                       | 106 |

| 4.9 Integration of the global power switch into the core power grid.                  | 107 |

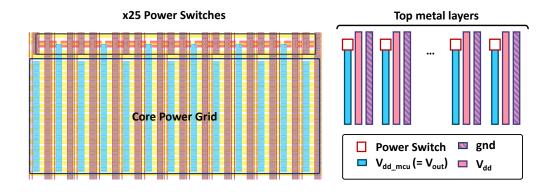

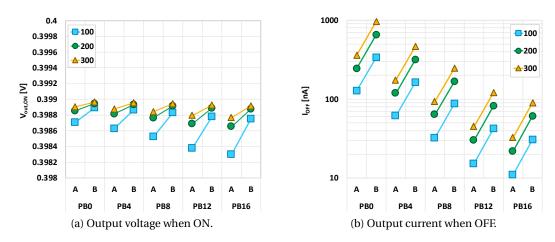

| 4.10 Performances evaluation of the global power switch.                              | 108 |

| 4.11 Schematic floor plan for distributed power switches.                             | 108 |

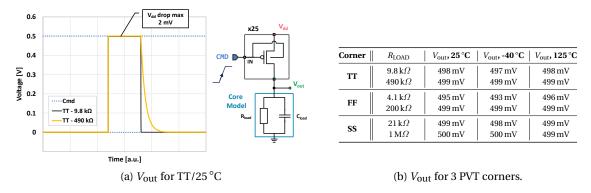

| 4.12 Power gating standard cell layout and integration                                | 109 |

| 4.13 Performance evaluation for two types of RVT header cells in 22 nm FD-SOI         | 109 |

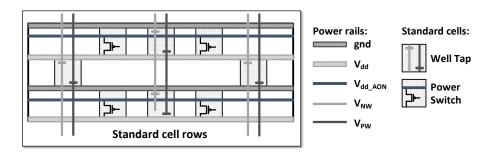

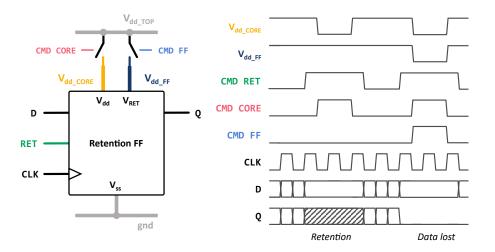

| 4.14 Schematic of a double-gated SRPG implementation.                                 | 110 |

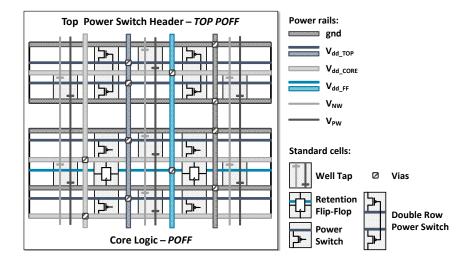

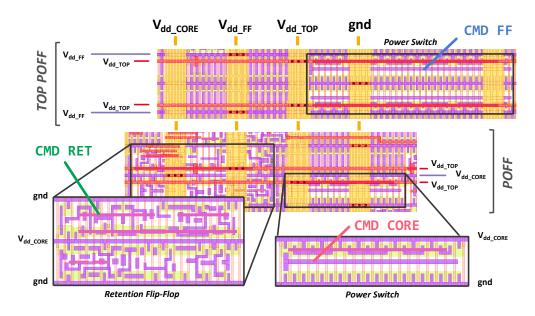

| 4.15 Double-gated SRPG implementation in 22 nm FD-SOI                                 | 111 |

| 4.16 Layout abstraction for double-gated 22 nm FD-SOI SRPG implementation             | 112 |

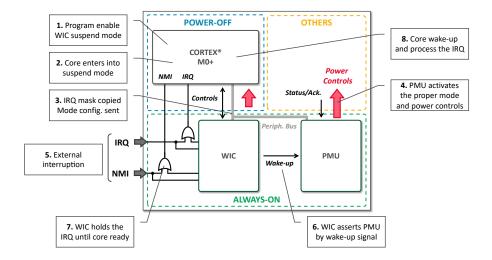

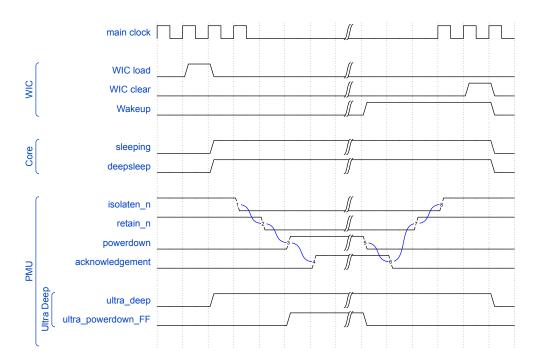

| 4.17 Interruption handling during suspend modes and PMU control signals.              | 114 |

| 4.18 PMU control sequence and signal generation during suspend mode transitions.      | 115 |

| 4.19 Context restoration and IRQ handling during suspend mode with no retention. $$ . | 116 |

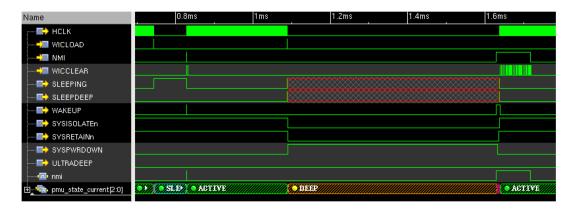

| 4.20 Simulated behavior of the PMU                                                    | 117 |

| 4.21 Block diagram of the DDSS clock generator.                                       | 118 |

| 4.22 Block diagram of the DFS implementation at system level                          | 119 |

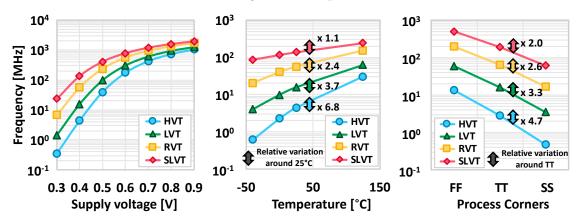

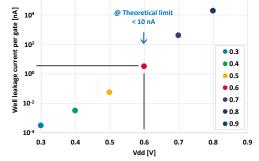

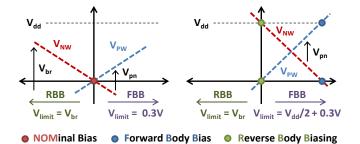

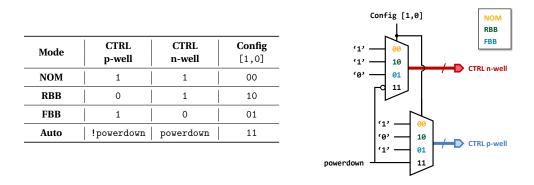

| 4.23 Proposed 28 nm FD-SOI body-biasing modes                                                                                                                      | 21 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.24 Evaluation of the supply voltage before well junction leakage occurs 1                                                                                        | 22 |

| 4.25 qFO4 frequency using NOM and FBB modes according to the supply voltage. $\ . \ . \ 1$                                                                         | 23 |

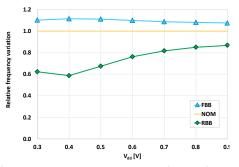

| 4.26 Evaluation of the energy per cycle according to the frequency                                                                                                 | 24 |

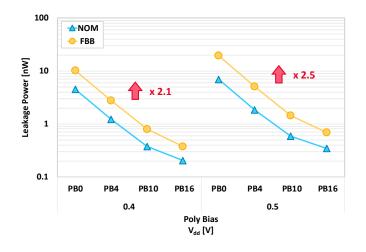

| 4.27 Leakage power of a qFO4 according to the Polysilicon Biasing                                                                                                  | 24 |

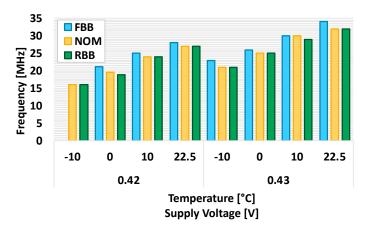

| 4.28 Frequency of a qFO4 according to the temperature and the supply voltage 1                                                                                     | 25 |

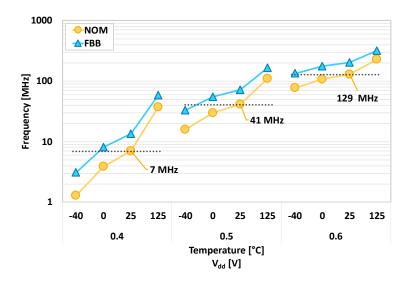

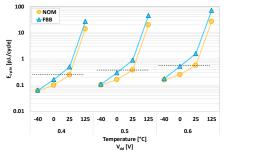

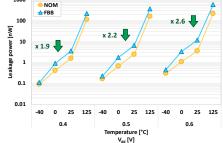

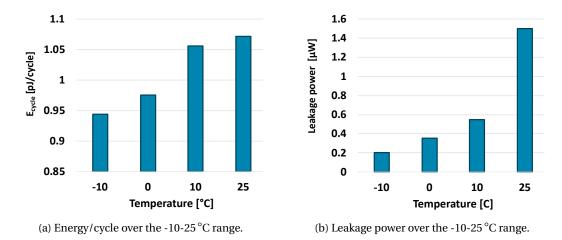

| 4.29 Power consumption of a qFO4 according to the temperature and the supply voltage.1                                                                             | 26 |

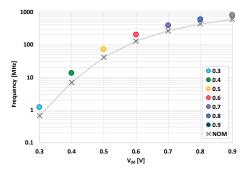

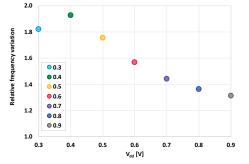

| 4.30 Proposed 22 nm FD-SOI body-biasing modes                                                                                                                      | 27 |

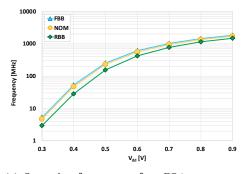

| 4.31 Evaluation of a qFO4 frequency using NOM and FBB modes                                                                                                        | 27 |

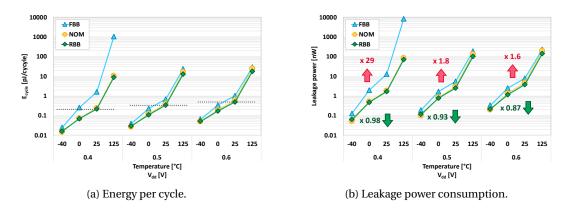

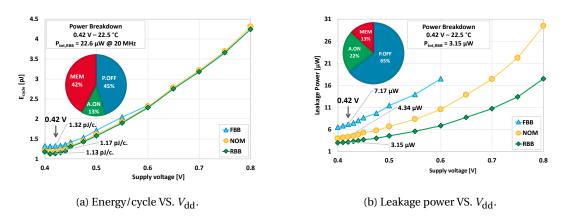

| 4.32 Performance analysis of the SWBB modes in 22 nm FD-SOI                                                                                                        | 28 |

| 4.33 Rising edge propagation along a qFO4                                                                                                                          | 29 |

| 4.34 Frequency of a qFO4 according to the temperature and the supply voltage $1$                                                                                   | 29 |

| $4.35 \ {\rm Power \ consumption \ of \ a \ qFO4 \ according \ to \ the \ temperature \ and \ the \ supply \ voltage.1}$                                           | 30 |

| 4.36 Self body bias generator using standard inverters                                                                                                             | 31 |

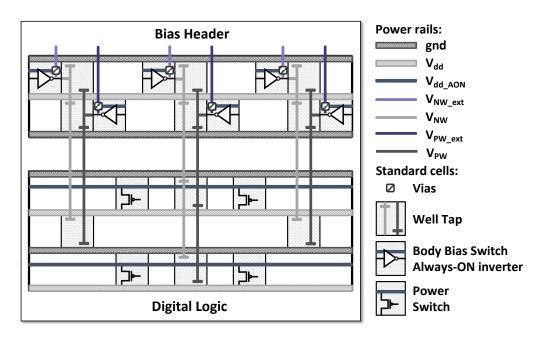

| 4.37 Overview of the system floorplan with integrated self body-biasing. $\ldots \ldots 1$                                                                         | 32 |

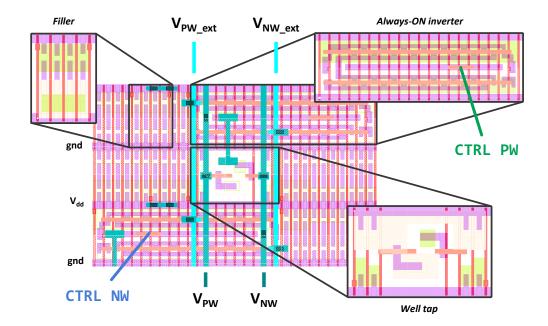

| 4.38 Layout abstraction of the SWBB implementation                                                                                                                 | 33 |

| 4.39 Self body bias generator mode selection through PMU controls 1                                                                                                | 33 |

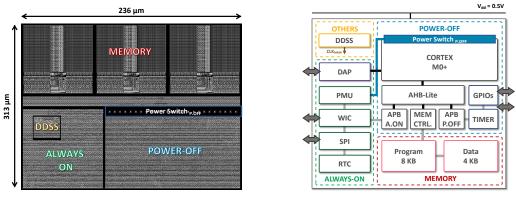

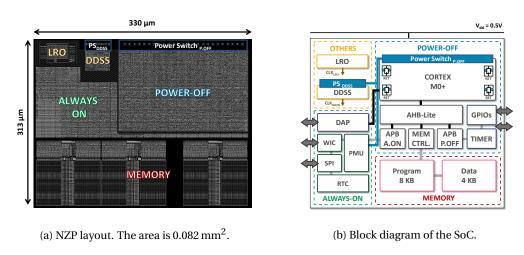

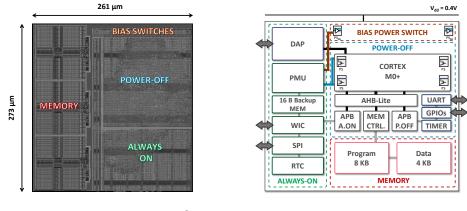

| 4.40 NZP28 V1.0 – 28 nm FD-SOI implementation                                                                                                                      | 35 |

| 4.41 NZP28 V2.0 – 28 nm FD-SOI implementation                                                                                                                      | 35 |

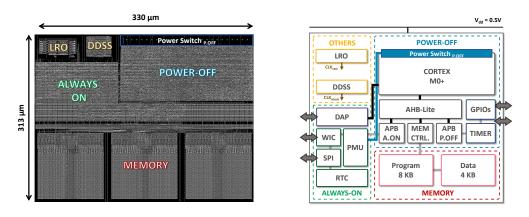

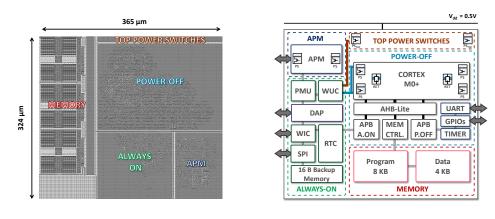

| 4.42 NZP28 V3.0 – 28 nm FD-SOI implementation                                                                                                                      | 36 |

| 4.43 NZP22 V1.0 – 22 nm FD-SOI implementation. $\dots \dots \dots$ | 37 |

| 4.44 NZP22 V2.0 – 22 nm FD-SOI implementation                                                                                                                      | 37 |

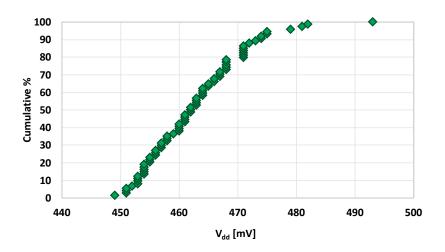

| 4.45 Cumulative percentage of working parts of NZP28 V1.0                                                                                                          | 38 |

| 4.46 Measured mean core frequency of NZP28 V1.0 according to the supply voltage.<br>. $\ 1$                                                                        | 39 |

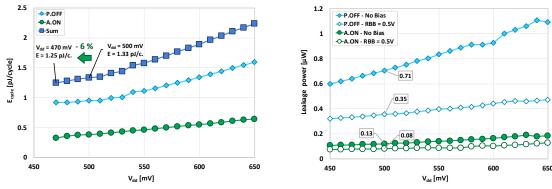

| 4.47 NZP28 V1.0 power evaluation according to the supply voltage 1                                                                                                 | 40 |

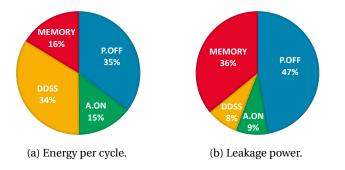

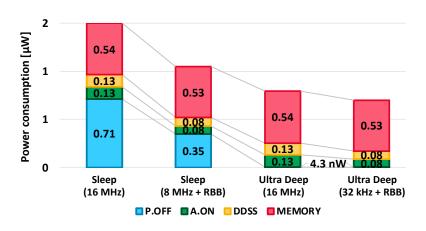

| 4.48 NZP28 V1.0 SoC power breakdown                                                                                                                                | 40 |

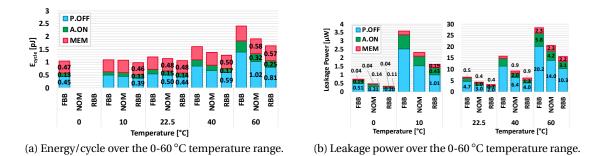

| 4.49 Influence of frequency scaling on the power consumption                                                                                                       | 41 |

| 4.50 Reduction of the leakage power using RBB                                                                                                                      | 42 |

| 4.51 Total power breakdown of the NZP28 – V1.0 SoC                                                                                                                 | 42 |

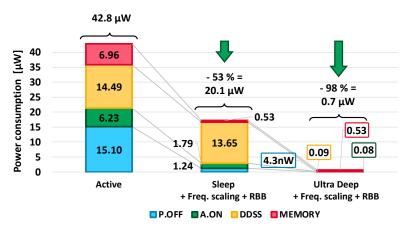

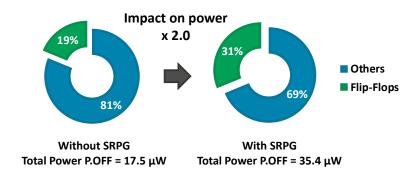

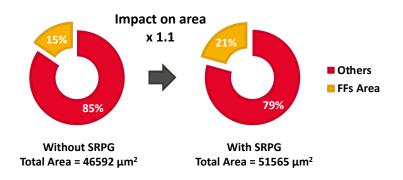

| 4.52 Power impact of SRPG in 28 nm                                                                                                                                 | 43 |

| 4.53 Area impact of SRPG in 28 nm on the whole SoC.                                                                                                                | 44 |

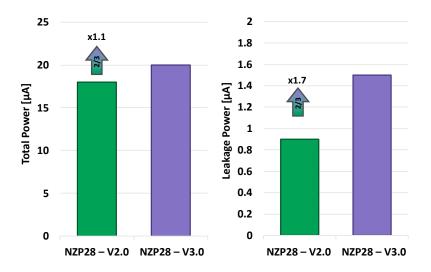

| 4.54 NZP V2.0 and V3.0 power consumption in 28 nm FD-SOI                                                                                                           | 44 |

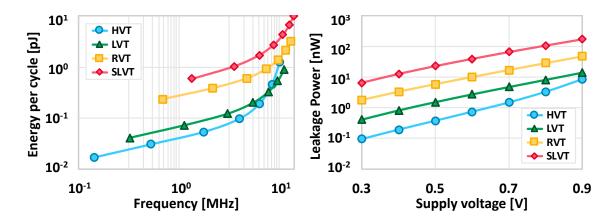

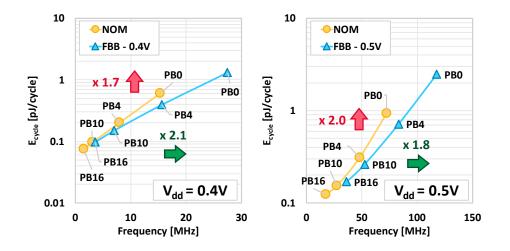

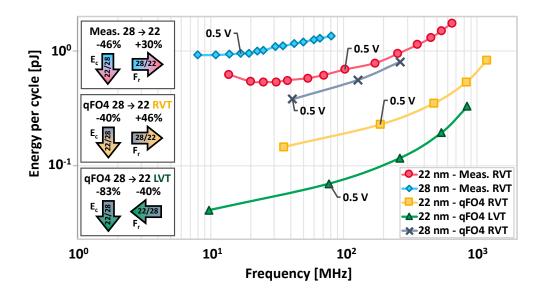

| 4.55 Energy/Frequency Trade-off analysis in 28 nm and 22 nm FD-SOI 1                                                                                               | 45 |

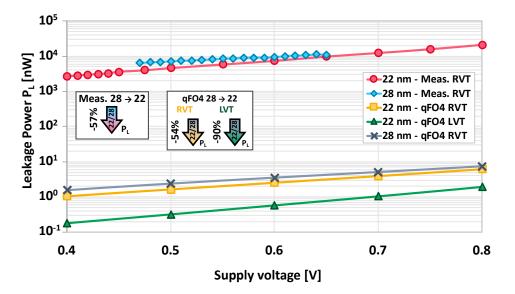

| 4.56 Leakage Power according to the supply voltage in 28 nm and 22 nm FD-SOI $\ldots$ 1                                                                            | 46 |

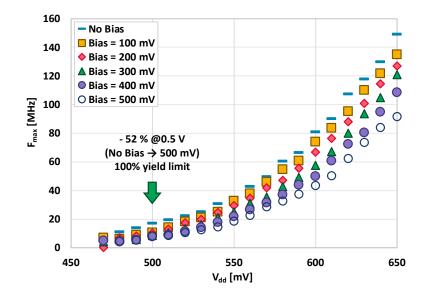

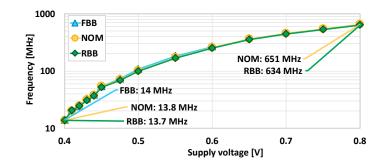

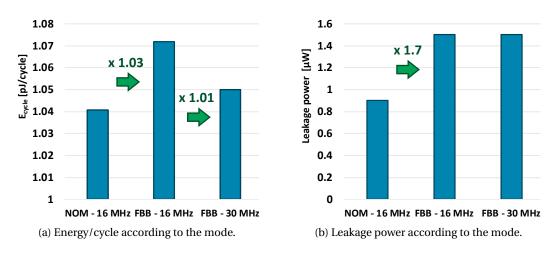

| 4.57 Measured NZP22 V1.0 frequency according to the supply voltage and bias 1                                                                                      | 47 |

| 4.58 NZP22 V1.0 measured SoC's performances                                                                                                                        | 47 |

| 4.59 NZP22 V1.0 measured maximum frequency.                                         | 148     |

|-------------------------------------------------------------------------------------|---------|

| 4.60 NZP22 V1.0 SoC's power with temperature compensation scheme enabled            | 149     |

| 4.61 Evaluation of self-body bias scheme on NZP28 V3.0 for energy/frequency trade-o | off.149 |

| 4.62 NZP28 V3.0 SoC's power with FBB scheme enabled for temperature compensation    | n.150   |

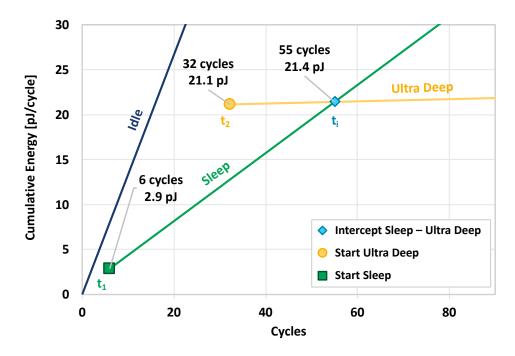

| 4.63 Evolution of the energy consumption depending on the selected power state.     | 151     |

|                                                                                     | 100     |

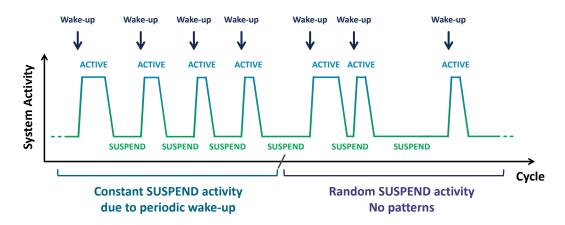

| 5.1 System activity describing various suspend scenarios.                           |         |

| 5.2 Energy consumed by the system according to the heuristic solution selected.     |         |

| 5.3 Color map representation of the deep sleep heuristic solution.                  |         |

| 5.4 Example of a simple finite Markov Decision Process                              |         |

| 5.5 TiSMDP representation using 3 states                                            |         |

| 5.6 Basic agent and environment interactions used in RL algorithms.                 | 165     |

| 5.7 Generic SoC architecture used as a template for the APM implementation          | 168     |

| 5.8 Generic system Markov Decision Process                                          | 168     |

| 5.9 MDP diagram of the system and Q-matrix associated.                              | 169     |

| 5.10 Definition of the energy consumed during the system transitions.               | 170     |

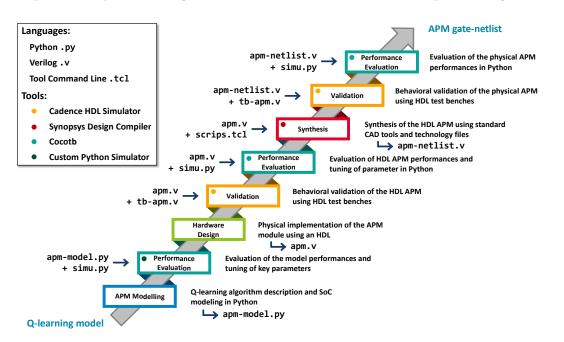

| 5.11 Mixed HDL–Python conception and validation flow                                | 172     |

| 5.12 Evaluation of different RL-algorithms.                                         | 173     |

| 5.13 Energy color map of a the Q-learning algorithms with two system representation | s. 174  |

| 5.14 Comparison of the heuristic solution with the Q-learning algorithm.            | 175     |

| 5.15 Evaluation of the robustness and stability of the Q-learning                   | 176     |

| 5.16 Evaluation of three different exploration policies.                            | 178     |

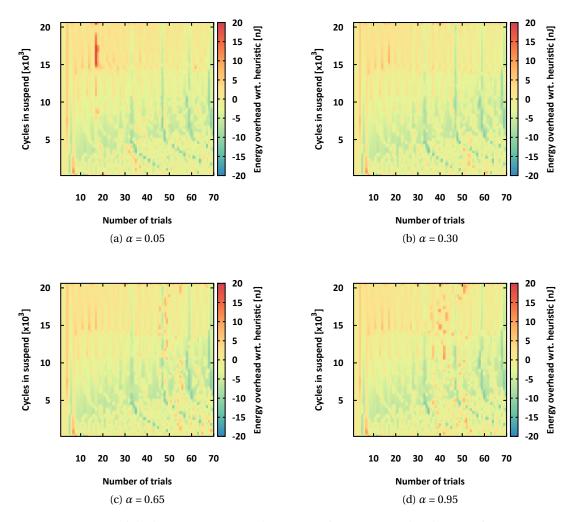

| 5.17 Energy colormap of the implemented Q-learning solution.                        | 179     |

| 5.18 APM performances according to the learning rate and discount factor.           | 180     |

| 5.19 Impact of the learning rate on the APM performances.                           | 181     |

| 5.20 Comparison of the energy consumption gains and losses of the generic APM.      | 182     |

| 5.21 Simplified NZP System MDP.                                                     | 184     |

| 5.22 Comparison of the energy consumption gains and losses of the NZP-oriented AP   | M.185   |

| 5.23 Interaction model between the APM and the PMU of the SoC.                      | 188     |

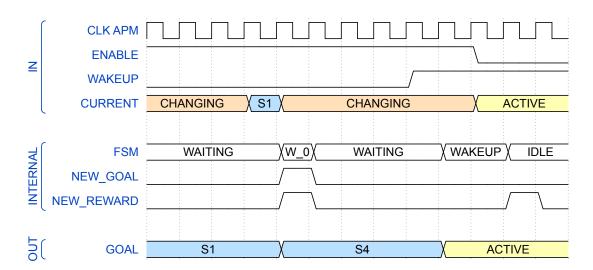

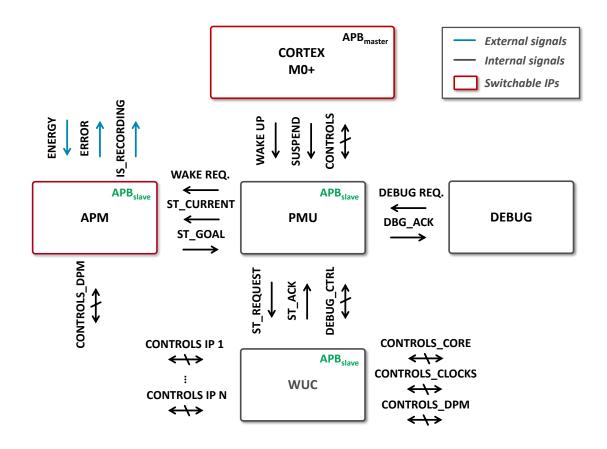

| 5.24 FSM of the APM HW module.                                                      | 189     |

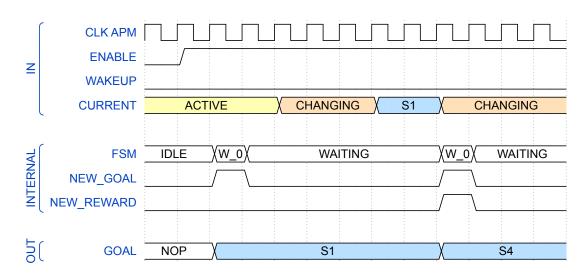

| 5.25 Suspend sequence timing diagram of the APM – Beginning                         | 190     |

| 5.26 Suspend sequence timing diagram of the APM – End                               | 190     |

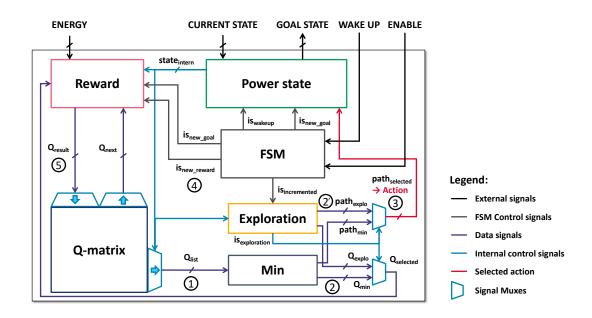

| 5.27 Block diagram of APM HW module.                                                | 191     |

| 5.28 Verilog code description to generate the $Q_{matrix}$ coefficients             | 192     |

| 5.29 System integration of PMU, WUC and APM modules.                                |         |

| 5.30 Block diagram of the NZP22 – V2.0 integrating the PMU, WUC and APM modules     | s. 195  |

| 5.31 | Simulated behavior of the APM module.                                           | 197 |

|------|---------------------------------------------------------------------------------|-----|

| 5.32 | Simplified flow chart describing the functional validation                      | 198 |

| 5.33 | List of the main contributions from device up to system level                   | 203 |

|      |                                                                                 | 000 |

| A.1  |                                                                                 | 209 |

| A.2  | Functional block diagram of the ARM Cortex–M0+                                  | 212 |

| A.3  | Two-stage pipeline representation of the Cortex–M0+                             | 215 |

| B.1  | Accuracy and stability evaluation.                                              | 217 |

| B.2  | Allan deviation of timers with regard to their power consumption                | 219 |

| C 1  | Electronic Design Automation flow for digital circuit implementations.          | 221 |

|      |                                                                                 |     |

| C.2  | Dummy system for power intent basic definitions.                                | 224 |

| D.1  | UPF standard decription to define a power gating strategy.                      | 227 |

| D.2  | Power switches liberty files attributes.                                        | 228 |

| D.3  | Triple power grid description for SRPG implementation in 22 nm FD-SOI. $\ldots$ | 229 |

| D.4  | Power intent description for SRPG implementation (1/3)                          | 230 |

| D.5  | Power intent description for SRPG implementation (2/3)                          | 231 |

| D.6  | Power intent description for SRPG implementation (3/3)                          | 232 |

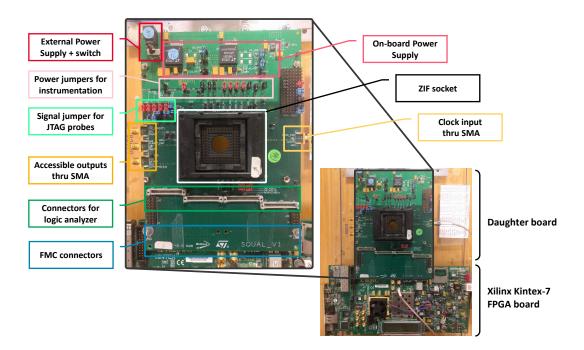

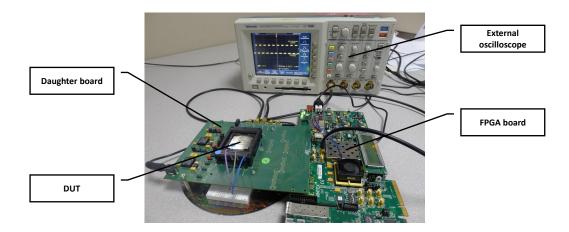

| E.1  | Picture of the daughter board and instrumentation setup.                        | 234 |

| E.2  | FPGA board instrumentation setup under utilization.                             | 234 |

| F.1  | C-code header file giving the HPM modules memory mapping                        | 238 |

# List of Tables

| 1.1 | Effect of device scaling on some of the transistor intrinsic parameters           | 14  |

|-----|-----------------------------------------------------------------------------------|-----|

| 1.2 | Logic Core Device Technology Roadmap based on IRDS projections.                   | 15  |

| 1.3 | Suspend mode consumption and autonomy for two standard BLE devices                | 37  |

| 1.4 | Summary of the Ultra-Low-Power techniques encountered                             | 42  |

| 1.5 | ULP SoC and referencing of the low-power optimizations $(1/2)$                    | 45  |

| 1.6 | ULP SoC and referencing of the low-power optimizations (2/2)                      | 46  |

| 2.1 | SoC power modes and corresponding peripheral states.                              | 58  |

| 3.1 | Qualitative study of electronic oscillators                                       | 66  |

| 3.2 | CMOS-based oscillators summary of performances                                    | 70  |

| 3.3 | LRO $\Leftrightarrow$ CLU Interface                                               | 73  |

| 3.4 | Oscillator frequency specifications in TT                                         | 74  |

| 3.5 | Design parameters of the devices used                                             | 75  |

| 3.6 | Qualitative study of digital compensations                                        | 81  |

| 3.7 | Evaluation of the drift and corresponding mismatch power of the relocking scheme. | 92  |

| 3.8 | Summary of the achieved performances and state of the art comparison              | 94  |

| 4.1 | Shut-off performance analysis for a single pMOS transistor                        | 106 |

| 4.2 | System partitions and proposed ULP modes                                          | 113 |

| 4.3 | DFS and clock generator modes.                                                    | 120 |

| 4.4 | NZP28 V1.0 SoC energy/cycle and total power breakdown.                            | 141 |

| 4.5 | Summary of the NZP V1.0 power modes and configuration.                            | 142 |

| 4.6 | Estimation of the SRPG impact on the power consumption                            | 143 |

| 4.7 | SRPG impact on the area.                                                          | 145 |

| 4.8 | NZP22 – V1.0 power breakdown according to the ULP modes                           | 148 |

| 4.9 | ULP SoC and referencing of the low-power optimizations performed                  | 154 |

| 5.1 | Evaluation of different systems for Adaptive Power Management implementation.     | 162 |

| 5.2 | Comparison of Reinforcement Learning algorithms implementations.                   | 166 |

|-----|------------------------------------------------------------------------------------|-----|

| 5.3 | Performance evaluation of the APM according to the minimum achievable energy.      | 175 |

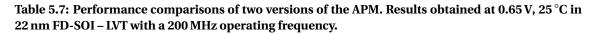

| 5.4 | Performance evaluation of the APM relatively to the Deep Sleep heuristic solution. | 182 |