UNIVERSITÀ DI PISA Scuola di Dottorato in Ingegneria "Leonardo da Vinci" UNIVERSITÈ BORDEAUX 1 Ecole Doctorale des Sciences Physiques et de l'Ingeniéur

Corso di Dottorato di Ricerca in Ingegneria dell'Informazione Cours de Doctorat en Électronique Tesi di Dottorato di Ricerca - Thèse de Doctorat - Doctoral Thesis

# Deep Sub-micron RF-CMOS Design and Applications of Modern UWB and Millimeter-wave Wireless Transceivers

Autore - Auteur - Author

### Domenico PEPE

| Relatori - Directeurs de Thèse - Supervisors         |  |

|------------------------------------------------------|--|

| Dr. Domenico ZITO (Università di Pisa)               |  |

| Dr. Thierry TARIS (Universitè Bordeaux 1)            |  |

| Prof. Bruno NERI (Università di Pisa)                |  |

| Prof. Jean-Baptiste BEGUERET (Universitè Bordeaux 1) |  |

|                                                      |  |

Pisa, Italy, 2009

### **Examining Commission**

Prof. Carmine Ciofi Dipartimento di Fisica della Materia e Ingegneria Elettronica, Università di Messina

Prof. Guido Masera Dipartimento di Elettronica, Politecnico di Torino

Prof. Massimo Macucci Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Università di Pisa

Dr. Domenico Zito Tyndall National Institute, University College Cork

Prof. Bruno Neri Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Università di Pisa

Dr. Thierry Taris Laboratoire IMS, Universitè Bordeaux 1

Prof. Jean-Baptiste Begueret Laboratoire IMS, Universitè Bordeaux 1

### **Final Examination**

25<sup>th</sup> June, 2009, Pisa

To my parents

## Acknowledgements

First of all I am grateful to my Family, for fully supporting me in all these years.

I am grateful to my supervisors, Dr. Domenico Zito, Dr. Thierry Taris, Prof. Bruno Neri and Prof. Jean-Baptiste Begueret, for their precious support and assistance. A special thanks to Domenico Zito, who made this research work possible and that in these years has been a teacher and a friend.

I am grateful to all my colleagues and people that have been worked at RFLab (Pisa), from my MSc thesis mates, to PhD mates, and to all the people that made here their thesis, whose work has been very important for this research.

I am grateful to all my collegues and professors of the IMS Laboratory (Bordeaux), in particular Thierry Taris for his precious support and availability.

Moreover, I am grateful to Prof. De Rossi and collegues of "Centro Piaggio" for their support.

### Sommario

L'attività di ricerca scientifica effettuata nell'ambito del corso di dottorato di ricerca si è svolta nel settore della progettazione di circuiti integrati a radio-frequenza, per sistemi ultra-wideband (UWB) e alle onde millimetriche, e si è articolata nei seguenti temi: (i) circuiti integrati a radio-frequenza per ricetrasmettitori a basso consumo di potenza potenza per reti locali wireless; (ii) radar UWB completamente integrato per il monitoraggio cardio-polmonare in tecnologia 90nm CMOS; (iii) amplificatori a basso rumore (LNA) a 60 GHz in tecnologia standard 65nm CMOS.

Nel Capitolo 1 una valutazione teorica della massima distanza operativa dei Radio Frequency Identification Device (RFID) passivi e il progetto di un ricetrasmettitore a bassa potenza per applicazioni ZigBee (IEEE 802.15.4) a 2.4 GHz in tecnologia 0.35µm Bi-CMOS di Austriamicrosystems sono riportati. Inoltre, viene presentato il progetto di un oscillatore controllato in tensione (VCO) a 5-6 GHz in tecnologia 0.35µm di Austriamicrosystems. In particolare, gli induttori sono stati realizzati mediante una nuova versione dell'induttore attivo chiamato "Boot-Strapped Inductor" (BSI). Infine, viene presentato un nuovo circuito equivalente a larga banda, a componenti discreti indipendenti dalla frequenza, per descrivere in termini di equivalenti elettrici a parametri concentrati il comportamento di induttori a spirale integrati su silicio.

Nel Capitolo 2 viene presentata l'attività di ricerca riguardante la realizzazione di un sistema radar UWB indossabile per il monitoraggio cardio-polmonare completamente integrato in tecnologia 90nm CMOS. In dettaglio, sono riportati lo studio di fattibilità, l'analisi di sistema e i risultati delle simulazioni di sistema. Inoltre, viene riportato il progetto dei principali blocchi del sensore radar UWB (l'amplificatore a basso rumore (LNA), il generatore di impulsi e il generatore di ritardo) in tecnologia 90nm CMOS di ST-Microelectronics. I test-chip sono stati realizzati e caratterizzati sperimentalmente. Sono riportati i risultati delle misure, che si sono dimostrati in eccellente accordo con i risultati delle simulazioni post-layout.

Nel Capitolo 3, infine, il progetto di un amplificatore a basso rumore (LNA) a 60 GHz in tecnologia 65nm CMOS di ST-Microelectronics è riportato. Il LNA sfrutta una nuova topologia per ottenere l'adattamento di impedenza in ingresso basata sull'uso di un trasformatore integrato, che permette la realizzazione dell'adattamento di impedenza senza l'applicazione di una degenerazione sul source, che causa un abbassamento del guadagno dell'amplificatore, cosa indesiderata specialmente alle onde millimetriche.

### Riassunto

L'attività di ricerca scientifica effettuata nell'ambito del corso di dottorato di ricerca si è svolta nel settore della progettazione di circuiti integrati a radio-frequenza, per sistemi ultra-wide-band (UWB) e alle onde millimetriche, e si è articolata nei seguenti temi: (i) circuiti integrati a radio-frequenza per ricetrasmettitori a basso consumo di potenza per reti locali wireless; (ii) radar UWB per il monitoraggio cardio-polmonare in tecnologia 90nm CMOS; (iii) amplificatori a basso rumore (LNA) a 60 GHz in tecnologia standard 65nm CMOS.

Questa tesi di dottorato è organizzata in tre Capitoli, ognuno dei quali tratta uno di questi temi sopra elencati affrontati durante la ricerca di dottorato.

#### Capitolo 1: Circuiti Integrati a Radio-frequenza per Ricetrasmettitori a Bassa Potenza per Reti Locali Wireless

Negli ultimi anni l'interesse in applicazioni a basso data-rate, come i Radio-Frequency Identification Device (RFID), e le reti di sensori wireless, è rapidamente cresciuto. Con esso è cresciuta notevolmente anche la richiesta di ricetrasmettitori a basso costo e basso consumo di potenza. I sistemi RFID possono essere classificati in passivi e attivi. I dispositivi passivi possono essere fabbricati a bassissimo costo, tuttavia hanno dei range di funzionamento di qualche metro, che dipende sostanzialmente dalla potenza richiesta dai tag per funzionare. È stata effettuata una valutazione teorica della massima distanza operativa dei RFID passivi [OP1]. Estendere il range di funzionamento dei dispositivi RFID a distanze superiori a una decina di metri è possibile utilizzando tag attivi.

Un ricetrasmettitore a bassa potenza per applicazioni ZigBee (IEEE 802.15.4) a 2.4 GHz è stato progettato in tecnologia  $0.35\mu$ m Bi-CMOS di Austriamicrosystems e presentato in [OP1, OP4]. Il ricevitore, che consiste in un LNA e un mixer I/Q, presenta una cifra di rumore (NF) di 8.7 dB, un guadagno in tensione di 26 dB un punto di intercetta del del terzo ordine riferito all'ingresso (iIP3) di -13 dBm, con un consumo di potenza di 8.6 mW. Il trasmettitore consiste in un amplificatore di potenza a due stadi (un preamplificatore in classe A seguito da un amplificatore in classe C) e due mixer doppiamente bilanciati a cella di Gilbert. Fornisce una potenza di uscita fino a 6 dBm con un consumo di potenza di 16 mW.

Anche l'interesse per canali radio ad elevato data-rate, come nel caso delle Wireless Local Area Network (WLAN), è notevolmente cresciuto negli ultimi anni. Un oscillatore controllato in tensione (VCO) (che tipicamente rappresenta il sottocircuito più critico dell'intero ricetrasmettitore) a 5-6 GHz, è stato progettato in tecnologia 0.35 µm di Austriamicrosystems, e presentato in [OP3, OP7]. Per ovviare ai limiti nelle prestazioni degli induttori a spirale su silicio, è stata sviluppata anche una nuova versione CMOS dell'induttore attivo ad alto fattore di merito "Boot-Strapped Inductor" (BSI) [OP6]. Questa nuova versione di CMOS BSI è stata opportunamente modificata per essere impiegata al posto degli induttori del filtro risonante del VCO. Un modello per piccolo segnale del nuovo BSI è stato implementato con MATLAB<sup>TM</sup>, in modo da poter efficacemente dimensionare ed ottimizzare l'induttore attivo.

Infine, un nuovo circuito equivalente a larga banda, a componenti discreti indipendenti dalla frequenza, è stato sviluppato per descrivere in termini di equivalenti elettrici a parametri concentrati il comportamento di induttori a spirale integrati su silicio e presentato in [OP5]. Questo nuovo modello è in grado di modellizzare efficacemente il comportamento di un induttore integrato in presenza o meno di uno schermo elettromagnetico sottostante (PGS). Gli elementi RLC del circuito sono stati ricavati direttamente dai parametri S dell'induttore. Sono state sviluppate due diverse procedure di "fitting" che offrono diversi livelli di accuratezza.

#### Capitolo 2: Radar UWB per il Monitoraggio Cardio-polmonare in Tecnologia 90nm CMOS

Nel 2002 la Federal Communication Commission (FCC) ha approvato l'immissione sul mercato di dispositivi che sfruttano un nuovo standard di comunicazione che impiega segnali ultra-wideband (UWB). Per i sistemi UWB è stata allocata la porzione di spettro radio 3.1-10.6 GHz, per la prima volta in modo non esclusivo. Il concetto che sta alla base della tecnologia UWB è quello di generare, trasmettere e ricevere impulsi a radio frequenza di durata temporale brevissima (da poche decine di picosecondi a poche decine di nanosecondi). Questo fa si che il segnale UWB abbia uno spettro frequenziale molto ampio (vari GigaHertz) e, pertanto, una densità di energia molto bassa. Tra le molteplici applicazioni per i quali i sistemi UWB sono stati pensati, una delle più promettenti è senz'altro quella del imaging medico.

Contrariamente alle tecniche tradizionali per il monitoraggio dell'attività cardiaca, quali l'elettrocardiogramma o l'impiego di trasduttori a ultrasuoni, i sistemi radar a microonde permettono il monitoraggio della parete cardiaca in maniera non invasiva, senza la necessità di applicare sensori a contatto con il corpo del paziente. Inoltre, a differenza dell'elettrocardiografo, permettono di monitorare direttamente la meccanica della parete cardiaca, anziché l'attività elettrica del cuore. Ci permetterebbe di rivelare l'insorgenza di numerose patologie cardiache che non si manifestano attraverso alcuna anomalia dell'attività elettrica del cuore ad esso associata.

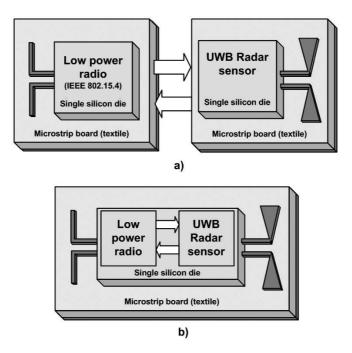

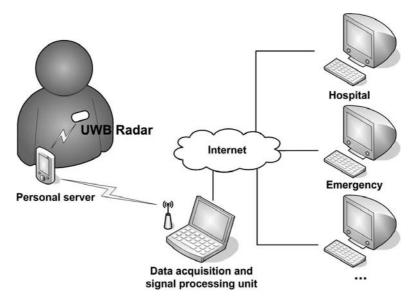

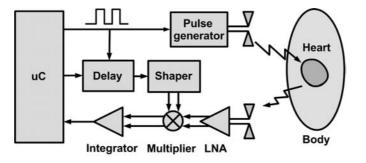

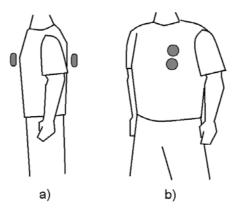

La tecnologia che negli ultimi anni ha registrato il maggiore sviluppo e la maggiore accelerazione in termini di diffusione nel settore delle applicazioni consumer è certamente quella CMOS. Dunque, il sensore radar UWB per il monitoraggio della parete cardiaca può essere realizzato in maniera completamente integrata su un singolo chip, permettendo la realizzazione di dispositivi altamente miniaturizzati, a basso costo e disponibili per il mercato di massa. A questo punto è stata sviluppata l'idea di un sistema indossabile di nuova generazione per il monitoraggio costante della frequenza cardiaca e respiratoria, presentata in [OP2, OP8, OP9, OP11, OP12, OP14, OP15, OP16, OP17]. Il sistema è costituito da un sensore radar UWB e una interfaccia radio low-power (IEEE 802.15.4 ZigBee), che ha il compito di acquisire i dati provenienti dal sensore ed inviarli ad una unità remota di elaborazione dati, sia questa "on-body", o facente parte di una infrastruttura wireless tipo WLAN. La topologia di radar più promettente per questo tipo di applicazione è quella dei radar ad impulsi, per via della loro semplicità architetturale e dei ridotti consumi di potenza.

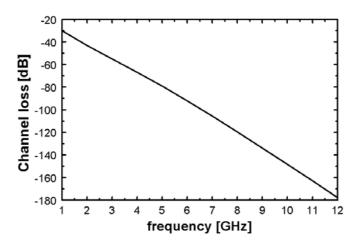

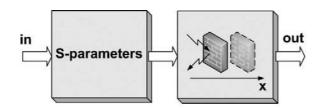

Per quanto riguarda il progetto del sistema radar, uno studio del canale nel quale l'impulso dovrà propagarsi è stato effettuato [OP2, OP9]. Tenendo conto dei vari tessuti del corpo umano e delle loro proprietà dielettriche, è stato sviluppato un modello di canale dipendente dalla frequenza, in modo da poter effettuare le analisi di sistema.

Simulazioni preliminari hanno permesso di individuare nella topologia di tipo correlatore la topologia di ricevitore che garantisce un maggior rapporto segnalerumore all'uscita del ricevitore e una maggiore sensibilità a piccoli spostamenti della parete cardiaca. Un'analisi di sistema è stata effettuata in modo da ripartire le specifiche di sistema tra i vari blocchi del radar UWB. Un modello del canale, che descrive sia le perdite frequenza per frequenza, sia il movimento della parete cardiaca, è stato implementato in modo da poter essere inserito nel simulatore Ptolemy in Agilent  $ADS2005A^{TM}$ . Misure di canale sono state effettuate al fine di verificare la validità del modello proposto [OP2, OP15, OP16]. I risultati mostrano attenuazioni molto prossime ai valori predetti dal modello proposto e da altri lavori pubblicati in letteratura. L'intero sistema è stato simulato, e i risultati delle simulazioni di sistema hanno dimostrato la fattibilità del progetto [OP2, OP8, OP9, OP11, OP12, OP14].

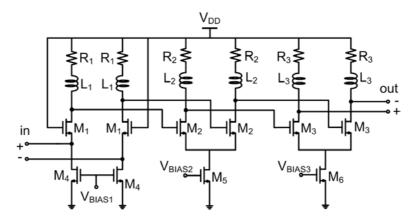

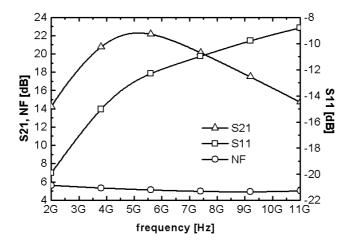

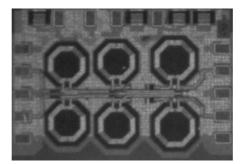

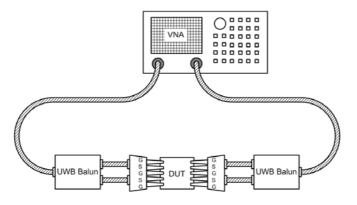

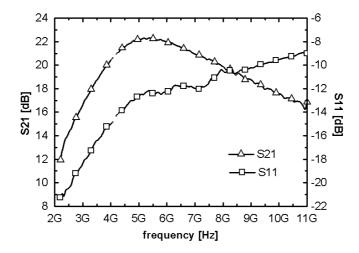

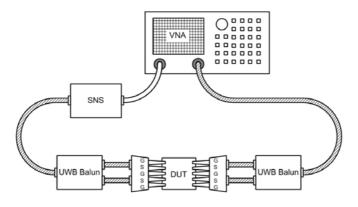

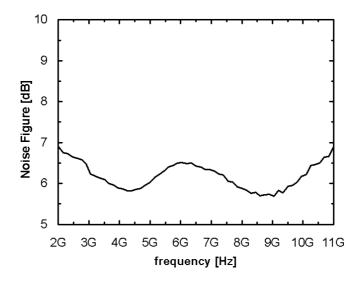

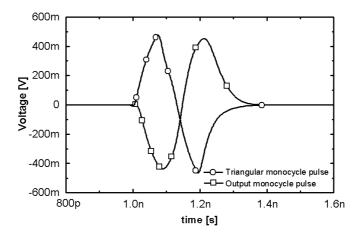

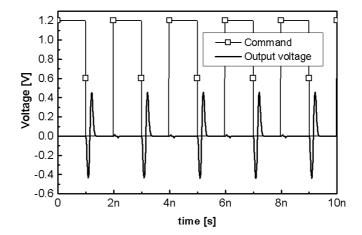

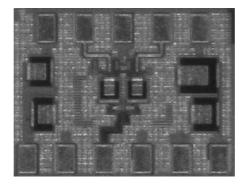

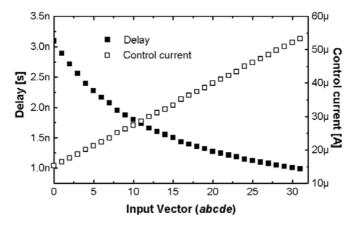

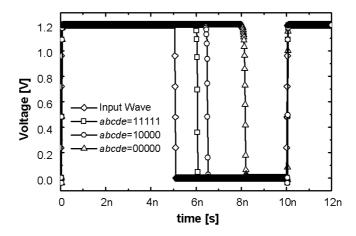

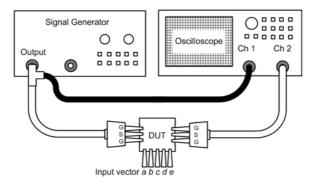

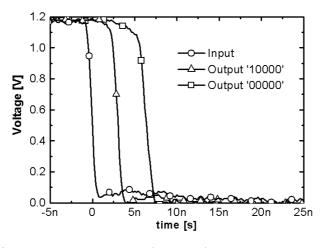

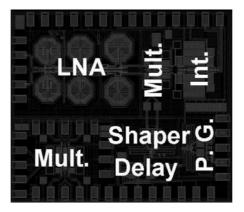

I principali blocchi del sensore radar UWB (amplificatore a basso rumore (LNA), generatore di impulsi e generatore di ritardo) sono stati progettati e realizzati in tecnologia 90nm CMOS di ST-Microelectronics. I circuiti sono stati caratterizzati on-chip utilizzando micro-punte. Il LNA è costituito da un primo stadio a gate comune e due stadi successivi a source comune. Lo stadio di ingresso common gate realizza un adattamento di impedenza a banda larga in ingresso. I due stadi seguenti a source comune forniscono un ulteriore amplificazione di tensione. Le misure mostrano un guadagno di trasduttore di 22.7 dB a 5.2 GHz, una banda a 3-dB di circa 5 GHz, un coefficiente di riflessione in ingresso inferiore a -10.5 dB su tutta la banda, e un punto di compressione a 1-dB di -19.7 dBm, in eccellente accordo con i risultati delle simulazioni post-layout. La cifra di rumore è prossima a 5.5 dB su tutto il range 3.1-10.6 GHz. Il consumo di potenza è 34.8 mW (alimentazione 1.2 V) [OP15, OP16]. Il generatore di impulsi UWB genera un impulso monociclo quando attivato dal fronte negativo di un segnale di comando fornito da un micro-controllore, sfruttando il principio dei formatori d'onda non-lineari. Misure on-chip mostrano che il generatore di impulsi genera un impulso con una durata temporale pari a 430 ps e una ampiezza picco-picco di durata 660 mV. Il consumo di potenza è 19.8 mW (alimentazione 1.2 V) [OP10, OP16]. Il generatore di ritardo è in grado di ritardare, con un ritardo programmabile da 1 a 3 ns, il fronte di discesa di un segnale digitale, in modo da permettere la generazione ritardata (di un ritardo pari al tempo di volo dell'impulso dal radar

al cuore e di nuovo al radar) di una replica locale (on-chip) dell'impulso trasmesso per valutare quindi la correlazione tra questa e l'eco ricevuto proveniente dalla parete cardiaca. Il ritardo è programmabile mediante 5 bit [OP10, OP16].

Si è affrontato l'integrazione totale del sistema radar. Il layout dell'intero sistema radar è stato realizzato in tecnologia 90nm CMOS di ST-Microelectronics e mandato in fonderia.

#### Capitolo 3: Amplificatore a basso rumore (LNA) a 60 GHz in tecnologia standard 65nm CMOS

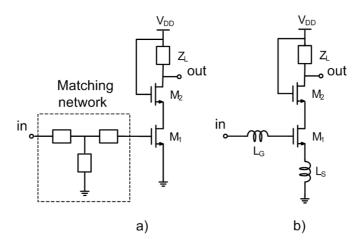

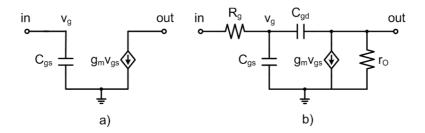

Un amplificatore a basso rumore (LNA) a 60 GHz in tecnologia 65nm CMOS di ST-Microelectronics è stato progettato presso il laboratorio IMS (Laboratoire de l'Intégration du Matériau au Système) con sede a Bordeaux (Francia), e presentato in [OP13].

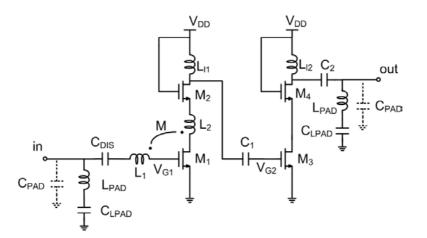

E stata impiegata una nuova tecnica per l'adattamento di impedenza in ingresso, che prevede l'uso di un trasformatore integrato. Il primario del trasformatore è connesso tra l'ingresso a radio-frequenza e il gate del transistor a source comune di un amplificatore cascode, mentre il secondario è connesso tra il drain del transistor a source comune e il source del transistor cascode. Questa tecnica permette la realizzazione dell'adattamento di impedenza senza l'applicazione di una degenerazione sul source, che causa un abbassamento del guadagno dell'amplificatore, cosa indesiderata specie alle onde millimetriche.

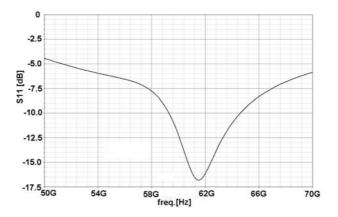

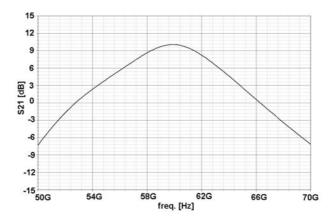

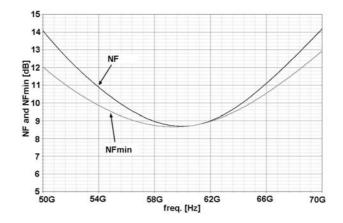

È stato sviluppato un modello del transistor all'interno del simulatore ADS di Agilent per analizzare l'effetto dei parassiti sulle prestazioni del LNA. Dopo aver dimensionato i componenti del LNA, un trasformatore integrato è stato progettato con il simulatore elettromagnetico 3D HFSS di Ansoft<sup>™</sup>. Il LNA è stato realizzato mediante due stadi in cascata per raggiungere le specifiche di guadagno desiderate. Le simulazioni post-layout mostrano un guadagno di 10.02 dB a 60 GHz, ed un coefficiente di riflessione in ingresso di -16.84 dB a 61.45 GHz. Per minimizzare l'effetto dei pad sono stati inseriti degli induttori per risuonare con la capacità del pad alla frequenza di interesse. In fase di misura è stato riscontrato che la struttura risonante pad-induttore risuona fuori dal range di funzionamento del LNA. Simulazioni dei pad con simulatori elettromagnetici 3D (HFSS<sup>™</sup>) hanno confermato che l'estrattore di parassiti fallisce a frequenze così elevate, sovrastimando la capacità parassita del pad. Un re-design del circuito è in corso.

## Sommaire

L'activité de recherche scientifique effectuée dans le cadre de mon doctorat de sciences s'est déroulé dans le secteur du projet de circuits intégrés radiofrèquences, pour des systèmes ultra-wideband (UWB) et aux ondes millimetriques, et s'est articulée comme suit: (i) circuits intégrés radiofrèquences pour émetteur-récepteur basse puissance pour réseaux locaux wireless; (ii) radar UWB complètement intégré pour la surveillance cardio-pulmonaire en technologie 90nm CMOS; (iii) amplificateurs à faible bruit (LNA) à 60 GHz en technologie standard 65nm CMOS.

Dans les Chapitre 1 une évaluation théorique de la distance opérationnelle des Radio Frequency Identification Device (RFID) passifs et le projet d'un émetteurrécepteur à basse puissance pour applications ZigBee (IEEE 802.15.4) à 2.4 GHz en technologie 0.35µm Bi-CMOS de Austriamicrosystems sont rapportés. En plus, il est présenté le projet d'un oscillateur contrôlé en tension (VCO) à 5-6 GHz en technologie 0.35µm de Austriamicrosystems. En particulier, les inductances ont été réalisées par une nouvelle version de l'inductance actif "Boot-Strapped Inductor" (BSI). Enfin, il est présenté un nouveau circuit équivalent large bande, avec composantes discrets indépendants de la fréquence, decrivant le comportement des inducteurs à spirale intégrés sur silicium.

Le Chapitre 2 est dédiée à la réalisation d'un système radar UWB portable pour la sourveillance cardio-pulmonaire complètement intégré en technologie 90nm CMOS. En détails, sont rapportés l'étudie de faisabilité, l'analyse de système et les résultats des simulations de système. En plus, il est rapporté le projet des principaux blocs du capteur radar UWB (l'amplificateur à faible bruit (LNA), le générateur d'impulsions et le générateur de retard) en technologie 90nm CMOS de ST-Microelectronics. Les test-chip ont été réalisés et caractérisés expérimentalement. Les résultats des mesures sont rapportés ici et présentant une excellent corrélation avec les résultats des simulations post-layout.

Dans le Chapitre 3, enfin, le projet d'un amplificateur à faible bruit (LNA) à 60 GHz en technologie 65nm CMOS de ST-Microelectronics est rapporté. Le LNA exploite un nouvelle topologie pour obtenir l'adaptation d'impédance en entrée basée sur l'emploie d'un transformateur intégré, qui permet la réalisation de l'adaptation d'impédance sans l'application d'une dégénérescence de source, qu'il cause un abaissement du gain de l'amplificateur, chose pas désirée en particulier aux ondes millimetriques.

## Résumé

L'activité de recherche scientifique effectuée dans le cadre de mon doctorat de sciences s'est déroulé dans le secteur du projet de circuits intégrés radiofrèquences, pour des systèmes ultra-wideband (UWB) et aux ondes millimetriques, et s'est articulée comme suit: (i) circuits intégrés radiofrèquences pour émetteur-récepteur basse puissance pour réseaux locaux wireless; (ii) radar UWB complètement intégré pour la surveillance cardio-pulmonaire en tecnologie 90nm CMOS; (iii) amplificateurs à faible bruit (LNA) à 60 GHz en technologie standard 65nm CMOS.

Cette thèse de doctorat est organisée en trois chapitres, dont chacun traite un de ces thèmes sur énumérés affrontés pendant la recherche de doctorat.

#### Chapitre 1: Circuits Intégrés Radiofrèquences pour Émetteur-récepteur à Basse Puissance pour Réseaux Locaux Wireless

Depuis quelques années on observe un interêt croissant pour l'interesse en applications à bas débit, telles les Radio-Frequency Identification Device (RFID), et les réseaux de capteurs wireless. Avec lui elle a crû considérablement même la demande d'émetteur-récepteur à bas coût et bas consommation de puissance. Les systèmes RFID peuvent être classifiés dans passifs et actifs. Les dispositifs passifs peuvent être fabriqué à tres bas coûte, toutefois ils ont des range de fonctionnement de quelque mètre, qui dépend substantiellement de la puissance demandée du tag pour fonctionner. Une évaluation théorique de la distance opérationnelle de RFID passifs a été effectuée [OP1]. Étendre le range de fonctionnement des dispositifs RFID à des distances supérieures à une dizaine de mètres est possible en utilisant tag actifs.

Un émetteur-récepteur à basse consommation de puissance pour applications ZigBee (IEEE 802.15.4) à 2.4 GHz a été implémenté en technologie 0.35µm Bi-CMOS d'Austriamicrosystems et est présenté en [OP1, OP4]. Le récepteur, qui consiste en un LNA et un mélangeur I/Q, présente un facteur de bruit (NF) de 8.7 dB, un gain en tension de 26 dB, un point de intercepte de troisième ordre (IIP3) de -13 dBm, avec une consommation de puissance de 8.6 mW. L'émetteur comporte un amplificateur de puissance à deux étages (preamplificateur en classe A suivi d'un amplificateur en classe C) et deux mélangeurs doublement équilibrés à cellule de Gilbert. Il fournit une puissance de sortie de 6 dBm avec une consommée de puissance de 16 mW.

De même l'interêt pour des liens à hauts débit, telle les Wireless Local Area Network (WLAN), il a considérablement crû depuis quelques années. Un oscillateur contrôlé en tension (VCO) (que typiquement représente le bloc le plus critique d'une chaine Tx/Rx) à 5-6 GHz, a été realisé en technologie 0.35µm d'Austriamicrosystems, et est présenté en [OP3, OP7]. Pour pallier aux limites des inductances sur silicium, une nouvelle approche CMOS de l'inducteur actif à haut facteur de mérite "Boot-Strapped Inductor" (BSI) [OP6]a été mise en place. Cette nouvelle version de BSI CMOS est employée à la place des inductances du filtre self-résonant du VCO. Un modèle petit signale du nouveau BSI a été developpé avec MATLAB<sup>TM</sup>, pour pouvoir efficacement dimensionner et optimiser l'inducteur actif.

Enfin, un nouveau modèle équivalent large bande, à composantes discrets indépendants de la fréquence, a été développé pour décrire le comportement d'inducteurs à spirale intégrés sur silicium et présenté en [OP5]. Ce nouveau modèle est capable de modèliser le comportement d'une inductance intégrée en présence ou moins d'un plan de masse au dessous (PGS). Les éléments RLC du circuit ont été extraits directement des paramètres S de l'inductance. Deux different procédures de correlation entre simulations et mesures sont ici proposés afin de dimensionner le modèle.

#### Chapitre 2: Radar UWB pour la Surveillance Cardio-pulmonaire en Technologie 90nm CMOS

En 2002 le Federal Communication Commission (FCC) a approuvé l'arrivée sur le marché de dispositifs qui exploitent un nouveau standard de communication qui emploie des signaux Ultra Large Bande (UWB). Pour les systèmes UWB elle a été allouée la bande de frequences 3.1-10.6 GHz, pour la première fois en mode pas exclusive. Le concept à la base de la technologie UWB est celui d'engendrer, transmettre et recevoir des impulsions radio-fréquence de durée temporelle tres brève (de quelque dizaines de picosecondes à quelque dizaines de nanosecondes). Le signale UWB présent par conséquent un spectre en fréquence très vaste (plusieurs GigaHertz) et une densité d'énergie faible. Parmi les multiples applications pour lesquelles les systèmes UWB ont été pensés, une des plus prometteur est la imagerie medicale.

Contrairement aux techniques traditionnelles pour l'observation de l'activité cardiaque, comme le l'électrocardiogramme ou l'emploi de transducteurs à ultrasons, les systèmes radar à micro-ondes permettent la surveillance du muscle cardiaque de manière peu envahissante, puisq'ils ne necessitent pas l'application de capteurs en contacte avec le corps du patient. D'autre part, en controlant ansi directement la mécanique du muscle cardiaque, cette technique permet de prévenir de nombreuses pathologies cardiaques non décelables au travers de la seule observation de l'activité electrique du coeur.

Parce que la technologie CMOS est la plus adaptée au marché de masse RF pour ses qualités d'intégration et de faible coût, le capteur UWB developpé ici, a été implémenté en technologie CMOS de longueur de grille 90 nm.

À ce point elle a été développée l'idée d'un système endossable de nouvelle génération pour la surveillance constant de les fréquences cardiaque et respiratoire, présentée en [OP2, OP8, OP9, OP11, OP12, OP14, OP15, OP16, OP17]. Le système est constitué d'un capteur radar UWB et d'une interface radio lowpower (IEEE 802.15.4 ZigBee), qui réalise l'acquisition des données provenants du

### RÉSUMÉ

capteur et les envoyer à une unité éloignée de traitment des signaux. Le topologie de radars la plus prometteuses pour ce type d'application est celle des radars à impulsions. Elles présente en effect une architecture simple permettant de réduir fortment la consommation de la partie radio.

En ce qui concerne le projet du système radar, un étudie du canal dans lequel l'impulsion devra se propager a été effectuée [OP2, OP9]. En tenant compte des divers tissus du corps humain et des leurs propriétés diélectriques, il a été développé un modèle de canal en function de la fréquence, pour pouvoir effectuer les analyses au niveau système.

Des simulations préliminaires ont permis de déterminer dans la topologie de type correlatore le topologie de récepteur guarantissant un rapport signal-bruit en sortie du récepteur et une sensibilité à des petits déplacements du muscle cardiaque maximum. Des analyses de système ont étés effectuée pour répartir les caractéristiques de système parmi les divers blocs du radar UWB. Un modèle du canal, qui décrit soit les pertes en fréquence, soit le mouvement du muscle cardiaque, a été realisé de façon à pouvoir être inséré dans le simulateur Ptolemy en Agilent ADS2005A<sup>™</sup>. Des mesures de canal ont été effectuées afin de vérifier la validité du modèle proposé [OP2, OP15, OP16]. Les résultats montrent des atténuations très proches du modèle proposé et d'autres travaux publiés en littérature. Le système entier a été simulé, et les résultats des simulations système ont montré la faisabilité du projet [OP2, OP8, OP9, OP11, OP12, OP14].

Les principaux blocs du capteur radar UWB (amplificateur à faible bruit (LNA), générateur d'impulsions et générateur de retard) ont été réalisés en technologie 90nm CMOS de ST-Microelectronics. Les circuits ont étés caractérisés sur puce en utilisant un banc de test sous pointes. Le LNA est constituée d'un étage grille commune, qui réalise l'adaptation d'entrée large bande, puis deux étages source commune pour l'amplification en tension. Les mesures montrent un gain de 22.7 dB à 5.2 GHz, une bande à 3-dB environ de 5 GHz, un coefficient de réflexion en entrée inférieure à -10.5 dB sur toute la bande, et un point de compression à 1-dB de -19.7 dBm. La chiffre de bruit est proche de 5.5 dB sur tout la bande 3.1-10.6 GHz. La consommation de puissance est de 34.8 mW (alimentation 1.2 V) [OP15, OP16]. Le générateur d'impulsions UWB, activé du front négatif de un signal de commande fourni par un micro-contróleur, engendre une impulsion monocycle. Il exploite le principe des formateurs d'ondes non linéaires. Des mesures on-chip montrent que le générateur d'impulsions produit une impulsion avec un durée temporelle de 430 ps et une amplitude pic-pic de 660 mV. La consommation de puissance est 19.8 mW (alimentations 1.2 V) [OP10, OP16]. Le generator de retard présente un retard programmabile de 1 à 3 ns commandé par le front de descente de un signal numerique, pour génération tardée (d'un retard pair au temps de vol de l'impulsion du radar au coeur et de nouveau au radar) d'une réplique local (sur puce) de l'impulsion transmise pour évaluer la corrélation entre celle-ci et l'écho reçu provenant du muscle cardiaque. Le retard est programmabile au moyen de 5 bit [OP10, OP16].

L'intégration totale du système radar a été réalisé en technologie 90nm CMOS de ST-Microelectronics et le layout a été envoyé en fonderie.

# Chapitre 3: Amplificateur à Faible Bruit (LNA) à 60 GHz en Technologie Standard 65nm CMOS

Un amplificateur à faible bruit (LNA) à 60 GHz en technologie 65nm CMOS de ST-Microelectronics a été conçu au sein du laboratoire IMS (Laboratoire de l'Intégration du Matériau au Système) avec siège à Bordeaux (France), et présenté en [OP13].

Une nouvelle technique d'adaptation d'entrée basée sur l'utilisation d'un transformateur a été mise au point. Le primaire, de ce transformateur, est en serie avec la grille du transistor d'entrée du cascode, le secondaire est relié au drain de ce dernier. Cette approche permet de s'affranchir de la technique traditionelle de degenerescence inductive, limitant fortment le gain dans le domaine mm-waves.

Il a été développé un modèle du transistor dans le simulateur ADS de Agilent<sup>TM</sup> pour analyser l'effet des parasites sur les caracteristiques du LNA. Après avoir dimensionné les composants, un transformateur intégré a été dessiné avec le simulateur électromagnétique 3D HFSS de Ansoft<sup>TM</sup>. Le LNA final comporte deux étages. Les simulations post-layout montrent un gain de 10.02 dB à 60 GHz, et un coefficient de réflexion en entrée de -16.84 dB à 61.45 GHz. Pour minimiser l'effet des pad des inductances ont été insérées pour résonner avec la capacité du pad a 60 GHz. Lors de mesures, il s'est avéré que la resonnance du couple pad/inductance masque le comportement du LNA en aval. Nous n'avons donc pas pu valider les simulations post-layout et procedons actuallment à un re-design du circuit.

### Abstract

The research activity carried out during this PhD consists on the design of radiofrequency integrated circuits, for ultra-wideband (UWB) and millimeter-wave systems, and covers the following topics: (i) radio-frequency integrated circuits for low-power transceivers for wireless local networks; (ii) fully integrated UWB radar for cardio-pulmonary monitoring in 90nm CMOS technology; (iii) 60-GHz low noise amplifier (LNA) in 65nm CMOS technology.

In Chapter 1 a qualitative analysis on the communication range of passive Radio-Frequency Identification Devices (RFID), and the design of a 2.4 GHz fully integrated low-power RF transceiver front-end in a low-cost 0.35 µm SiGe Bi-CMOS technology by Austriamicrosystems are reported. Furthermore, a novel fully integrated 5-6 GHz CMOS LC tank VCO designed in a 0.35 µm standard CMOS technology is presented. Particularly, the LC tanks have been implemented by introducing a new version of the CMOS Boot-Strapped Inductor (BSI) circuit. Finally, in Chapter 1 a new wide-band frequency-independent equivalent circuit single-Π model for on-chip spiral inductors is presented.

In Chapter 2 the research activity on a new system-on-a-chip radar sensor for next generation wearable wireless interfaces applied to the human health-care and safeguard is described. In detail, the feasibility study, system analysis and the results of system simulation have been reported. The main building blocks of this UWB radar have been realized in 90nm CMOS technology by ST-Microelectronics. The design of the main building blocks of the UWB (3.1-10.6 GHz) radar sensor (the LNA, the monocycle pulse generator and the digitally programmable delay generator) in 90nm CMOS technology by ST-Microelectronics is reported. The test-chips have been realized and their performance have been measured. The measurement results show a good agreement with post-layout simulations.

Finally, in Chapter 3, the design of a 60-GHz LNA in 65nm bulk CMOS technology is reported. The LNA exploits a novel topology to obtain the integrated input impedance matching based on an integrated transformer. This technique does not require any inductive source (emitter) degeneration, which decreases the gain at high frequency, especially in the range of the millimeter waves.

## Preface

The opportunity offered by the modern silicon technologies (the transistors of the standard 65nm CMOS technology have cut-off frequencies up to 200 GHz) allows us to realize highly miniaturized, low cost and low power systems-on-a-chip (SoaC), operating up to the millimeter waves, suitable for mass-market applications.

The research activity carried out during the PhD has been focused on the design of radio-frequency transceivers, from several GigaHertz up to the millimeterwaves, for narrow-band and ultra-wideband applications, on standard silicon technologies. All the aspects of the design, from the study of the applications, the system analyses and simulations, to the circuit design, realization and measurements have been covered.

This PhD thesis is organized in three Chapters, whose each one concerns a specific application and design investigated during the PhD research. The presentation order follows the thesis schedule. The research theme regarding the design of an ultra-wideband (UWB) radar for cardio-pulmonary monitoring in 90nm CMOS technology, described in Chapter 2, has interested most of the research period.

The rising interest in low-data rate applications, such as Radio-Frequency Identification Devices (RFID) and wireless sensor networks, has increased the demand of low-cost and low-power wireless devices. On the other side, the demand for high data-rate links in spectrum regions at higher frequencies, as the 5-6 GHz band for wireless local area network (WLAN) multi-standard applications, has increased in the last years as well. Chapter 1 deals with the design of radio-frequency integrated circuits for 2.4-GHz ZigBee applications and 5-GHz WLAN applications.

In February 2002 the Federal Communications Commission (FCC) gave the permission for the marketing and operation of a new class of products incorporating ultra-wide-band (UWB) technology in the 3.1-10.6 GHz band. One of the most promising class of applications of the UWB systems consists of the medical imaging. Chapter 2 deals with the study and design of an innovative wearable wireless interface for cardio-pulmonary monitoring based on a fully integrated innovative UWB radar in 90nm CMOS technology.

In the last few years, the interest in the 60 GHz radio-frequency band has rapidly grown, since the great bandwidth available allows the implementation of very high (Gigabit/s) data-rate communication systems. Chapter 3 investigates the design of a 60-GHz Low Noise Amplifier (LNA) in a 65nm bulk CMOS technology by ST-Microelectronics, exploiting a new approach of input matching without inductive source degeneration, based on the employment of an integrated trans-

### former.

The original contributions of this PhD thesis to the improvement of the state of the art are referred with the label OP (e.g. [OP1]), and reported in the List of Publications.

xviii

## Contents

| Ackno                                                                                    | wledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | i                                                               |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Somm                                                                                     | ario                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | iii                                                             |

| Riassu                                                                                   | nto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{v}$                                                    |

| Somm                                                                                     | aire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ix                                                              |

| Résun                                                                                    | né                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | xi                                                              |

| Abstra                                                                                   | act                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | XV                                                              |

| Prefac                                                                                   | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xvii                                                            |

| Conte                                                                                    | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xix                                                             |

| <ol> <li>Sho</li> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>1.4</li> <li>1.5</li> </ol> | ort-range Wireless LAN         Introduction         RFID: Active vs. Passive and a Low-Power Transceiver for IEEE         802.15.4 (ZigBee) Standard         1.2.1 Communication Range of Backscattered RFID Systems         1.2.2 Low-Power Transceiver for IEEE 802.15.4 (ZigBee) Standard         5-6 GHz LC-Active VCO for CMOS RF Transceivers         1.3.1 CMOS Boot-Strapped Inductor: The New Circuit         1.3.2 5-6 GHz BSI Based VCO Design         Wide-Band Frequency-Independent Equivalent Circuit Model for         1.4.1 New equivalent Wideband Circuit Model         1.4.2 Model Validation and Results | 1<br>1<br>2<br>1<br>3<br>12<br>12<br>15<br>18<br>20<br>21<br>23 |

| 2 UW<br>2.1<br>2.2<br>2.3                                                                | /B Radar for Cardio-Pulmonary Monitoring         Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>25</b><br>25<br>26<br>27                                     |

#### CONTENTS

|     | 2.4            | Feasibility Study of the System-on-a-Chip UWB Radar for the<br>Heart Monitoring                                        | 29<br>30<br>33       |

|-----|----------------|------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | 2.5            | 2.4.3       CAD System Simulations                                                                                     | 34<br>37<br>38<br>44 |

|     | 2.6            | 2.5.3 5-bit Digitally Programmable 1-3 ns Delay Generator<br>System-on-a-Chip UWB Radar for The Cardio-Pulmonary Moni- | 52                   |

|     | 2.7            | toring in 90nm CMOS Technology                                                                                         | $56 \\ 56$           |

| 3   | 60-0           | GHz Low Noise Amplifier                                                                                                | 59                   |

|     | 3.1            | Introduction                                                                                                           | 59                   |

|     | 3.2            | A Novel Technique to Achieve the Input Matching of a Low Noise                                                         | -                    |

|     |                | Amplifier                                                                                                              | 59                   |

|     |                | 3.2.1 Calculation of The Input Impedance of the Transformer-<br>Based LNA                                              | 62                   |

|     |                | 3.2.2 Design Criteria                                                                                                  | 65                   |

|     | 3.3            | LNA Design at 60 GHz                                                                                                   | 65                   |

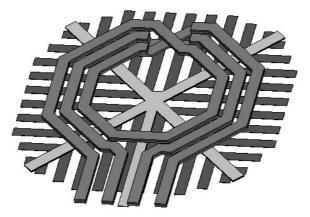

|     | 0.0            | 3.3.1 Transformer Design                                                                                               | 65                   |

|     |                | 3.3.2 LNA Design                                                                                                       | 67                   |

|     | 3.4            | Post Layout Simulations                                                                                                | 68                   |

|     | 3.5            | Measurements                                                                                                           | 70                   |

|     | 3.6            | Remarks                                                                                                                | 71                   |

| Co  | onclu          | sions                                                                                                                  | 73                   |

| Li  | st of          | Publications                                                                                                           | 75                   |

| Bi  | bliog          | raphy                                                                                                                  | 77                   |

| Li  | st of          | Symbols and Abbreviations                                                                                              | 85                   |

| Li  | st of          | Figures                                                                                                                | 87                   |

| Lis | st of          | Tables                                                                                                                 | 91                   |

| In  | $\mathbf{dex}$ |                                                                                                                        | 93                   |

XX

### Chapter 1

## Short-range Wireless LAN

### 1.1 Introduction

In the last years the interest in low-data rate applications, as radio-frequency identification devices (RFID) and wireless sensor networks has rapidly grown. As a consequence, the demand of low-cost and low-power wireless transceivers has hugely increased. On the other side, the demand for high data-rate links in spectrum regions at higher frequencies, as the 5-6 GHz band for wireless local area network (WLAN) multi-standard applications, has increased as well. In this chapter the design of some building blocks of radio-frequency transceivers for 2.4 GHz ZigBee and 5-GHz WLAN applications in 0.35µm Bi-CMOS technology by Austriamicrosystems are presented.

In order to realize portable wireless devices, a primary requirement for active transponders (tags) is the reduction of the power consumption in order to reasonably extend the battery lifetime.

After presenting the capabilities of passive and active RFID, a 2.4 GHz ultra low-power RF transceiver front-end for low data-rate wireless links compliant with IEEE 802.15.4 standard (ZigBee) [1, 2] applications designed in a low-cost 0.35µm Bi-CMOS technology is presented. The design criteria for an optimal trade-off between linearity and power consumption are reported.

Then, the design of a 5-6 GHz voltage controlled oscillator (VCO) employing a new version of the Boot-Strapped Inductor (BSI, an high-Q active inductor) is presented. Finally, a wide-band equivalent circuit single- $\Pi$  model for on-chip spiral inductors employed in this design is presented.

### 1.2 RFID: Active vs. Passive and a Low-Power Transceiver for IEEE 802.15.4 (ZigBee) Standard

The RFID systems can be classified into two main groups: the passive and the active transponders (tags) [3]. The active RFID tags are battery assisted, whereas the passive tags are not. The passive tags draw the power supply by rectifying the incident radiofrequency (RF) power emitted by the reader device.

Passive RFID tags are very cheap, but they need to be very close to the reader. For a passive RFID tag, the maximum operating distance from the reader is limited to a few meters because of the low power level which can be transmitted in the 2.4 GHz ISM band (4 W in the United States of America; 4 W in-building only or 0.5 W without any restriction in Europe [4]). Unlike passive tags, active tags can operate at distances up to tens of meters, making them an obliged choice for many applications.

#### 1.2.1 Communication Range of Backscattered RFID Systems

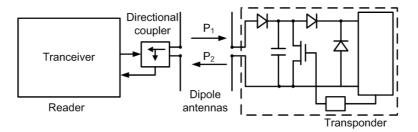

The operating principle of a typical passive RFID system, which operates in the UHF or microwave range is shown in Fig. 1.1.

Figure 1.1: RFID backscattered system: scheme of principle.

These systems exploit the backscattering modulation. At first, the reader interrogates all the tags (transponders) in its operating range. During this time, it sends a radio-frequency signal (with power  $P_1$ ) to the transponders. A part of the incident radio-frequency signal is rectified by the tag in order to obtain the power supply for its circuitry. In a second part of the communication protocol, the reader activates the communication only with the tag which corresponds to a specific code. During this time, the tag draws its power supply from a part of the energy irradiated by the reader in order to activate the tag circuitry which modulates the antenna impedance. Thus, the signal backscattered to the reader contains the information contained into the tag.

A simple theoretical model has been developed and reported in [OP1], and is herein summarized. The power density S at a distance r (range) from the antenna of the reader device is given by

$$S\left(r\right) = \frac{EIRP}{4\pi r^2} \tag{1.1}$$

where, EIRP is the effective isotropic radiated power emitted by the reader. The effective area of an antenna is expressed by:

$$A_e = \frac{\lambda_0^2}{4\pi} G \tag{1.2}$$

where,  $\lambda_0$  is the wavelength of the RF carrier and G is the antenna gain. An RFID system operates properly if the RF-to-DC power converted by the tag is higher or equal than its minimum power supply requirement  $(P_{TAG})$ , typically in the order

# 1.2. RFID: ACTIVE VS. PASSIVE AND A LOW-POWER TRANSCEIVER FOR IEEE 802.15.4 (ZIGBEE) STANDARD

of some tens of mW. This means that,

$$P_{TAG} \le \frac{EIRP}{4\pi r^2} \frac{\lambda_0^2}{4\pi} G_{TAG} \tag{1.3}$$

where  $G_{TAG}$  represents the antenna gain of the tag. Then, it derives that

$$r_{Reader-to-Tag} \le \frac{\lambda_0}{4\pi} \sqrt{\frac{EIRP \ G_{TAG}}{P_{TAG}}} \tag{1.4}$$

which shows the upper limit of the communication range from the reader to the tag. In spite of that, limitations on the reverse communication path from the tag to the reader have to be considered. In fact, the RFID system operates properly if the power backscattered to the reader is higher than its sensitivity ( $S_{READER}$ ), which is typically in the range from -110 to -70 dBm), according to the following expression

$$\frac{\lambda_0^2}{4\pi}G_{READER}\frac{1}{4\pi r^2}\frac{EIRP}{4\pi r^2}\frac{\lambda_0^2}{4\pi}G_{TAG} \ge S_{READER} \tag{1.5}$$

From (1.5) it results that,

$$r_{Tag-to-Reader} \le \frac{\lambda_0}{4\pi} \sqrt[4]{\frac{EIRP \ G_{READER} \ G_{TAG}}{S_{READER}}}$$

(1.6)

Finally, the theoretical range of a RFID system is given by the minimum between the two ranges evaluated with (1.4) and (1.6),

$$r = \min\left\{r_{Reader-to-Tag}, r_{Tag-to-Reader}\right\}$$

(1.7)

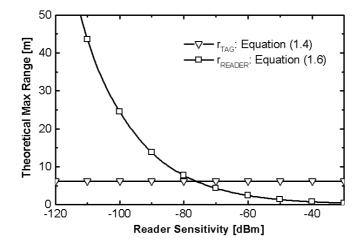

The theoretical maximum operating range versus the reader sensitivity are shown in Fig. 1.2.

These curves have been evaluated by (1.4) and (1.6), in the case of a tag operating at 2.45 GHz with  $P_{TAG}$  equal to 10 µW and  $G_{TAG}$  equal to 0 dB, and a 4 W EIRP reader with an antenna gain equal to 0 dB. To be noted that for lower values of the reader sensitivity, the maximum operating range is due to the limit introduced by (1.4), whereas for higher values of the reader sensitivity (> -75dBm) the limit is given by (1.6).

The maximum operating range of several passive transponder presented in literature have been compared with those obtained with the previously presented equations in [OP1]. The results of such comparison is shown Table 1.1. It can be noted the good agreement between the measured and the expected theoretical maximum range. However, the maximum measured range is slightly lower than that theoretical for all the cases, as we expected since the theoretical prediction does not take into account the electromagnetic complexity of the surrounding environment.

### 1.2.2 Low-Power Transceiver for IEEE 802.15.4 (ZigBee) Standard

A fully integrated and low-power RF transceiver has been designed in 0.35µm Bi-CMOS technology by Austriamicrosystems and presented in [OP1, OP4]. The proposed transceiver exploits a direct-conversion topology.

3

The direct-conversion I/Q receiver has been designed by using the available bipolar transistors in order to reduce the receiver noise figure and avoid the problems concerning the flicker noise corner frequency.

The direct up-conversion transmitter has been designed with the minimum channel-length n-MOS RF transistor. As far as the transmitter is concerned, the issue of the local oscillator pulling is mitigated by the low output power required for ZigBee applications (0 dBm).

Details on the derivation of the specifications of the receiver and the transmitters are reported in [OP1].

#### **Receiver Design**

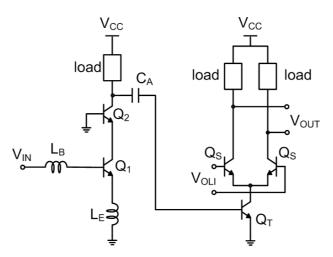

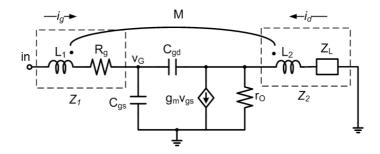

The most widespread topology for the realization of integrated radio-frequency receivers [8, 9] on silicon is shown in Fig. 1.3. The low noise amplifier (LNA) shown in Fig. 1.3 is typically implemented by a transconductive cascode stage.

By a properly sizing of the transistor  $Q_1$  and the inductors  $L_E$  and  $L_B$ , an almost perfect input integrated matching is realized, which allows us to simultaneously reach the maximum power transfer to the receiver and the minimum noise figure performance [10]. The input integrated matching technique imposes a constraint on the current drained by the LNA. In [11], it is shown that by adding a properly sized capacitance in parallel with  $C_{BE}$  of the transistor  $Q_1$ , then the input integrated matching can be achieved with reduced power consumption. The receiver shown in Fig. 1.3 provides a high gain, but the transconductive stage of the mixer introduces an additional non-linearity in excess to that introduced by the LNA. Thus, the increase of the linearity performance of such a receiver topol-

Figure 1.2: The theoretical maximum operating range vs. Reader sensitivity calculated by Equations (1.4) and (1.6), for the case of a tag operating at 2.45 GHz with  $P_{TAG}$ equal to 10 µW and  $G_{TAG}$  equal to 0 dB, and a 4 W EIRP reader with an antenna gain equal to 0 dB. The theoretical maximum operationg range is done by the minimum between the two curves.

Table 1.1: Comparison Between Experimental and Theoretical Range of Passive Tranceivers

| Work | Frequency | EIRP | $P_{TAG}$ | Theoretical Range | Experimental Range |  |

|------|-----------|------|-----------|-------------------|--------------------|--|

|      | (MHz)     |      | $[\mu W]$ | [m]               | [m]                |  |

| [5]  | 915       | 4W   | 16.7      | 12.05             | 9.25               |  |

| [5]  | 2450      | 4W   | 50        | 2.75              | 2.6                |  |

| [6]  | 915       | 4W   | 10        | 16.5              | 11                 |  |

| [7]  | 2450      | 4W   | 2.7       | 15                | 12                 |  |

Figure 1.3: The most commonly employed receiver front-end topology. The LNA is implemented by means of an emitter degenerated cascode transconductive stage and the mixer is implemented with a typical Gilbert cell.

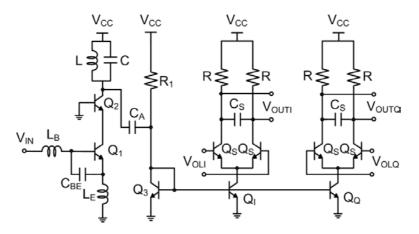

ogy requires an increase of the mixer bias current. A direct-conversion receiver topology [12] is proposed for the realization of a low-power receiver front-end for ZigBee based standard applications. The simplified schematic is shown in Fig. 1.4.

The LNA is implemented by means of a cascode transconductive stage. The inductances  $L_E$  and  $L_B$  realize the input integrated matching, whereas the additional capacitance  $C_{BE}$  reduces the power consumption of the LNA [11]. The LC filter resonates at the operating frequency. The small-signal current provided by the LNA flows directly into the transistor  $Q_3$ , which mirrors (according to the transistor areas ratio) its current into the transistors of the transconductive stage of the mixer ( $Q_I$  and  $Q_Q$ ). Since this connection between LNA and mixer stages does not introduce ideally any non-linearity, a small bias current for the transistor  $Q_3$  is allowed. As a consequence,  $R_1$  is in the order of K $\Omega$  and then it does not impair the quality factor of the LC filter. In this way, the output current of the LNA can flow through the low-impedance path offered by the differential resistance of the transistor (diode)  $Q_3$ , and then into the transistors  $Q_I$  and  $Q_Q$

Figure 1.4: Simplified schematic of the direct down-conversion I/Q receiver front-end. The LNA output drives the two subsequent I/Q mixers by means of a current mirror, which amplifies the signal provided by the LNA without introducing significant distortions.  $C_A$  is a DC blocking capacitance.

of mixers.

To be noted that in a traditional design approach, the LC filter is not in parallel with any other components [10, 11], especially resistors, since they have a heavy impact on its quality factor degradation. Moreover, it is worth mentioning that the linearity benefits of the current mirror are well known in literature [13], but the technique is not used in the range of the radio-frequencies. In fact, in [14], it has been exploited at low frequencies for up-conversion operations. In addition, unlike the topology of Fig. 1.4, in [14] the current mirror is driven by an additional emitter follower stage, which introduces an extra degradation of the linearity performance that can be mitigated only by increasing the power consumption.

The benefits offered by the circuit of Fig. 1.4 in terms of linearity performance can be shown by a simplified circuit analysis reported hereinafter. If we consider the signal  $i_{RF}(t) = i_{RFM} \cos(\omega_0 t)$  at the input of the LNA, then the small signalcurrent in  $Q_3$  can be written as follows

$$i_{C3}(t) \approx \beta_{ac} \, i_{RF}(t) \tag{1.8}$$

where  $\beta_{ac}$  is the current gain of the LNA (in the order of ten in the radio-frequency range). The current  $I_{CI}(t)$  ( $I_{CQ}(t)$ ) into the RF trasconductive stage of the mixer is proportional to the exponential of voltage  $V_{BE}(t)$ , and then the small signal current is proportional to the small signal output current provided by the LNA

$$i_{CI}(t) \propto i_{C3}(t) \propto \beta_{ac} \, i_{RFM} \cos(\omega_0 t) \tag{1.9}$$

It can be noted that the non-linearities of the overall front-end are mainly due by those introduced by the LNA. Further aspects regarding the linearity have already been investigated in [15]. Moreover, the current mirror can be used as a

# 1.2. RFID: ACTIVE VS. PASSIVE AND A LOW-POWER TRANSCEIVER FOR IEEE 802.15.4 (ZIGBEE) STANDARD

current amplifier as well: indeed, if k is the area ratio between the transistors  $Q_I$   $(Q_Q)$  and  $Q_3$ , the value of  $i_{CI}$   $(i_{CQ})$  is k-times that of  $i_{C3}$ . Finally, for a proper design of the mixer, three parameters have been taken into account: i) the bias current  $I_{C30}$ , ii) the area of the transistor  $Q_3$  and iii) the ratio k between the area of the transistors  $Q_I$   $(Q_Q)$  and  $Q_3$ . In order to have a linear behaviour of  $Q_3$ , the peak value of the signal current  $(i_{C3M})$  has to be lower than its bias current  $(I_{C30})$ . Therefore, in order to avoid current clipping (i.e. distortion),  $I_{C30}$  has to be

$$I_{C30} \ge \beta_{ac} \sqrt{\frac{P_{IN}}{2R_{IN}}} \tag{1.10}$$

where,  $P_{IN}$  is the maximum power at the input of the LNA and  $R_{IN}$  is its input impedance (resistive as in this case with the input integrated matching to the gatesource capacitance). The transistors area ratio k is chosen in order to achieve a good trade-off between the gain and power consumption. The down-conversion voltage gain  $(A_v)$  can be expressed as follows:

$$A_v = \frac{\beta_{ac} k_\pi^2 R}{2R_{IN}} = \frac{g_m kR}{\pi} \tag{1.11}$$

(1.11) shows that the down-conversion gain of the proposed receiver increases with higher values of k. However, a higher k causes an increasing of the mixer bias current as well. Finally, the area of  $Q_3$  has to be set, in order to reach the best trade-off between gain and noise figure. These criteria have been applied for the case of IEEE 802.15.4 (Zigbee) standard applications at 2.45 GHz.

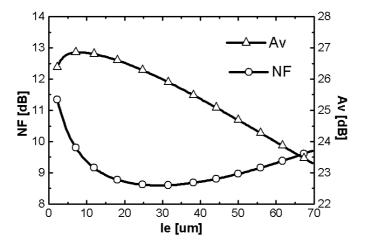

The circuit has been designed by using the SiGe HBTs available with the 0.35  $\mu$ m Bi-CMOS process by Austriamicrosystems. The simulation results have been carried out by the SpectreRF<sup>TM</sup> circuit simulator. As for the LNA, with a bias current budget of 1.3 mA and an emitter area of  $Q_1$  equal to 8  $\mu$ m<sup>2</sup>, it results an input referred 1-dB compression point (ICP<sub>1dB</sub>) of -20 dBm and a NFmin of 1.8 dB.  $C_{BE}$  is sized to obtain a NF very close to the NFmin with an input integrated matching to a 50 $\Omega$  antenna, according to [11]. The bias current of  $Q_3$  has been set equal to 700  $\mu$ A. The current mirror gain (k) has been chosen equal to two. The voltage gain ( $A_V$ ) and NF vs. the emitter length (the emitter width is fixed to 0.4  $\mu$ m) are shown in Fig. 1.5.

By choosing an emitter length equal to 27 µm, a good trade-off between the NF and the voltage gain  $A_V$  equal to 26 dB ( $R_{load}$  is 400 $\Omega$ ,  $P_{AOL}$  is -10 dBm on a gate-source capacitance resistance of 50 $\Omega$ ) is obtained. The overall NF is reported in Fig. 1.6.

To be noted that the corner frequency of the flicker noise is quite lower than 10 KHz. A summary of the receiver performance and a comparison with the most representative works presented in literature are reported in Table 1.2. The solution herein reported represents one of the best performance tradeoffs between overall receiver performance and power consumption, among all those previously presented in the literature (for sake of clarity, our performance are obtained by simulations, while the performance of the other works reported in Table 1.2 are obtained by measurements).

Figure 1.5: NF and  $A_V$  vs.  $Q_3$  emitter length. The minimum of NF is obtained for an emitter length of 27 µm, with an associated  $A_v$  of 26 dB.

Figure 1.6: Noise Figure (NF) of the overall receiver vs. frequency.

| Work      | Vork Tech        |     | $A_v$ | NF   | $P_D$ | $IIP_3$ |

|-----------|------------------|-----|-------|------|-------|---------|

|           |                  | [V] | [dB]  | [dB] | [mW]  | [dBm]   |

| [9]       | 0.35µm CMOS      | 1   | 16    | 29   | 6     | -18     |

| [16]      | $0.25\mu m$ CMOS | 2.5 | 50    | 6    | 10    | -16     |

| [17]      | 0.18µm CMOS      | 1.8 | 32    | 6.5  | 8.8   | -9      |

| [18]      | 0.18µm CMOS      | 1.8 | 30    | -    | 5.4   | -4      |

| This work | SiGe*            | 1.8 | 26    | 8.7  | 8.6   | -13     |

Table 1.2: Summary of the Receiver Performance and Comparison with Previous Works

#### \*0.35µm Bi-CMOS

#### **Transmitter Design**

The IEEE 802.15.4 standard states that the devices operate with a typical output power equal to 1 mW. This power is very low, so a direct up-conversion transmitter architecture may be used without suffering of local oscillator pulling. The radio-frequency carrier is modulated with a constant envelope offset QPSK modulation. This fact allows the employment of a high-efficiency non-linear amplifier, such as class-C amplifiers.

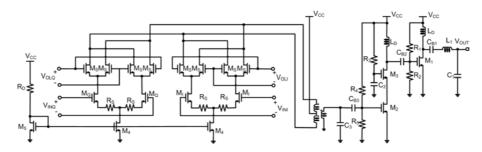

The proposed I/Q direct up-conversion transmitter consists of two double balanced mixers realized by a Gilbert cell mixer quad (I and Q channels) and a two-stage power amplifier (PA). The circuits have been designed by using the multi-finger n-MOS transistors (with the minimum channel length) of the 0.35 µm Bi-CMOS process, which, unlike the bipolar counterparts, allow us to not incur in extra dc power consumption due to the current drained from their bases. The integrated square spiral inductors and balun have been designed by means of the  $2D\frac{1}{2}$  simulators (Momentum<sup>TM</sup>, EM Sight<sup>TM</sup>). Schematic and post-layout simulations have been carried out within Cadence Design Systems and Advanced Design System (ADS). The simplified schematic of the overall transmitter is shown in Fig. 1.7.

Figure 1.7: Schematic of the direct up-conversion I/Q transmitter front-end.

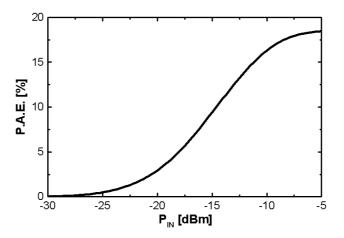

The power amplifier is realized by a class-A pre-amplifier (driver stage) that drives a high-efficiency class-C amplifier (power stage). The circuit has been designed in order to provide an overall output power level equal to +6 dBm, taking into account the possible reductions of performance due to the unpredictable losses caused by process parameters variations. As first design step, the class-C amplifier has been designed. For a class-C amplifier a higher efficiency can be achieved by reducing the conduction angle. On the other hand, this reduction also causes a reduction of the gain, so that a tradeoff is required. For the circuit solution herein proposed the transmitter has been designed for a conduction angle of 150 degrees, which has allowed the achievement of a good tradeoff between power efficiency and gain. Then, the optimal load impedance of the amplifier for the maximum power delivering has been found by performing a load-pull analysis both with Cadence<sup>TM</sup> and Advanced Design System<sup>™</sup>, by considering a standard gate-source capacitance impedance  $(50\Omega)$  at the input of the class-C amplifier. The output matching network  $(L_1 \text{ is } 210 \text{ pH}, C_1 \text{ is } 5 \text{ pF})$  realizes the impedance matching between the power stage and the load resistance. Large Signal S-Parameter simulations have shown a drain efficiency  $(\eta)$  of 25% and a power-added efficiency (PAE) of and 22% at 6 dBm, where the drain efficiency and the power-added efficiency are defined as follows

$$\eta = \frac{P_{OUT,RF}}{P_{DC}} \tag{1.12}$$

$$PAE = \frac{P_{OUT,RF} - P_{IN}}{P_{DC}} \tag{1.13}$$

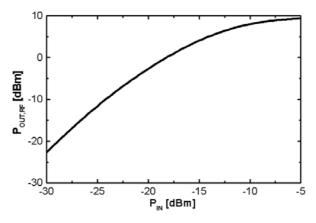

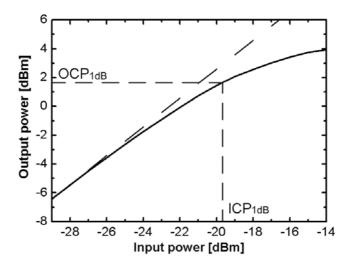

$(P_{OUT,RF}$  is the power of the radio-frequency component of the output signal,  $P_{DC}$  is the DC power consumption and  $P_{IN}$  is the radio-frequency power at the input of the transmitter). The pre-amplifier has been implemented by a class-A amplifier (implemented by using a cascode stage), which allows us to properly set in a reliable way the circulation angle of the class-C. Moreover, this solution offers an almost constant input impedance, which represents a fundamental requisite for an efficient transformer-based power delivering from the output of the mixer stage [19]. The transistors of the driver stage have a gate width of 200 µm. The driver stage provides a power gain of 14 dB, an ICP<sub>1dB</sub> nearly equal to -15 dBm and an OCP<sub>1dB</sub> very close to 2 dBm. The circuit drains a current of 5.8 mA from a 1.8 V power supply. The input-output characteristic of the overall PA is shown in Fig. 1.8.

Figure 1.8: PA output power  $(P_{OUT,RF})$  vs. input power  $(P_{IN})$ .

The PA provides an output power equal to +6 dBm when is driven by input power of -15 dBm supplied by the class-A driver stage. The saturation power level is nearly equal to +9 dBm. The overall PA reaches a drain efficiency equal to 16% and a power-added efficiency of 15% at +6 dBm of output power. The power added efficiency vs. the input power is shown in Fig. 1.9.

The up-conversion mixers are implemented by two double balanced Gilbert cells. This architecture allows the reduction of the phase noise effects and the LO-to-RF leakage. Since the  $ICP_{1dB}$  of the driver stage is -15 dBm, then each mixer has to exhibit an  $OCP_{1dB}$  lower than -18 dBm (the output sum signal is

Figure 1.9: PA drain efficiency (PAE) vs. input power  $(P_{IN})$ .

3 dB higher). The I/Q differential currents provided by the mixer are collected to the input of the driver stage of the PA by means of the integrated symmetric balun. The transistors  $M_I$  and  $M_Q$  have a gate width (W) of 300 µm, whereas the transistors of the switching stages ( $M_S$ ) have a width equal to 200 µm. The resistive gate-source capacitance degeneration ( $R_S$ ) has been introduced in order to properly fix the conversion gain of the mixers. Each mixer drains a bias current of 1.5 mA with a 1.8 V power supply. The overall transmitter provides an output power up to +6 dBm while it is driven by an input power of 18 dBm. The power consumption of the transmitter is of 16 mW on a 1.8 V power supply. The comparison with the most representative solutions presented in literature is reported in Table 1.3. To be noted that the solution herein proposed attains one of the best trade-off between the power consumption and the output power level among the previous works reported in literature (for sake of clarity, our performance are obtained by simulations, while the performance of the other works reported in Table 1.3 are obtained by measurements).

| Work      | Tech             | $V_{cc}$ | Pout     | $P_D$ |

|-----------|------------------|----------|----------|-------|

| WOIR      | Teen             | [V]      | [dBm]    | [mW]  |

| [16]      | $0.25\mu m$ CMOS | 2.5      | 0        | 16    |

| [19]      | $0.18\mu m$ CMOS | 1.8      | 0        | 18    |

| [20]      | $0.18\mu m$ CMOS | 1.8      | -4       | 17    |

| [21]      | $0.18\mu m$ CMOS | 1.8      | 3.5      | 14.4  |

| This work | $SiGe^*$         | 1.8      | $+6^{*}$ | 16    |

Table 1.3: Summary of the Transmitter Performance and Comparison with Previous Works

\*corresponding to the OCP<sub>1dB</sub> of the preceding drive stage

## 1.3 5-6 GHz LC-Active VCO for CMOS RF Transceivers

In a radio-frequency front-end, the voltage controlled oscillator generate the signals that, by using of the phase locked loop (PLL), are provided as local oscillation (LO) for the mixers. The phase noise produced by the VCO strongly affects the noise performance of the mixers [22] and then of the overall transceiver. Thus, it is very important that the VCO exhibits a phase noise as low as possible.

Fully integrated VCOs with a lower phase noise are implemented by using LC tanks resonating at the frequency of interest. However, the phase noise performance are mainly limited by the low quality factor (Q) of the LC tank [23], which is mostly impaired by the loss mechanisms in the integrated spiral inductors.

Examples of high-Q passive inductors have been presented in literature [24]. These inductors are realized by means of additional steps in the fabrication process, which cause a dramatic increase of the chip fabrication costs.

For that reason there is a strong interest in the realization of high-Q inductors by means of active equivalent circuits. Several topologies of active inductors have been presented in literature [25, 26]. However, active inductors are not free of drawbacks, such as the production of an amount of excess noise and the limited linearity.

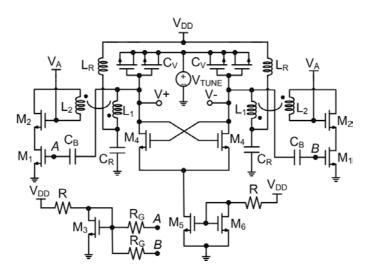

A novel fully integrated 5-6 GHz LC tank VCO for WLAN multi-standard applications has been designed in a 0.35 µm CMOS standard process by Austriamicrosystems and presented in [OP7, OP3]. In detail, the circuit exploits a new version of the CMOS Boot-Strapped Inductor (BSI) [27], presented in [OP6], which realizes the high-Q equivalent inductors of the LC tanks, playing a key role in reaching the best phase noise (PN) performance.

## 1.3.1 CMOS Boot-Strapped Inductor: The New Circuit

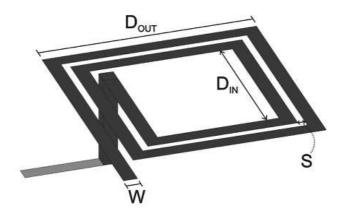

The active circuit named Boot-Strapped Inductor (BSI) has been originally developed in silicon bipolar technology [28]. The BSI consists of an integrated transformer and a current amplifier inserted between its primary and secondary spirals. If the current amplifier circuitry is properly sized, then an increase of the equivalent inductance seen from the primary and its quality factor (boot-strap effect) can be obtained.

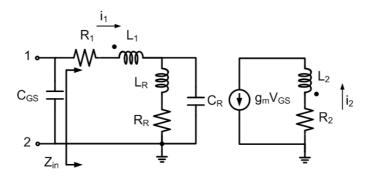

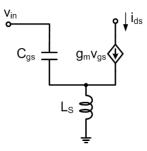

Recently, the BSI circuit topology has been rearranged in CMOS technology as well [29, 27]. The small signal equivalent circuit of the CMOS BSI therein reported is shown in Fig. 1.10.

If the impedance  $Z_{in}$  is purely inductive  $(Z_{in}(j\omega) \approx j\omega L_{in})$ , then the impedance  $Z_{12}$  (seen from the nodes 1 and 2) can be written as follows

$$Z_{12}(j\omega) = \frac{j\omega L_{in}}{1 - \omega^2 L_{in} C_{GS}} \tag{1.14}$$

Typical values of the capacitance  $C_{GS}$  of the transistors in the BSI design are in the order of several tens of femtoFarad. Therefore, the effect of  $C_{GS}$  can be neglected in (1.14) if  $L_{in}$  is lower than a specific amount (i.e. at 5-6 GHz, the effect can be neglected if Lin is lower than 10 nH). In this condition, then

Figure 1.10: Small-signal equivalent circuit of the CMOS BSI. The inductors  $L_1$ ,  $L_2$  and  $L_R$  are reported with their series loss resistances.  $g_{mc}$  is the total equivalent transconductance of the cascode stage ( $M_1$  and  $M_2$ ), which is mainly given by the contribution of the common gate-source capacitance stage.

$Z_{12}(j\omega) \approx Zin(j\omega) \approx j\omega L_{in}$ . Then,  $Z_{12}$  can be approximately written as follows [29]

$$Z_{12}(j\omega) = \frac{(Z_P + R_1 + j\omega L_1)(1 + j\omega M \ g_{mc})}{1 + \omega^2 M^2 \ g_{mc}^2}$$

(1.15)

where, M is the mutual inductance between  $L_1$  and  $L_2$ , and  $Z_P$  is the parallel impedance of the inductor  $L_R$  and the capacitor  $C_R$ . At frequencies lower than the self-resonance frequency of  $Z_P$  and with proper values of  $g_{mc}$  and M, the BSI exhibits a high-Q inductive behaviour between the nodes 1 and 2.

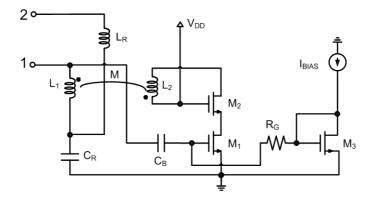

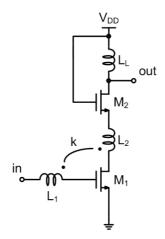

A new version of the CMOS BSI (reported in Fig. 1.11) introduces several improvements for its efficient use in the RF CMOS design for the modern transceivers.

Figure 1.11: The new version of the CMOS BSI.

Unlike the BSI circuit described in [29], the DC biasing of the transistor  $M_1$  is independent from the external circuitry connected to the nodes 1 and 2. In fact, the placement of the inductor  $L_R$  has been changed and a DC blocking capacitor  $C_B$  (from the node 1 and the gate of  $M_1$ ) has been introduced.

In detail, these changes allow us to wire the VCO to power supply without introducing additional components, which not only require additional area on die but introduce undesired parasitic effects that reduce the overall circuit performance. This makes independent the bias circuitry of the BSI from that of the rest of the circuit (e.g. the VCO core if the BSI is applied to VCO design). In this way a separate tuning of the BSI circuit performance and those of the rest of the circuit are allowed. If the reactance of the capacitor  $C_B$  can be neglected at the operating frequencies, and the node 2 is properly AC grounded, then the small signal equivalent circuit of the BSI herein presented becomes the same of that reported in [29] and shown in Fig. 1.10, so that the previous design considerations can be easily extended to the new circuit.

## **BSI** Design

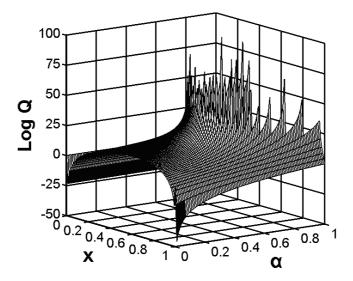

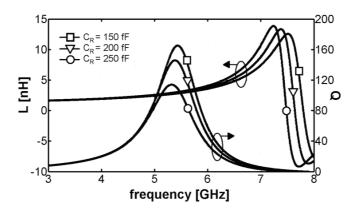

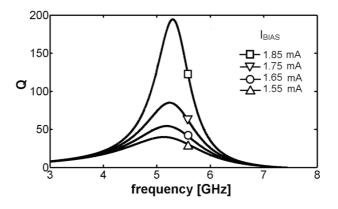

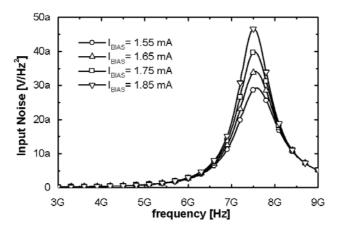

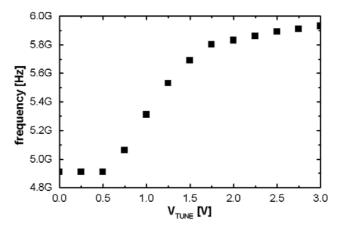

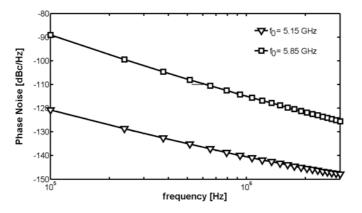

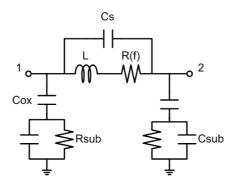

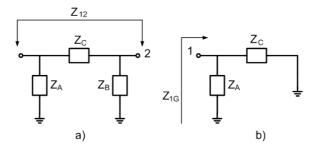

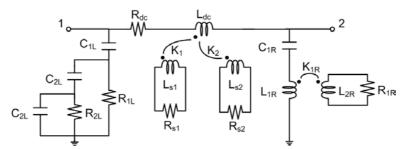

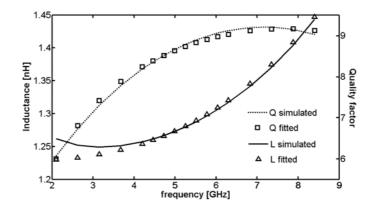

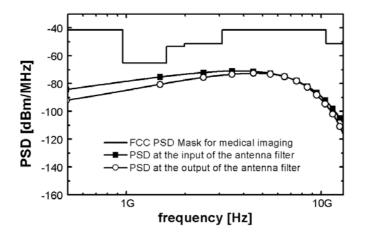

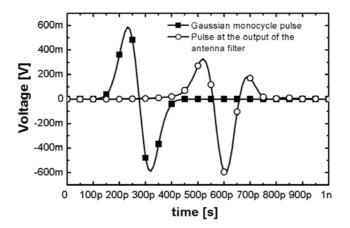

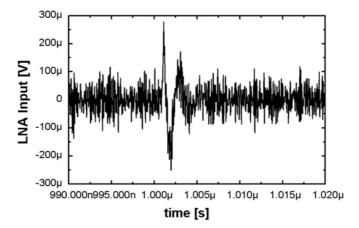

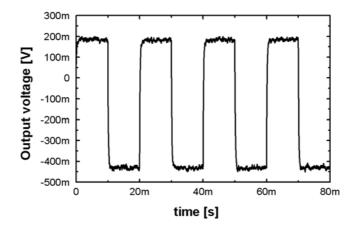

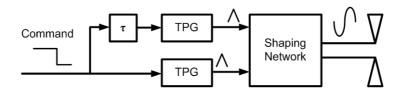

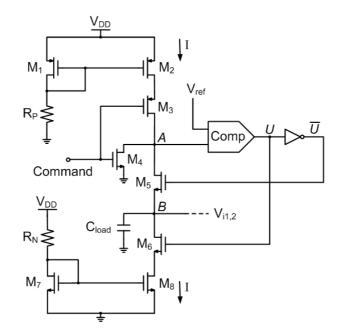

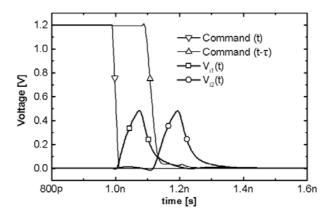

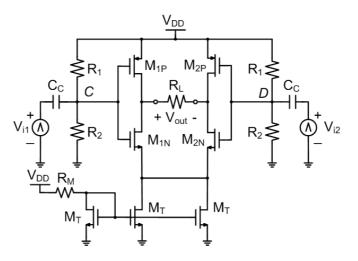

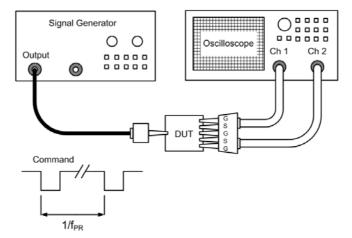

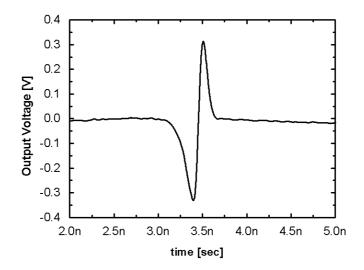

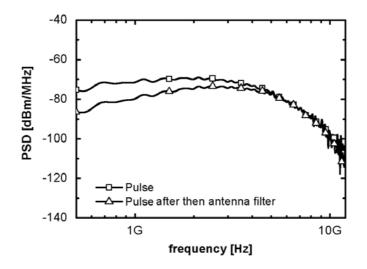

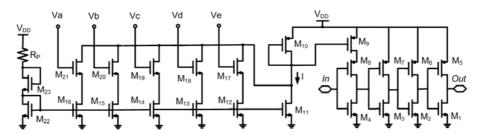

As first step, an extensive analytical description of the BSI has been derived in order to widely investigate its design space and reach an optimal circuit synthesis. This work has been reported in [OP6]. This analytic description allows us to properly size the circuit, in order to achieve the values of equivalent inductance suitable to be resonating with an integrated capacitor and simultaneously maximize its quality factor (Q). In Fig. 1.12, the Q factor of the BSI versus x ( $x = \omega/\omega_R$ , where  $\omega_R = 1/\sqrt{L_R C_R}$ ) and  $\alpha$  ( $\alpha = \omega_R M g_m$ ) obtained by MAT-LAB<sup>TM</sup> simulations, is depicted.