$N^{\circ}$  d'ordre : 3811

## THÈSE

présentée à

# L'Université Bordeaux 1

Ecole doctorale des Sciences Physiques et de l'Ingénieur

#### par François RIVET

Pour obtenir le grade de

### DOCTEUR

SPÉCIALITÉ : ÉLECTRONIQUE

CONTRIBUTION À L'ÉTUDE ET À LA RÉALISATION D'UN FRONTAL RADIOFRÉQUENCE ANALOGIQUE EN TEMPS DISCRETS POUR LA RADIO-LOGICIELLE INTÉGRALE

Soutenue le : 19 Juin 2009

Après avis de :

M. Edgar Sánchez-Sinencio Professeur Texas A&M University Rapporteur

Patrice Gamand HDR NXP Semiconductors Rapporteur

Devant la commission d'examen formée de :

Jean-Baptiste BÉGUERET M.Professeur Université Bordeaux 1 Co-directeur de thèse **Didier** Belot Industriel Expert ST Microelectronics Philippe CATHELIN ST Microelectronics Industriel Ingénieur Professeur Dominique DALLET **ENSEIRB** Bordeaux Président Yann Deval Professeur ENSEIRB Bordeaux Directeur de thèse Patrice Gamand HDR NXP Semiconductors Rapporteur Edgar SÁNCHEZ-SINENCIO Professeur Texas A&M University Rapporteur

# Remerciements

A mes parents, à ma famille, à mes amis.

$A\ Yann,\ Jean-Baptiste\ et\ Dominique,$   $\grave{a}\ l'\acute{e}quipe\ Conception\ de\ Circuits,$   $\grave{a}\ l'\acute{e}quipe\ Circuits\ et\ Syst\grave{e}mes\ Hyperfr\acute{e}quences.$

Aux membres du laboratoire IMS.

| Li | List of Abbreviations |        |                                          |    |

|----|-----------------------|--------|------------------------------------------|----|

| Li | List of Notations     |        |                                          |    |

| In | trodu                 | action |                                          | 21 |

| 1  | The                   | Softw  | vare Radio Concept                       | 23 |

|    | 1.1                   | Wirele | ess communication systems                | 24 |

|    |                       | 1.1.1  | Wireless communication architectures     | 25 |

|    |                       | 1.1.2  | Wireless communication standards         | 27 |

|    |                       | 1.1.3  | Wireless communication market and trends | 28 |

|    |                       | 1.1.4  | Conclusion                               | 30 |

|    | 1.2                   | Softwa | are Radio Background                     | 30 |

|    |                       | 1.2.1  | Definition                               | 30 |

|    |                       | 1.2.2  | History                                  | 31 |

|    |                       | 1.2.3  | Software Radio Characteristics           | 33 |

|    |                       | 1.2.4  | Technological Bottlenecks                | 35 |

|    |                       | 1.2.5  | Software Defined Radio Architectures     | 40 |

|    | 1.3                   | Analo  | g Signal Processing                      | 44 |

|    | 1.4                   | Concl  | usion                                    | 49 |

| 2  | Sam                   | pled A | Analog Signal Processor                  | 51 |

|    | 2.1                   | Princi | ple                                      | 52 |

|    |                       | 2.1.1  | Analog Signal Processor Principle        | 52 |

|    |                       | 2.1.2  | Frequency Translation                    | 53 |

|    |                       | 2.1.3  | A Fourier Transform                      | 56 |

|    | 2.2                   | A Fas  | t Fourier Transform                      | 57 |

|    |                       | 2.2.1  | The Cooley-Tukey algorithm               | 57 |

|    |                       | 2.2.2  | A pipelined DFT                          | 60 |

|   | 2.3  | Archite | ecture                                                |

|---|------|---------|-------------------------------------------------------|

|   |      | 2.3.1   | Signal pre-processing                                 |

|   |      | 2.3.2   | DFT implementation                                    |

|   |      | 2.3.3   | Post-signal processing                                |

|   | 2.4  | A Soft  | ware Radio System                                     |

|   |      | 2.4.1   | Concurrent reception                                  |

|   |      | 2.4.2   | Frequency demodulation                                |

|   | 2.5  | Conclu  | sion                                                  |

| 3 | Scho | ematic  | s and Modeling results                                |

|   | 3.1  | Discret | te Analog Operations                                  |

|   |      | 3.1.1   | Accumulation Delay Line                               |

|   |      | 3.1.2   | Matrix Unit                                           |

|   |      | 3.1.3   | Weighting Unit                                        |

|   | 3.2  | Digital | Instructions                                          |

|   |      | 3.2.1   | A base-4 algorithm clock generation                   |

|   |      | 3.2.2   | A hardware-implemented algorithm                      |

|   | 3.3  | Design  | - SASPEPA and LUCATESTA                               |

|   |      | 3.3.1   | Peripherical building blocks                          |

|   |      | 3.3.2   | Layout considerations                                 |

|   |      | 3.3.3   | A building block library                              |

|   |      | 3.3.4   | Post-Layout Simulations                               |

|   | 3.4  | Conclu  | sion                                                  |

| 4 | Mea  | asurem  | ents and Perspectives 12'                             |

|   | 4.1  | Test Se | etup and Experimental Results                         |

|   |      | 4.1.1   | Test setup                                            |

|   |      | 4.1.2   | SASP validation measurements                          |

|   |      | 4.1.3   | SASP applications measurements                        |

|   |      | 4.1.4   | SASPEPA Characteristics                               |

|   | 4.2  | An ope  | en window to RF applications - Achievement of SASP65K |

|   |      | 4.2.1   | Schematic perspectives                                |

|   |      | 4.2.2   | Technology issues                                     |

|   |      | 4.2.3   | Signal processing accuracy                            |

|   |      | 4.2.4   | Real-Time error correction                            |

|   | 4.3  | Conclu  | usion 14                                              |

| Contents     | 7   |

|--------------|-----|

| Conclusion   | 147 |

| Publications | 149 |

| Bibliography | 152 |

| 1.1  | Transceiver Architecture                                              | 25 |

|------|-----------------------------------------------------------------------|----|

| 1.2  | Emitter Architecture                                                  | 26 |

| 1.3  | Receiver Architecture                                                 | 26 |

| 1.4  | Evolution of the GSM standard to LTE                                  | 28 |

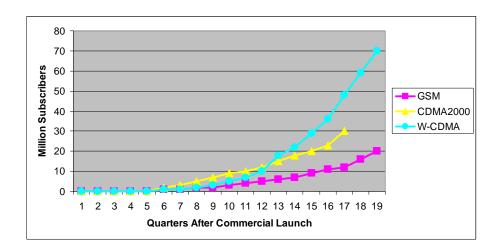

| 1.5  | Global Subscribers by Technology                                      | 29 |

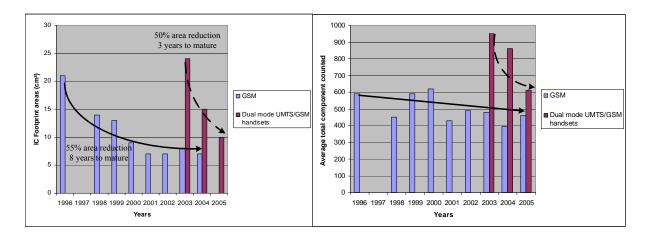

| 1.6  | Components parameters evolution in Mobile Phones                      | 29 |

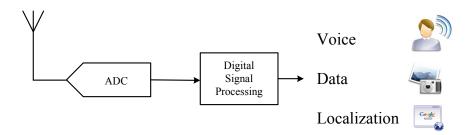

| 1.7  | Ideal Software Radio receiver architecture                            | 31 |

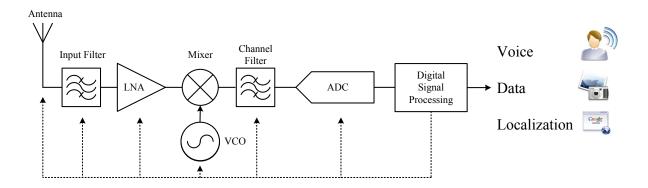

| 1.8  | Realistic Software-Defined Radio receiver architecture                | 33 |

| 1.9  | Software-Defined to Software Radio Classification                     | 34 |

| 1.10 | ADC issues                                                            | 35 |

| 1.11 | ADC power consumption                                                 | 36 |

| 1.12 | ADC limitations                                                       | 37 |

| 1.13 | ADC Figure of merit                                                   | 38 |

| 1.14 | Power consumption per MIPS for DSP the last 20 years                  | 39 |

| 1.15 | Software Defined Radio by Baseband Conversion Architecture            | 41 |

| 1.16 | RF signal to baseband translation by Baseband Conversion Architecture | 41 |

| 1.17 | RF signal to IF translation by IF Conversion Architecture             | 41 |

| 1.18 | Software Defined Radio by sub-sampling                                | 42 |

| 1.19 | Software Defined to Software Radio State of the Art                   | 43 |

| 1.20 | Proposed SR architecture                                              | 44 |

| 1.21 | Charge Coupled circuit in 3 working phases                            | 45 |

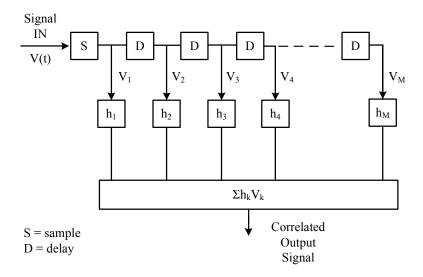

| 1.22 | Block Diagram of a Transversal Filter                                 | 46 |

| 1.23 | Block Diagram of a Correlator                                         | 47 |

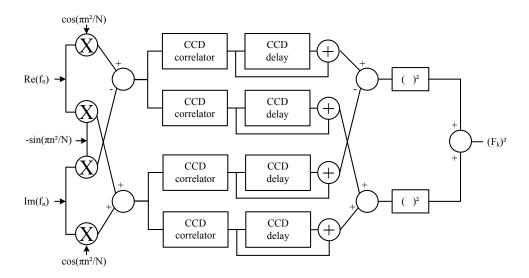

| 1.24 | Block Diagram of a Chirp Transform                                    | 48 |

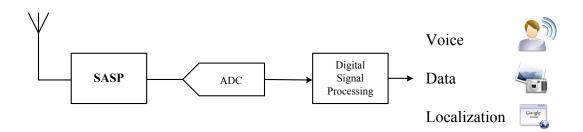

| 2.1  | Proposed SR architecture                                              | 53 |

| 2.2  | Principle of the frequency translation                                | 54 |

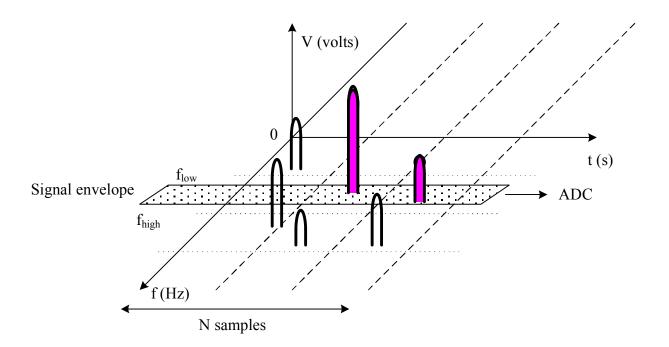

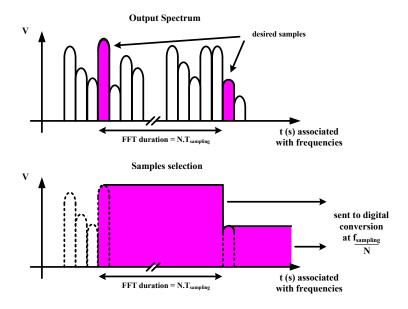

| 2.3  | Envelope selection and digitization                                                      | 55 |

|------|------------------------------------------------------------------------------------------|----|

| 2.4  | Sinewave FFT                                                                             | 55 |

| 2.5  | Frequency Translation of a modulated signal                                              | 56 |

| 2.6  | $W_N^{nk}$ properties                                                                    | 58 |

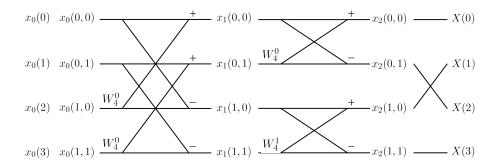

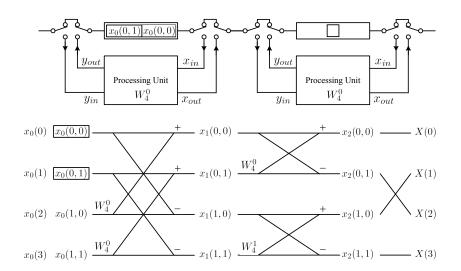

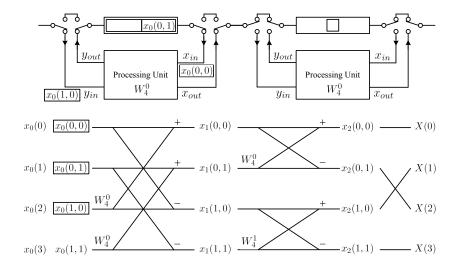

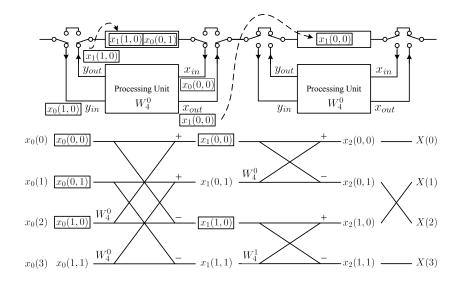

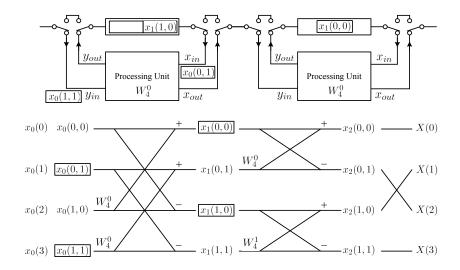

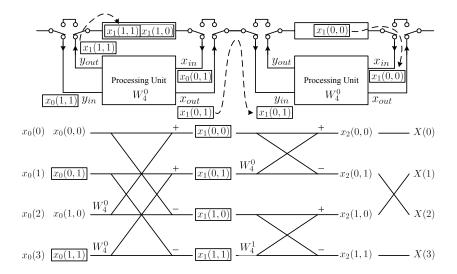

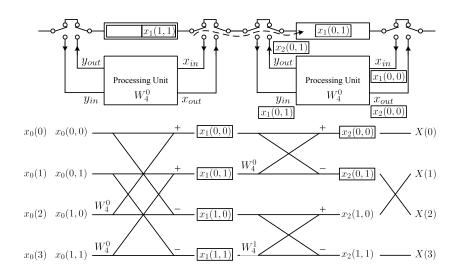

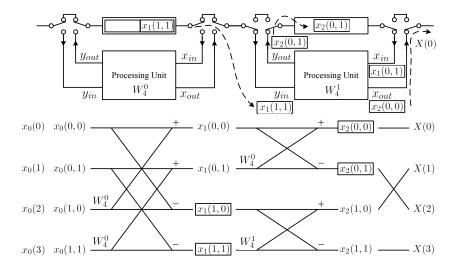

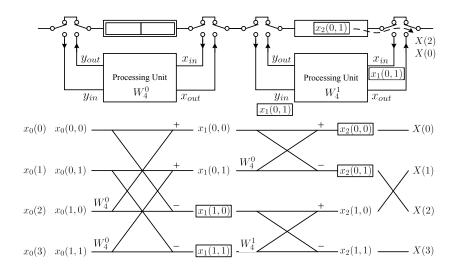

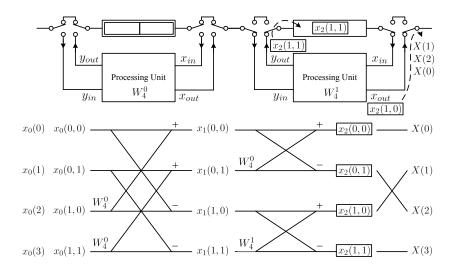

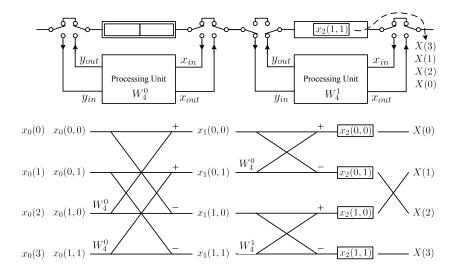

| 2.7  | N=4 Pipelined DFT                                                                        | 60 |

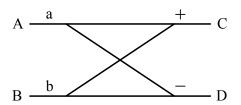

| 2.8  | Module of radix-2 DFT                                                                    | 60 |

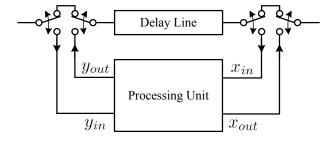

| 2.9  | Basic cell of a pipelined DFT                                                            | 61 |

| 2.10 | Step 1                                                                                   | 62 |

| 2.11 | Step 2                                                                                   | 62 |

| 2.12 | Step 3                                                                                   | 63 |

| 2.13 | Step 4                                                                                   | 63 |

| 2.14 | Step 5                                                                                   | 64 |

| 2.15 | Step 6                                                                                   | 64 |

| 2.16 | Step 7                                                                                   | 65 |

| 2.17 | Step 8                                                                                   | 65 |

| 2.18 | Step 9                                                                                   | 66 |

| 2.19 | Step 10                                                                                  | 66 |

| 2.20 | SASP Architecture                                                                        | 67 |

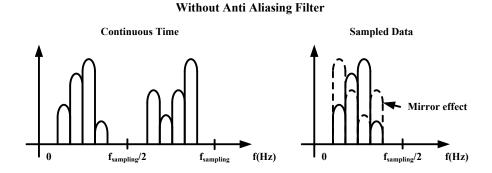

| 2.21 | Aliasing Matters without Anti Aliasing Filter                                            | 68 |

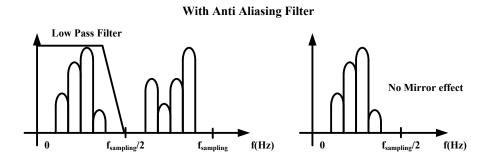

| 2.22 | Aliasing Matters with Anti Aliasing Filter                                               | 68 |

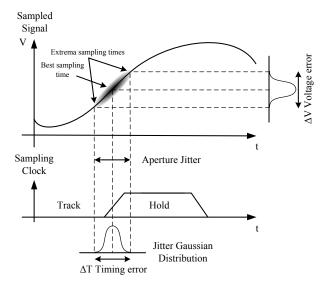

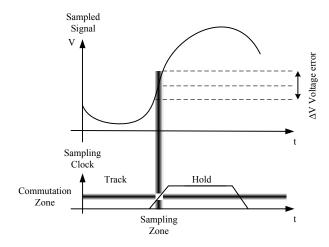

| 2.23 | Aperture Time Error                                                                      | 69 |

| 2.24 | Aperture Uncertainty Error                                                               | 70 |

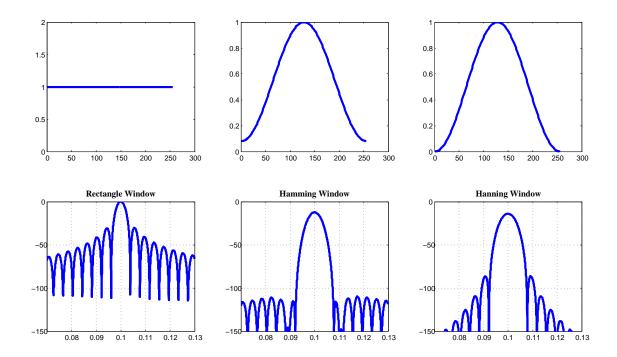

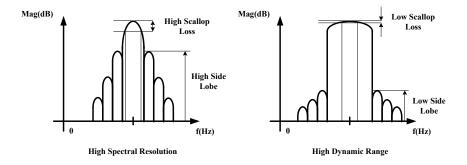

| 2.25 | Differents kind of windows                                                               | 72 |

| 2.26 | Window characteristics                                                                   | 72 |

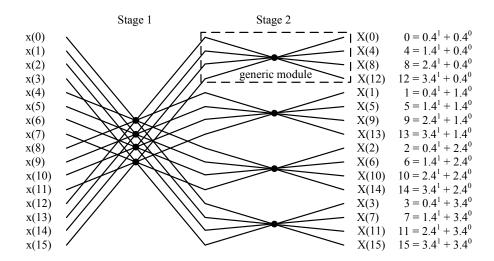

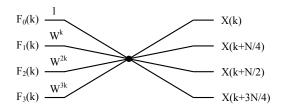

| 2.27 | Diagram flow of a radix-4 FFT with $N=16,$ i.e. 2 stages                                 | 73 |

| 2.28 | Basic radix-4 FFT module                                                                 | 74 |

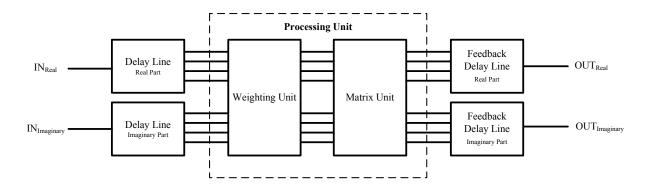

| 2.29 | Stage architecture                                                                       | 74 |

| 2.30 | Accumulation Delay Line                                                                  | 75 |

| 2.31 | Samples selection                                                                        | 76 |

| 2.32 | Envelope voltage samples selection                                                       | 77 |

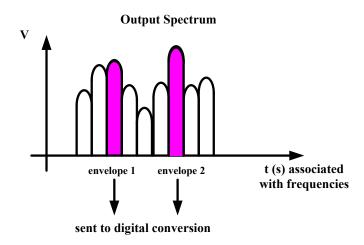

| 2.33 | Concurrent reception                                                                     | 79 |

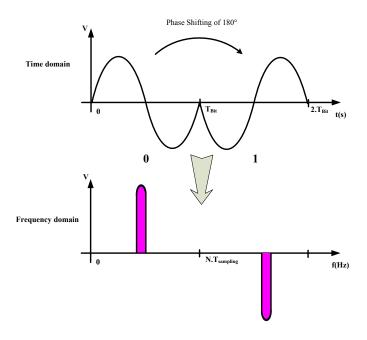

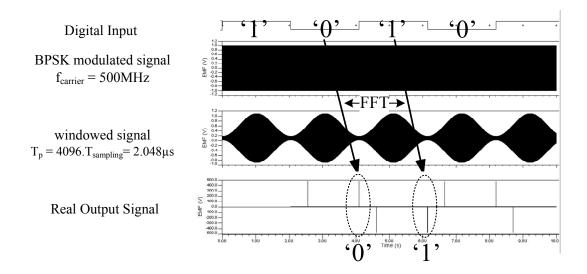

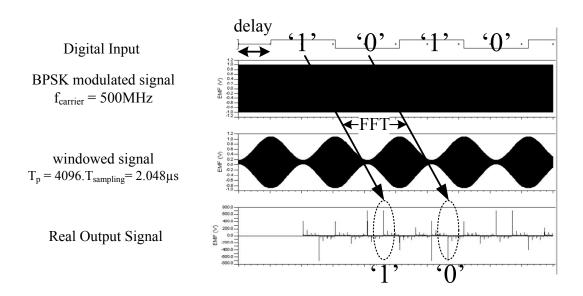

| 2.34 | Theorical BPSK signal processing                                                         | 80 |

| 2.35 | A synchronized BPSK signal processed by 4096-point SASP                                  | 80 |

| 2.36 | A non-synchronized BPSK signal processed by 4096-point SASP $\ \ldots \ \ldots \ \ldots$ | 81 |

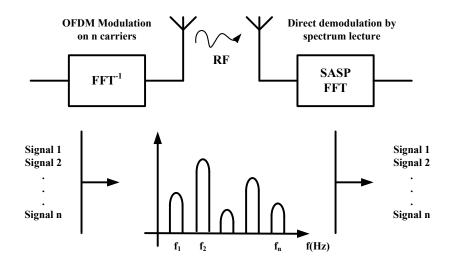

| 2.37 | A OFDM signal processed by the SASP                                                      | 81 |

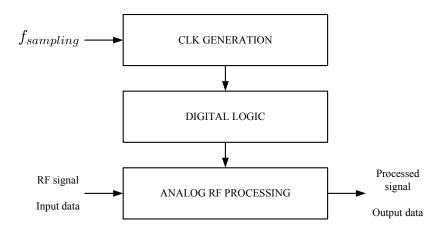

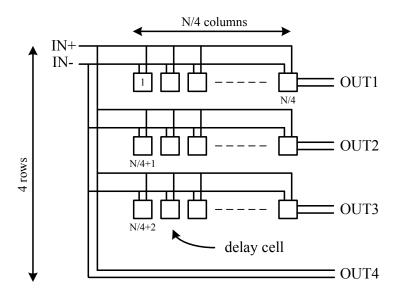

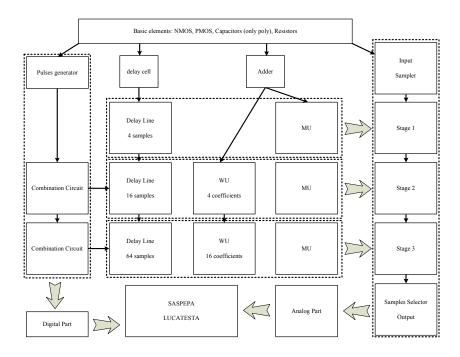

| 3.1  | Processor Architecture                                                    |

|------|---------------------------------------------------------------------------|

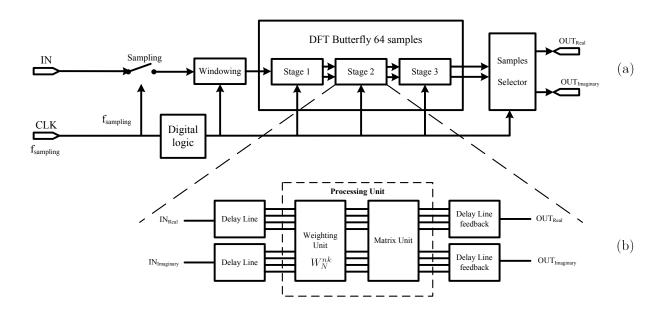

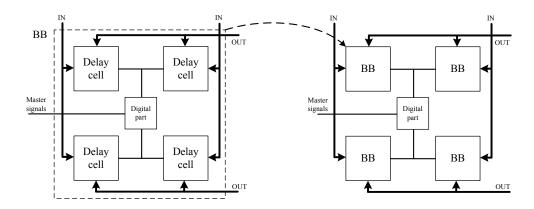

| 3.2  | (a) Architecture of SASP64, (b) Close-up of a stage                       |

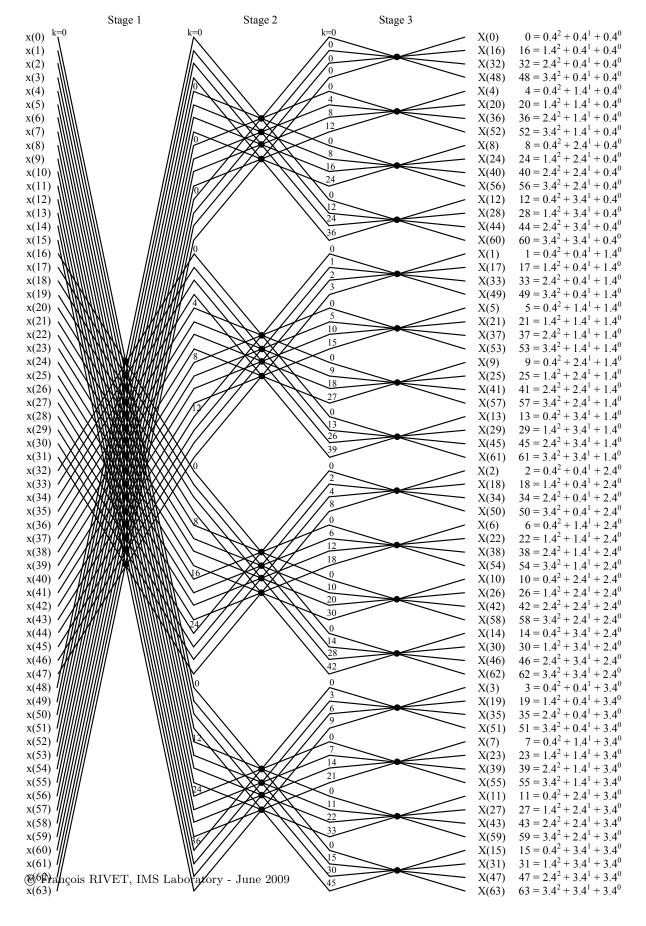

| 3.3  | Diagram flow of a radix-4 FFT with $N=64\ldots 86$                        |

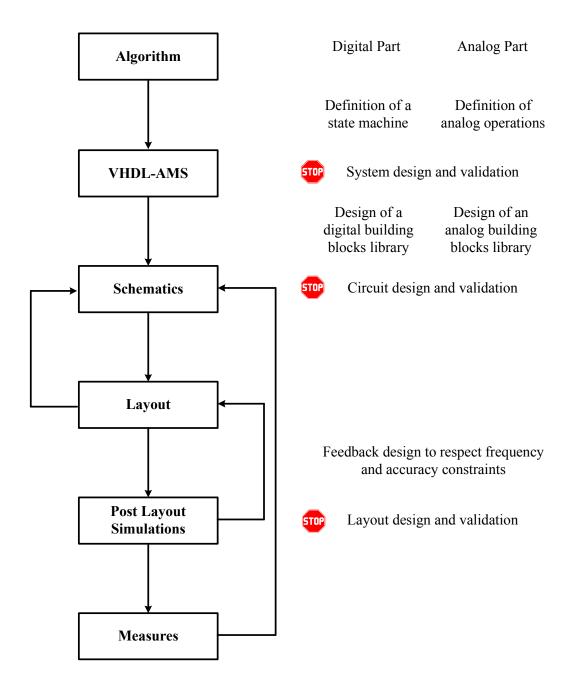

| 3.4  | Design Flow                                                               |

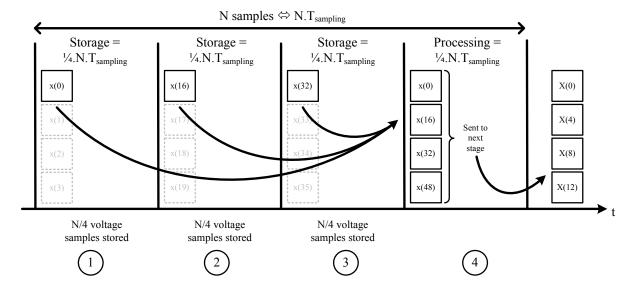

| 3.5  | Processing phases                                                         |

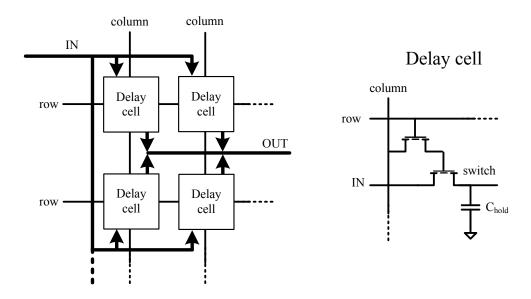

| 3.6  | Delay Line system view                                                    |

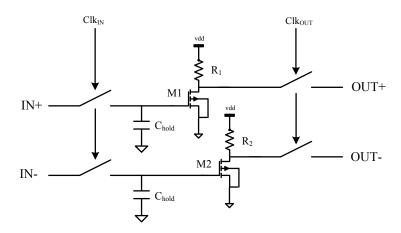

| 3.7  | Simplified schematic of a delay cell                                      |

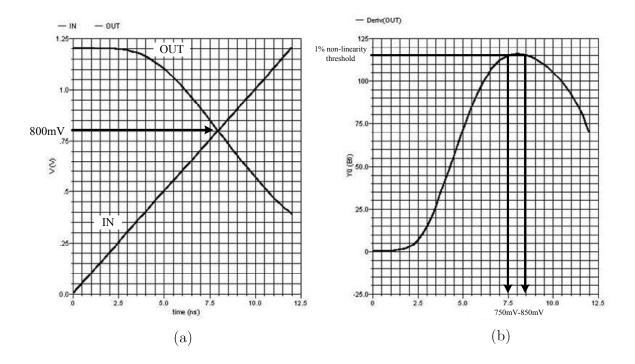

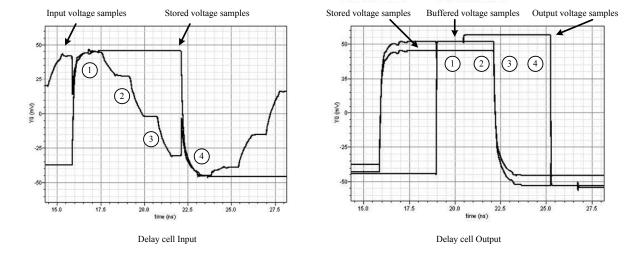

| 3.8  | (a) Buffer characterization, (b) Output derivation                        |

| 3.9  | Delay line lowest working frequency                                       |

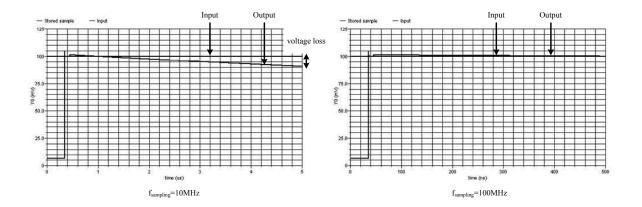

| 3.10 | Charge Transfer. Load (a) and Display (b) of a voltage sample             |

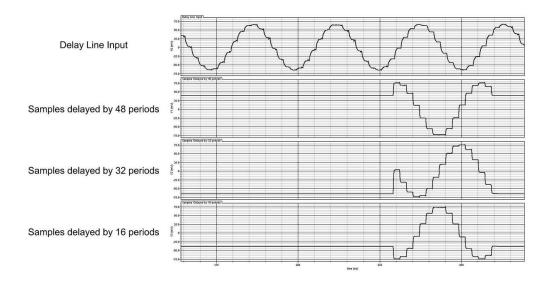

| 3.11 | Simulation of a delay line                                                |

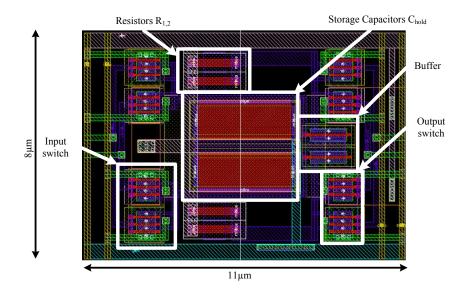

| 3.12 | Delay Cell layout                                                         |

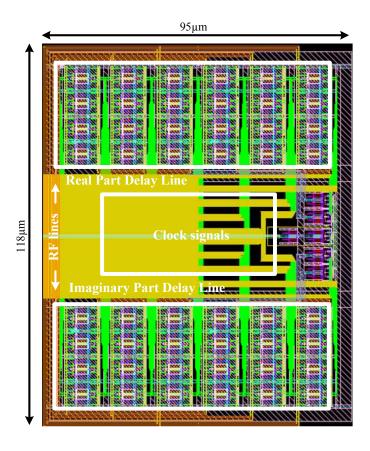

| 3.13 | Delay Line with 64 samples layout                                         |

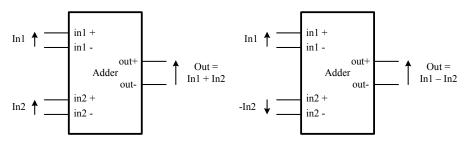

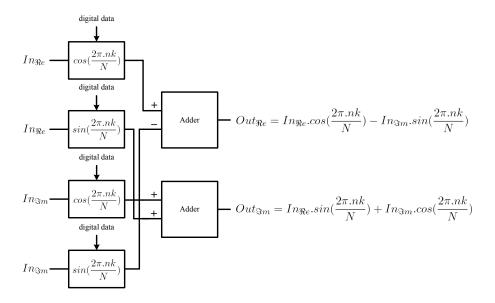

| 3.14 | Matrix design based on adders implementation                              |

| 3.15 | Simplified schematic of a 4-voltage sample adder                          |

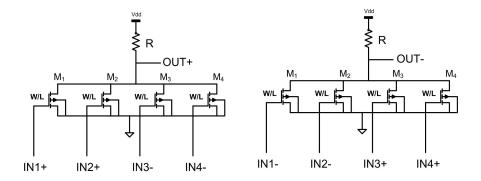

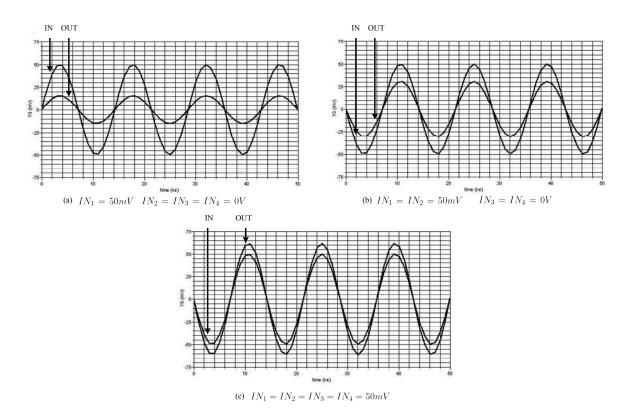

| 3.16 | Simulation of a 4-voltage sample adder                                    |

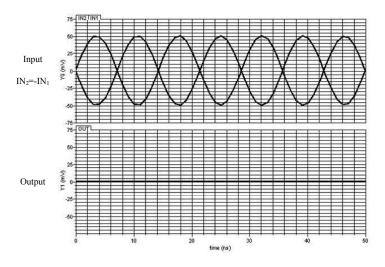

| 3.17 | Simulation of a 4-voltage sample adder, a signal and its inverse added 97 |

| 3.18 | Matrix layout                                                             |

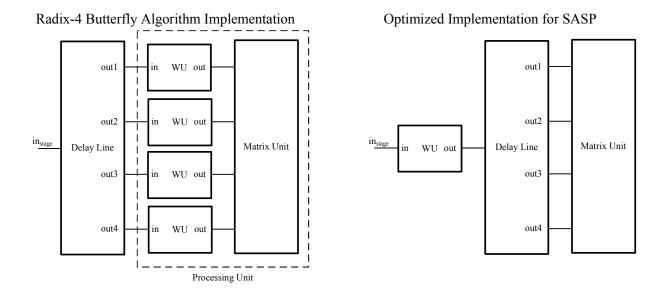

| 3.19 | Comparaison between non-optimized and optimized WU position 99            |

| 3.20 | Weighing Unit architecture                                                |

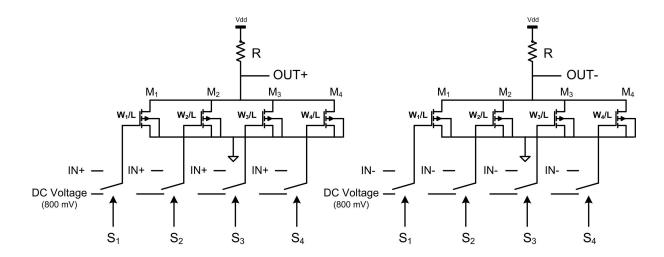

| 3.21 | Simplified schematic of the Weighting Unit                                |

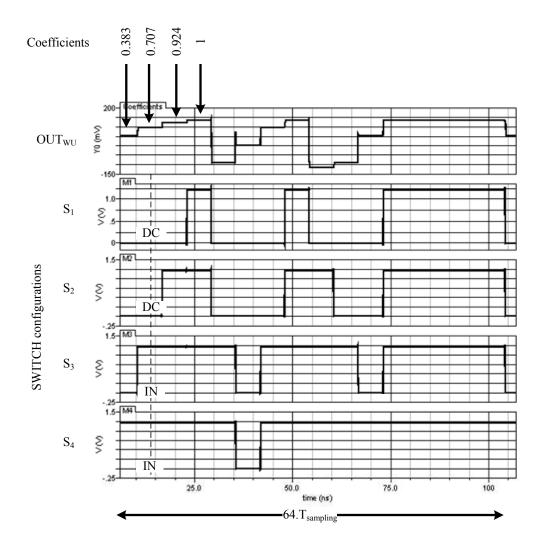

| 3.22 | A 100mV voltage sample weighted by 4 coefficients                         |

| 3.23 | Weighting Unit layout                                                     |

| 3.24 | Design startegy of the digital circuitry                                  |

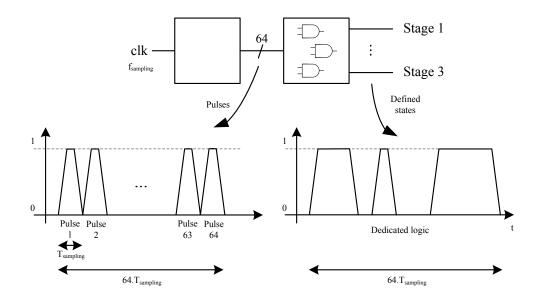

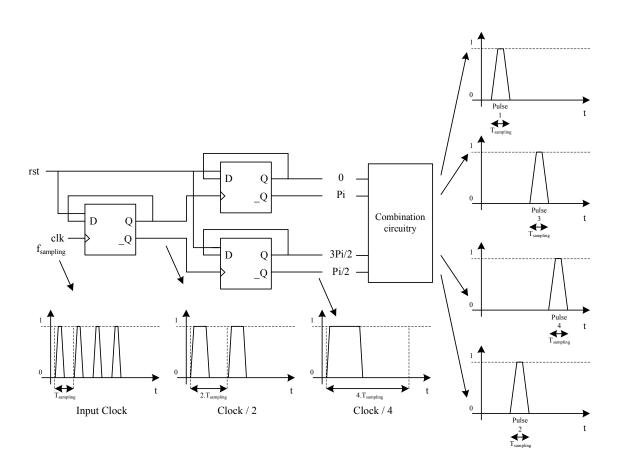

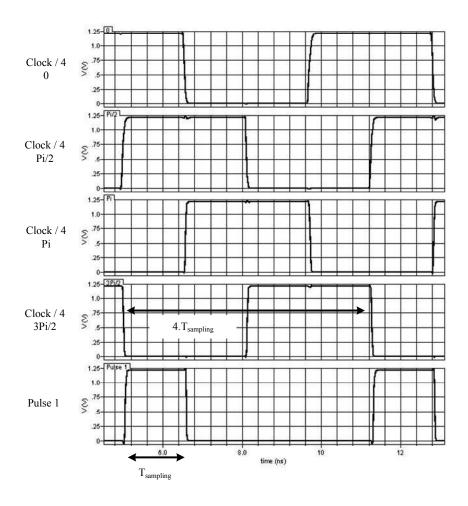

| 3.25 | Generation of 4 pulses                                                    |

| 3.26 | Simulation of pulses generations                                          |

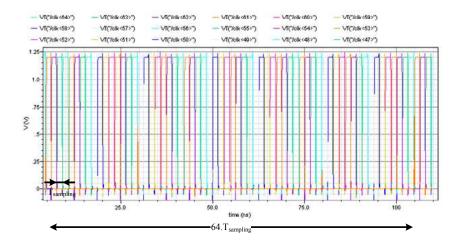

| 3.27 | Simulation of 64 pulses                                                   |

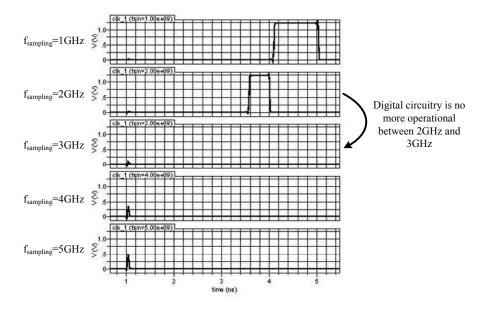

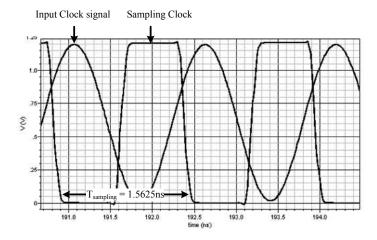

| 3.28 | Simulation of the maximal $f_{\text{sampling}}$                           |

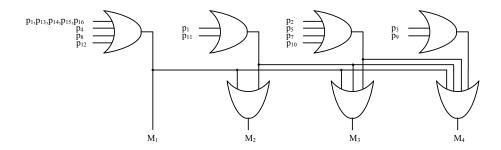

| 3.29 | Example of a logic circuit to address WU                                  |

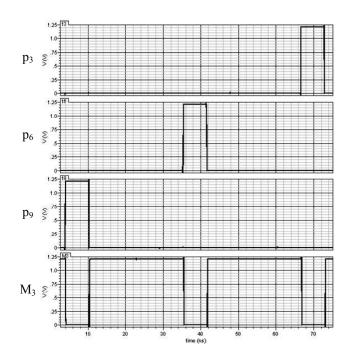

| 3.30 | Simulation result of a state combination, $M_3$                           |

| 3.31 | Architecture of the Sample Selector                                       |

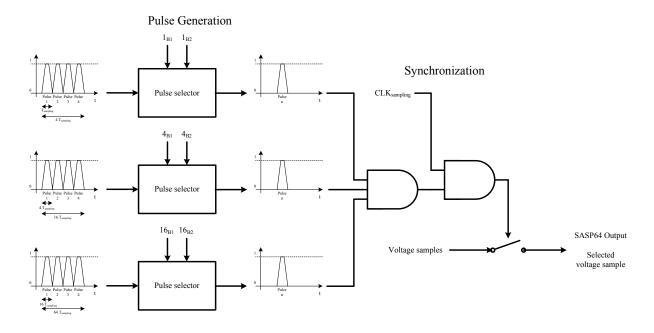

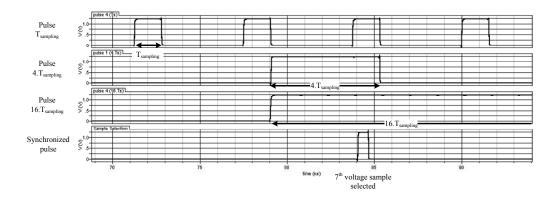

| 3.32 | Generation of the selection of the $7^{th}$ voltage sample                |

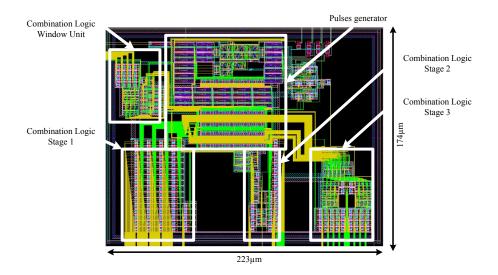

| 3.33 | Digital part layout                                                       |

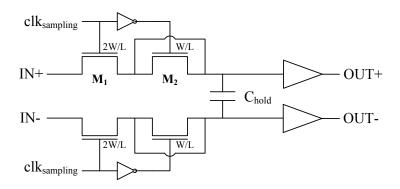

| 3.34 | Sampler Architecture                                                      |

| 3.35 | Sampler simulation                                                        |

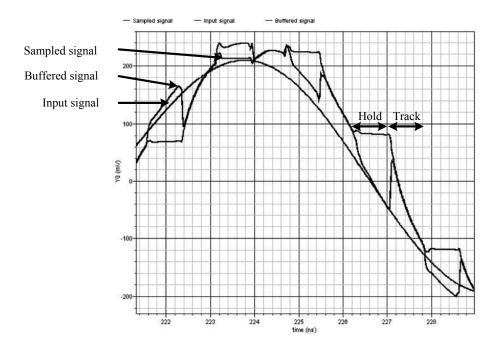

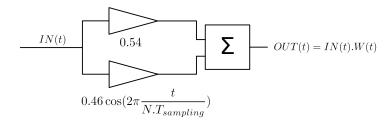

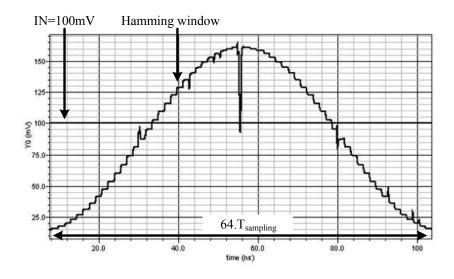

| 3.36 | Windowing circuit (simplified schematic)                                  |

|------|---------------------------------------------------------------------------|

| 3.37 | Simulation result of a Hamming Window                                     |

| 3.38 | Design strategy                                                           |

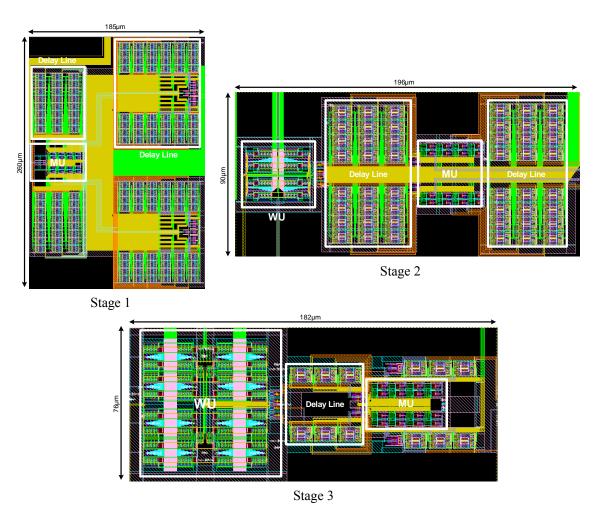

| 3.39 | Stage 1, Stage 2 and Stage 3 layouts                                      |

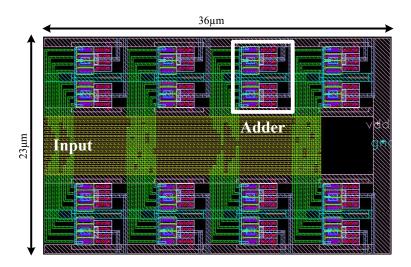

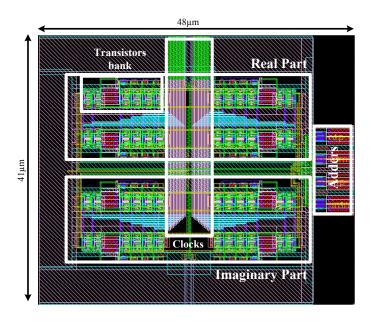

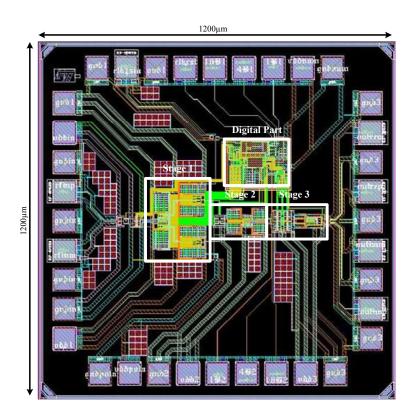

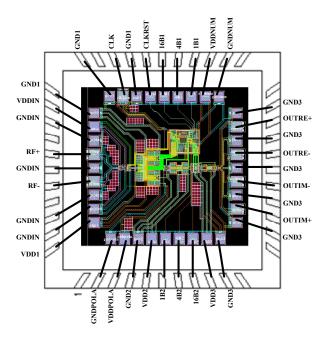

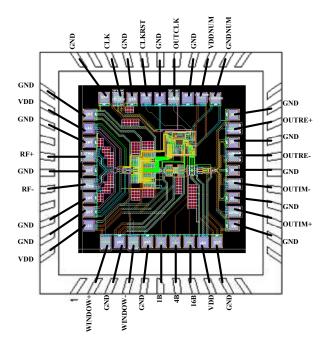

| 3.40 | SASPEPA Layout                                                            |

| 3.41 | PLS of clock signal generation                                            |

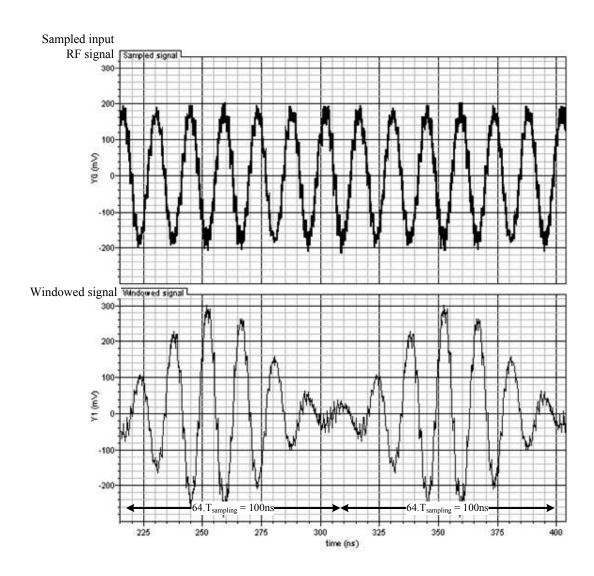

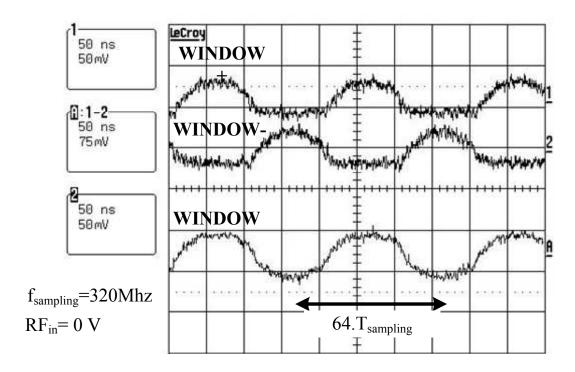

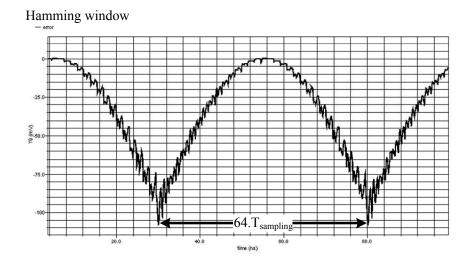

| 3.42 | PLS of windowing operation                                                |

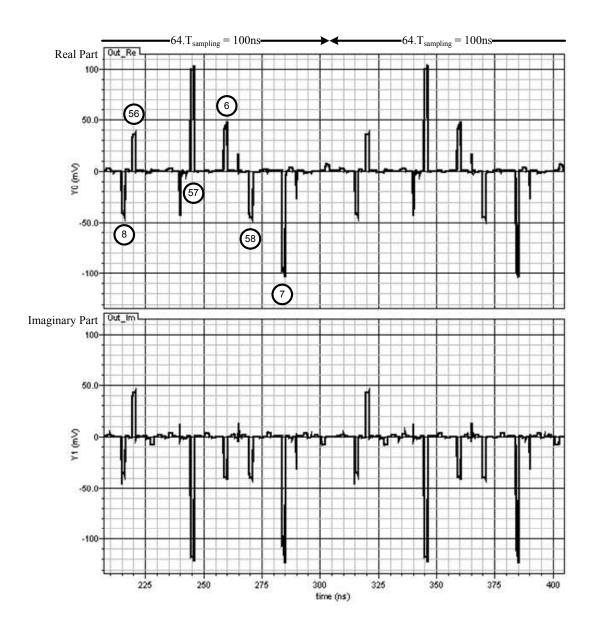

| 3.43 | PLS of output spectrum                                                    |

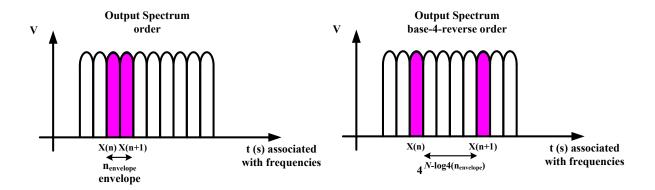

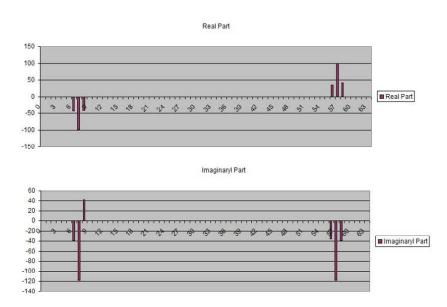

| 3.44 | Output spectrum in order                                                  |

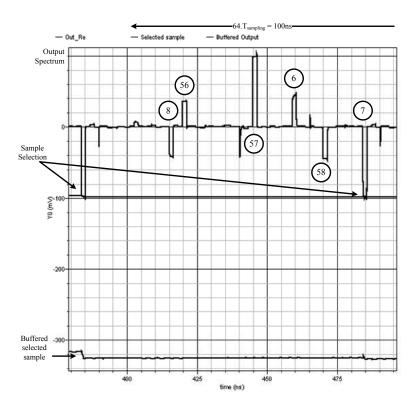

| 3.45 | PLS of the sample selection                                               |

| 3.46 | PLS of output spectrum                                                    |

| 3.47 | Output spectrum in order                                                  |

| 3.48 | PLS of output spectrum                                                    |

| 3.49 | Output spectrum in order                                                  |

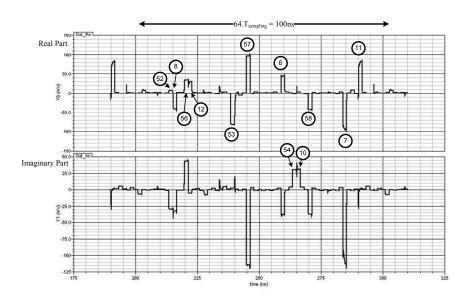

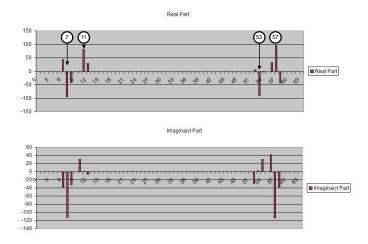

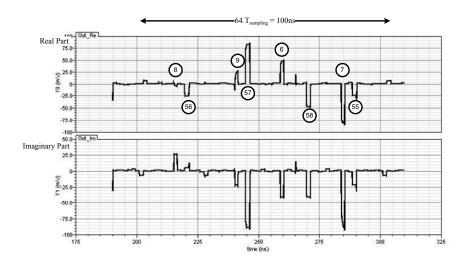

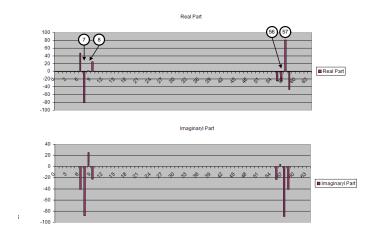

| 3.50 | A non-entire frequency sinewave processed by 64-point SASP                |

| 11   | Floorplan of SASPEPA                                                      |

| 4.1  | Floorplan of LUCATESTA                                                    |

| 4.2  | <del>-</del>                                                              |

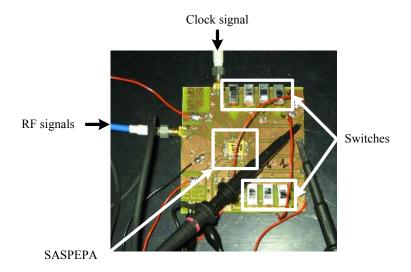

| 4.3  | Test board of SASEPA                                                      |

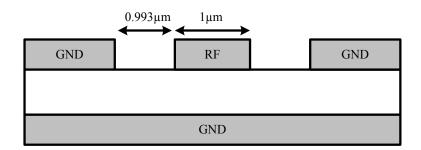

| 4.4  | Coplanar waveguide                                                        |

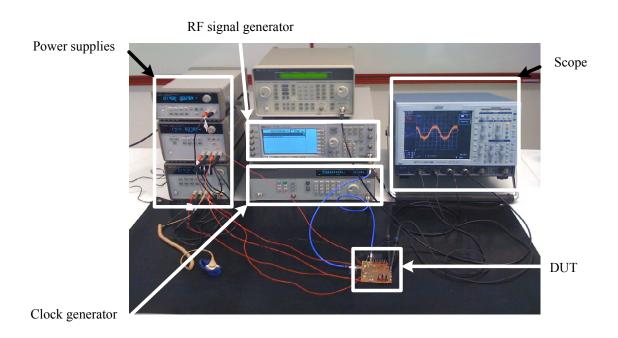

| 4.5  | Photo of instruments configurations                                       |

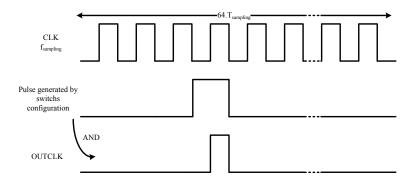

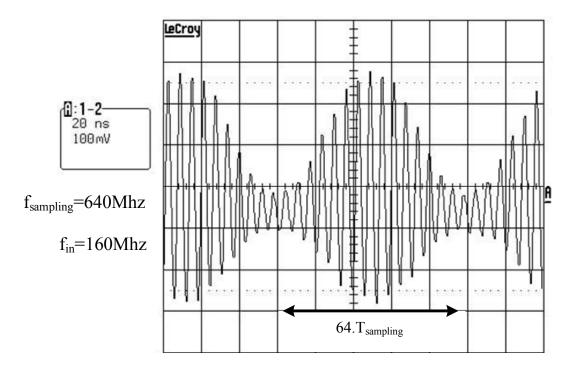

| 4.6  | OUTCLK signal generation                                                  |

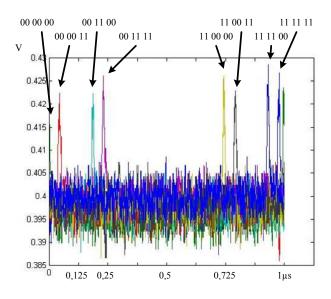

| 4.7  | OUTCLK measurements                                                       |

| 4.8  | Measured hamming window                                                   |

| 4.9  | Measured error on hamming window                                          |

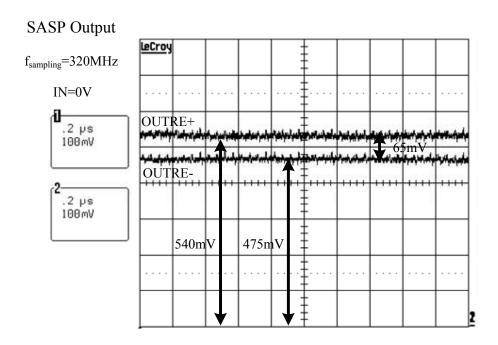

|      | Retro-simulation of a windowed zero-signal                                |

|      | SASP output saturation                                                    |

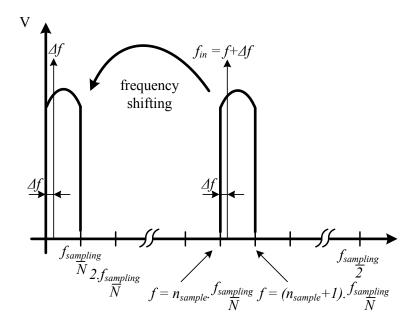

|      | Principle of frequency Shifting                                           |

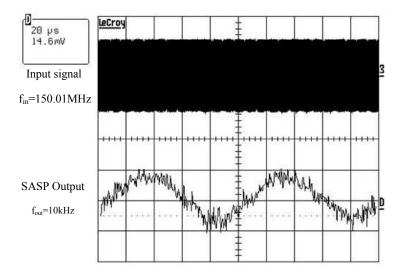

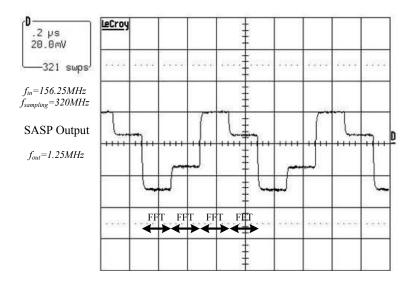

|      | Measure of frequency Shifting                                             |

|      | Measure of a non-entire frequency sinewave processed by 64-point SASP 137 |

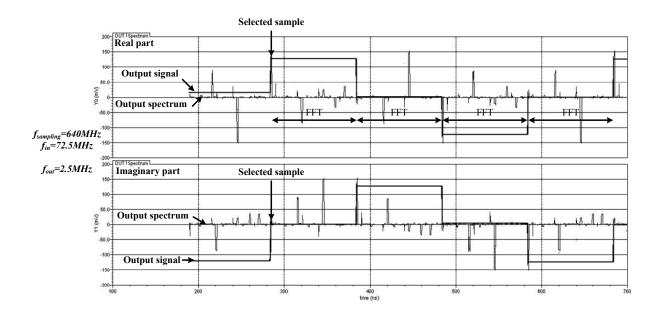

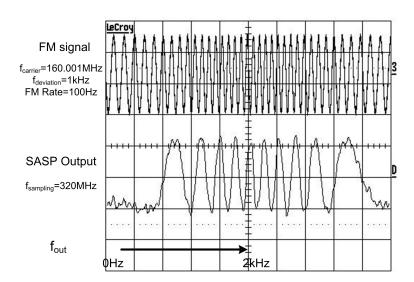

|      | Frequency shift of FM signal                                              |

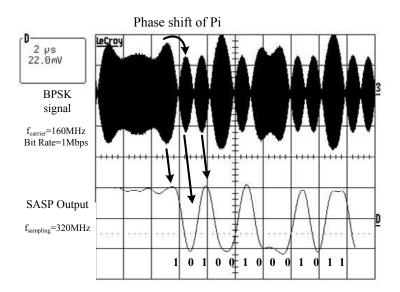

|      | BPSK modulation                                                           |

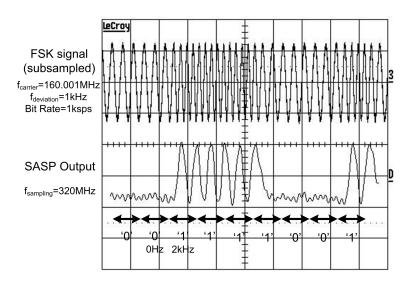

|      | FSK modulation                                                            |

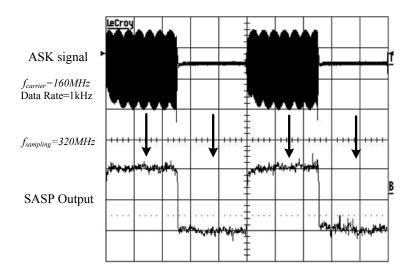

| 4.18 | ASK modulation                                                            |

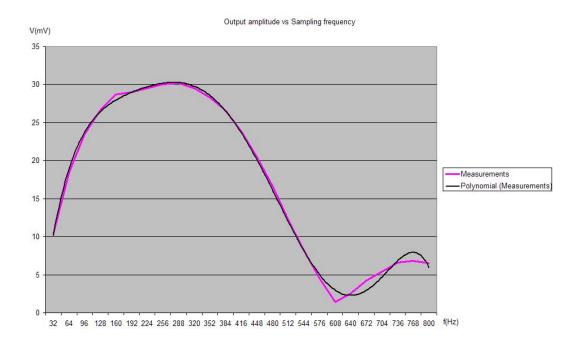

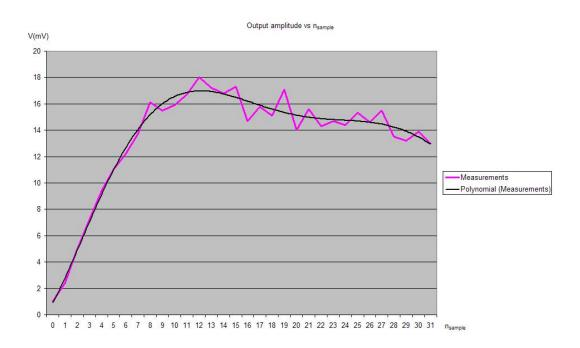

| 4.19 | Output amplitude vs $f_{\text{sampling}}$                                 |

| 4.20 | Output amplitude vs $n_{\text{sample}}$                                   |

| 4.21 | First proposed delay line architecture  | 143 |

|------|-----------------------------------------|-----|

| 4.22 | Second proposed delay line architecture | 143 |

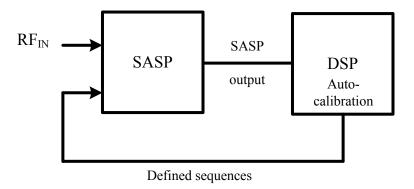

| 4.23 | SASP system auto-calibration            | 146 |

# List of Tables

| 1.1 | Wireless Communication Systems Characteristics                           |

|-----|--------------------------------------------------------------------------|

| 1.2 | Figure of Merit                                                          |

| 1.3 | Charge Coupled Devices Sum up                                            |

| 2.1 | Windows and Figure of Merit                                              |

| 2.2 | Operating states and switchs configurations                              |

| 2.3 | Comparison of number of samples at a given sampling frequency of 4GHz 78 |

| 2.4 | RF standards addressed by 65536-point SASP                               |

| 3.1 | Voltage loss vs $f_{\text{sampling}}$                                    |

| 3.2 | Simulated delay lines power consumption                                  |

| 3.3 | WU Coefficients                                                          |

| 3.4 | Weighting Unit Coefficients Application                                  |

| 3.5 | Weighting Unit Coefficients Simulation                                   |

| 3.6 | Simulated WU power consumption                                           |

| 3.7 | Binary code                                                              |

| 3.8 | Metals                                                                   |

| 3.9 | Power Consumption                                                        |

| 4.1 | Different power supplies                                                 |

| 4.2 | Digital part validation                                                  |

| 4.3 | Power Consumption under 1.4V                                             |

| 4.4 | SASPEPA Characteristics                                                  |

| 4.5 | Weighting Unit Coefficients extension                                    |

| 4.6 | Estimated Power Consumption                                              |

16 List of Tables

# List of Abbreviations

A/D Analog-to-Digital

**AAF** Anti-Aliasing Filter

AC Alternating Current

ADC Analog-to-Digital Converter

**AM** Amplitude Modulation

**ASIC** Application-Specific Integrated Circuit

BIST Built-In Self-Test

**BPSK** Binary Phase Shift Keying

**CCD** Charge-Coupled Device

**CDMA** Code Division Multiple Access

**CMOS** Complementary MOS

**DAC** Digital-to-analog converter

**DARPA** Defense Advanced Research Projects Agency

**DC** Direct Current

**DCS** Defense Communications System

**DFT** Discrete Fourier Transform

**DSP** Digital Signal Processor

**DUT** Device Under Test

**EDGE** Enhanced Data for GSM Evolution

**ENOB** Effective Number of Bits

FFT Fast Fourier Transform

FM Frequency Modulation

**FSK** Frequency Shift Keying

**GMSK** Gaussian Minimum Shift Keying

**GPRS** General Packet Radio Service

**GPS** Global Positioning System

**GSM** Global System for Mobile Communications

**HSDPA** High-Speed Downlink Packet Access

18 List of Tables

IC Integrated Circuit

IF Intermediate Frequency

**IFFT** Inverse FFT

**ISSCC** International Solid-State Circuits Conference

JTO Joint Program Office

JTRS Joint Tactical Radio System

LNA Low Noise Amplifier

LTE Long Term Evolution

MEMS Micro Electro Mechanical Systems

MIPS Million Instructions Per Second

MNOS Metal Nitride-Oxide Semiconductor

MOS Metal Oxide Semiconductor

MU Matrix Unit

**OFDM** Orthogonal Frequency Division Multiplexing

**PA** Power Amplifier

PCB Printed Circuit Board

PCS Personal Communications System

PLS Post Layout Simulation

PSK Phase Shift Keying

QPSK Quadrature PSK

QAM Quadrature AM

RF Radio-Frequency

SASP Sampled Analog Signal Processor

SDR Software-Defined Radio

SR Software Radio

SNR Signal-to-Noise ratio

T/H Track-and-Hold

UMTS Universal Mobile Telecommunications System

**UWB** Ultra-Wideband

VHDL Very high-speed integrated circuits Hardware Description Language

VHDL-AMS VHDL-Analog and Mixed-Signal

WCDMA Wideband CDMAWU Weighting Unit

# List of Notations

$f_{\mathbf{sampling}}$  SASP Sampling frequency

k  $n^{th}$  root of unity indix

N Number of voltage samples handled by the SASP

$n_{\mathbf{envelope}}$  Number of samples in a RF envelope

$n_{\mathbf{sample}}$  Frequency sample number in a DFT processing sequence

$T_p = N.T_{\mathbf{sampling}}$  Period of a processing sequence  $T_{\mathbf{sampling}}$  Sampling Period of the SASP

$r_{\mathbf{stage}}$  Stage number in the pipelined DFT  $[1, \log_4(N)]$

$W_N^k$  Twiddle factor

20 List of Tables

# Introduction

The recent increase in the demand for wireless devices has led to the emergence of various standards. Cellular systems are more and more required to accept different kinds of applications such as audio, graphic or video data. Mobile terminals are the place for a real multimedia convergence. For this reason multifunctional wireless devices are required. They are able to accommodate different wireless standards with different carrier frequencies, channel bandwidths, modulation schemes or data rates.

Multifunctional circuits and systems are part of the solution. They can integrate the concept of Software Radio (SR) in just one chip. A SR circuit can be tuned to any frequency band, select any reasonable channel bandwidth, and detect any known modulation. This thesis presents the design of a Radio Frequency Front-End receiver dedicated to SR for mobile terminals. This receiver is based on a Sampled Analog Signal Processor (SASP). The latter is placed between the antenna and the ADC in a receiver chain.

Chapter 1 presents the Software Radio concept. It emphasizes the technological bottleneck of a full Software Radio receiver chain. The receiver is composed of an antenna, an ADC and a DSP. But, to accept any RF standard, ADC and DSP have to deal with high signal resolution at RF frequencies. It leads to a very high power consumption unsuited to mobile terminals. The idea is to perform part of digital signal processing in analog. A state of the art of analog signal processing components is proposed.

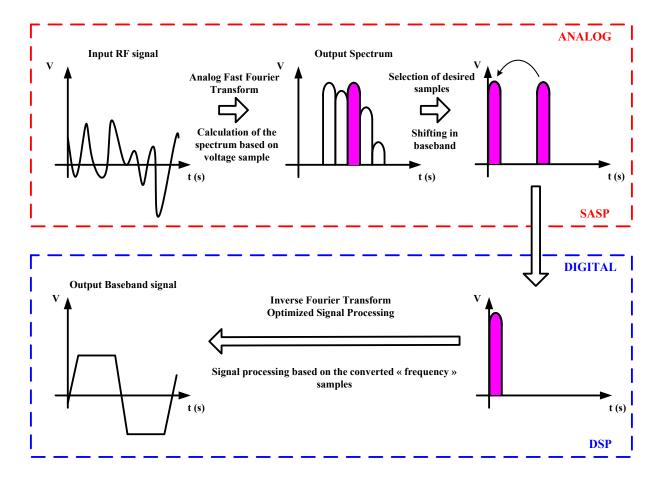

Chapter 2 exposes the principle of the SASP. It does basic analog operations on discrete time voltage samples. The purpose is to reduce the RF signal data rate before digital conversion. Analog operations give the opportunity to work directly at RF frequencies at an acceptable power consumption and to display a low frequency output signal. The SASP aims at processing the RF input signal spectrum. Only the spectral envelope of the desired RF signal is analogically selected and sent toward an ADC. To carry out the operation, the SASP implemented an analog Discrete Fourier Transform (DFT). Two parameters inherited from the DFT equation mastered

22 List of Tables

the SR requirements such as reprogrammability and flexibility: the sampling frequency  $f_{sampling}$  and the number of voltage samples N. Two applications are proposed to enhance SASP principle: concurrent reception enables to receive and shift to baseband several RF signals, frequency demodulation performs part of the digital signal processing in analog and participates to reduce the ADC input frequency.

Chapter 3 exhibits the SASP design. The goal is to validate the feasibility of the SASP with a demonstrator using 65nm CMOS technology of STMicroelectronics. This demonstrator handles 64 voltage samples. Each part of the system is detailed. The implementation is discussed and characteristics are given through behavioral simulations.

Chapter 4 concludes on measurements of two chips. They both confirm the physical feasibility of the SASP and identify technical points to be improved for an industrial product. A technological roadmap is paved for a Software Radio chip. Perspectives are given concerning the architecture, the design and the targeted characteristics.

### CHAPTER

1

# The Software Radio Concept

| 1.1 | Wire  | eless communication systems              | 24 |

|-----|-------|------------------------------------------|----|

|     | 1.1.1 | Wireless communication architectures     | 25 |

|     | 1.1.2 | Wireless communication standards         | 27 |

|     | 1.1.3 | Wireless communication market and trends | 28 |

|     | 1.1.4 | Conclusion                               | 30 |

| 1.2 | Soft  | ware Radio Background                    | 30 |

|     | 1.2.1 | Definition                               | 30 |

|     | 1.2.2 | History                                  | 31 |

|     | 1.2.3 | Software Radio Characteristics           | 33 |

|     | 1.2.4 | Technological Bottlenecks                | 35 |

|     | 1.2.5 | Software Defined Radio Architectures     | 40 |

| 1.3 | Ana   | log Signal Processing                    | 44 |

| 1.4 | Con   | clusion                                  | 49 |

Chapter 1 presents the Software Radio concept. The first part reminds RF transceivers architectures, RF standards and wireless devices market. The second part shows how telecommunication industry is faced with new challenges. It tends to integrate more and more functionalities in mobile terminals whereas technological bottlenecks prevent from designing low cost solutions. The Software Radio concept proposes new ways to success in a full multimedia convergence at the lowest price fulfilling constraints imposed by mobile terminals.

**Key words**: RF architectures, RF standards, multimedia convergence, software radio, analog signal processing

Wireless communication systems are faced with the emergence of various standards dedicated to voice transmission, data transfer and localization. The past decade has seen a fast evolution regarding the communication standards: their data rates have increased, their carrier frequencies are higher and their modulations are more complex. While integrating all these changes, mobile terminals tend to address several communication standards in just one handset. But, conventional architectures cannot challenge this multimedia convergence satisfying technological matters imposed by handsets at a lowest price. Thus, new architectures need to be studied in order to answer to mobile terminals constraints. This chapter presents the classical architectures of transceivers in the case of mobile terminals and an overview of the new solutions proposed by the Radio Frequency community to overcome technological issues.

### 1.1 Wireless communication systems

Transceivers architectures dedicated to mobile terminals have emerged in the 90's to answer wireless communications such as GSM. A continuous evolution of wireless systems has been led by an increasing demand of the market to design products which integrate more and more applications at the lowest price.

#### 1.1.1 Wireless communication architectures

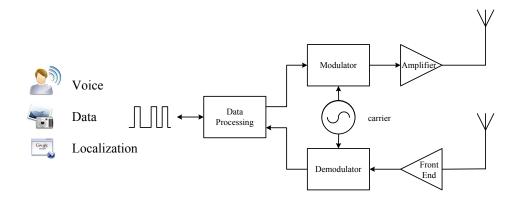

The aim of a wireless communication system is to receive and transmit information at high frequencies. A basic architecture can be summarized up as follow (Fig. 1.1) with two paths:

- A transmitting path: to send information (voice, data, localization), a digital signal encoding the information by a data stream is processed through a modulation scheme. It is then carried at RF frequencies (carrier frequency) and amplified in order to be transmitted.

- A receiving path: to receive information, RF signals are amplified, filtered, translated into baseband by a Front End. The signal is processed digitally to recover the information contained in the data stream.

Figure 1.1: Transceiver Architecture

#### 1.1.1.1 Emitter chain

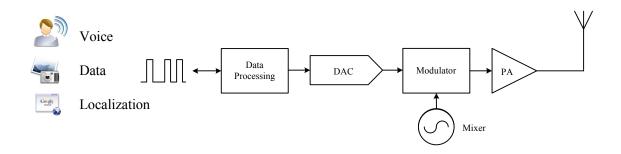

The emitter chain is composed by (Fig. 1.2):

- A Digital to Analog Converter (DAC).

- A Mixer to up convert the signal.

- A Power Amplifier (PA).

Digital information is encoded and modulated to be up converted at RF frequencies. Then, a PA amplifies the signal meeting the requirements given by international standards. This step is one of the most important, as amplification is a trade-off between linearity (signal quality) and power (communication range and power consumption). Designers are faced to issues like improving PA performances without increasing power consumption (limited in the case of a handset) and decreasing the PA yield.

Figure 1.2: Emitter Architecture

#### 1.1.1.2 Receiver chain

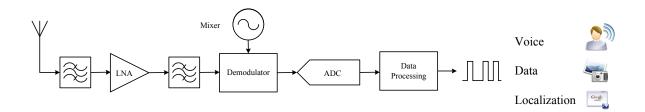

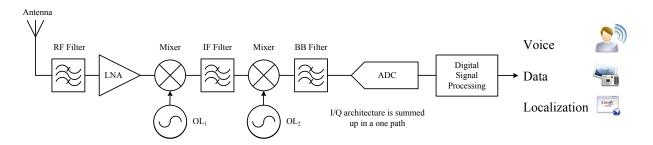

The receiver chain aims at receiving signals from the base station. The chain is composed by (Fig. 1.3):

- A Low Noise Amplifier (LNA).

- A Mixer to down convert the signal.

- An Analog to Digital Converter (ADC).

The LNA amplifies the received signal to be processed fitting the requirements. In fact, the signal received by the antenna is very weak and cannot be treated ad-hoc properly. LNA features (noise, gain) are crucial to guarantee a good functionality. The mixer down converts the RF frequency signal to intermediate frequencies or baseband. It is then converted into digital by an ADC. A DSP finally processes the signal to decode the information and transmit recovered data to the user through an analog interface (earphone, screen).

Figure 1.3: Receiver Architecture

low-IF or polyphase [2].

The principle exposed here is a general one. Several kinds of architectures are used to perform the reception. It is determined by a trade-off between parameters to maximize the reception. For instance, it can be cited: heterodyne, super-heterodyne, image rejection, homodyne (direct conversion or zero-Intermediate Frequency), low Intermediate Frequency, polyphase [1]. The super-heterodyne structure is the most used. But, the trend to integrate circuits on a single chip at a low power represents a real drawback of this architecture. At the same time, multistandard systems are claimed. It leads to search for more adapted topologies such as homodyne,

#### 1.1.2 Wireless communication standards

The wireless communication standards world is a world of diversity [3]. Historically, the GSM (2G) is the first standard to have dominated the cell phone market in 1992. In June 2008, it numbered 3 billion of users in the world. The native version operated at 900MHz and was extended to two other frequency bands at 1800MHz and 1900MHz. It is mainly used to transmit voice and data (SMS). The GPRS (2.5G) and EDGE (2.75G) standards are evolutions of the GSM. The same frequencies are used but the data rate is higher thanks to new modulation schemes (8-PSK). Multimedia services are thus proposed to users.

The successor of GSM is UMTS (3G). It has a high data rate and enables video transmission. While this new standard is appearing and bringing multimedia closer and closer to the final user, other standards provide better wireless communications between multimedia devices (Bluetooth and WiFi standards). Table 1.1 offers an overview of the standards nowadays used. It exhibits clearly the fast growth of wireless device market and the diversity of the technological constraints.

| Standards         | GSM900       | UMTS             | Bluetooth | WiFi (802.11b)   |

|-------------------|--------------|------------------|-----------|------------------|

| RX Band (MHz)     | 925-960      | 2110-2170        | 2448-2482 | 2412-2472        |

| TX Band (MHz)     | 880-915      | 1920-1980        | 2448-2482 | 2412-2472        |

| Channel Bandwidth | 200kHz       | 5MHz             | 1MHz      | 20MHz            |

| Modulation        | GMSK         | QPSK             | GFSK      | OFDM / QPSK      |

| Resolution (bits) | 14           | 9                | 12        | 7                |

| Data Rate         | 14.4-115kbps | 384kbps to 2Mbps | 723kbps   | 11Mbps to 54Mbps |

| Application       | Voice        | Data/Voice       | Data      | Data             |

Table 1.1: Wireless Communication Systems Characteristics

#### 1.1.3 Wireless communication market and trends

#### A growing diversity

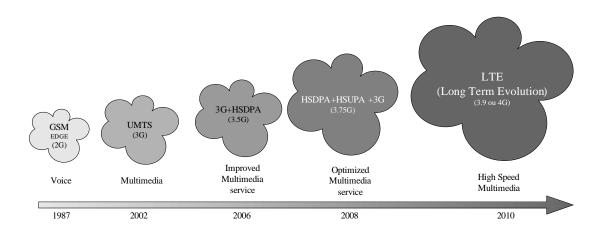

With all the sophistication that characterizes today's mobile phones, it is easy to forget that the handset, at core, is a radio set! Traditionally, radios have been implemented entirely in hardware thanks to analog circuits, with new waveforms added by integrating new hardware. However, last generation of handsets needs to support all of the following wireless standards: GSM, GPRS, EDGE, WCDMA, HSDPA, LTE, GPS, mobile TV, WiFi, Bluetooth and UWB (Fig. 1.4). Besides, every new standard added on the market is faced with faster and faster introduction (Fig. 1.5) whereas multi-mode handsets must be able to operate across GSM and CDMA networks. The number of waveforms to be supported is consequently considerable, various and becomes hard to handle. The trend can be summed up by a multimedia convergence on a lonely handset.

Figure 1.4: Evolution of the GSM standard to LTE

#### Telecommunication industry challenges

Telecommunication industry dilemma is to maintain a constant (or lowest) production cost and handset size while integrating more and more functions with a maximum reactivity. Figure 1.6 depicts the reduction of Integrated Circuit (IC) footprint in cell phones during the first years of a product. GSM is here compared to a dual mode chip (GSM and UMTS). The industry is answering to new technological matters faster when new solutions appear. For instance UMTS came to maturity more than two times faster than the GSM. As said before, it can be seen than size and complexity of discrete components are tried to be maintained as stable as possible. Thus, the trend is to integrate more features for free thanks to miniaturization based upon multiple chip package, high density package, or novel RF architectures.

Figure 1.5: Global Subscribers by Technology

Figure 1.6: Components parameters evolution in Mobile Phones

For this reason, integrating additional radio hardware is impractical beyond a point because it increases the handset size, complexity and price. As mentioned before, novel RF architectures are to be created. Software-Defined Radio (SDR) and Software Radio (SR) are concepts aiming at integrating a RF architecture able to handle any kind of RF standards in only one chip. The attraction of SDR/SR is its ability to support multiple waveforms by re-using the same hardware while changing its parameters by software. This has enormous benefits for handset size, cost, development cycle, upgrade and interoperability. Whereas the demand of SDR/SR product is very strong, technical challenges are to be solved by telecommunication industry. The next section exposes the most important obstacles to be solved to design a handset based on SDR or SR concepts.

#### 1.1.4 Conclusion

This overview of wireless domain is concluded by two main observations that exhibit the need of rupturs in RF architectures design.

User habits: Handset needs to have evolved from the mere phone call to multimedia services.

A multimedia convergence is required by the omnipresence of communication device in our every day life. Telecommunication industry and consumers claim for a one-product solution.

**Network diversity:** As the wireless market has exploded, various telecommunication standards can be found. This diversity implies a technological challenge to merge any standard in a one-product solution.

The classical way of building Radio architectures is over. To answer to the new constraints exposed previously, new structures are to be found.

### 1.2 Software Radio Background

The wireless industry is faced with the multimedia convergence in mobile terminals, looking for new RF architectures. Joseph Mitola exposed for the very first time the concept of Software Radio (SR) in 1995 [4]. The concept of SR aims at designing a reconfigurable radio architecture accepting all cellular and non-cellular standards working in a 0 to 5 GHz frequency range. Technical challenges need to be solved to address this concept. This section presents the concept of SR, its technological bottlenecks and an overview of existing SDR RF architectures dedicated to mobile terminals.

#### 1.2.1 Definition

#### Principle

A definition of Software Radio is a "Radio in which the entire physical layer functions are software defined". A particular case of that principle is the concept of Software Defined Radio (SDR) defined as a "Radio in which some or all of the physical layer functions are software defined", commonly adopted by the SDR industry association [5].

A Software-Radio receiver architecture is depicted in figure 1.7. The concept is to bring as close as possible the Analog to Digital Conversion to the antenna. Thus, the ideal system is composed by an antenna, an ADC and a DSP. The DSP is reconfigurable by software and can address

any standard. This architecture can adapt itself to any kind of radio context and treat any RF signal. But, nowadays technological bottlenecks prevent from realizing such a utopian system. The Analog to Digital Conversion, if done directly after the antenna requires a high resolution at high sampling frequencies. It would consume a lot of power which is not compatible with mobile terminal battery life. Intermediate solutions are studied to achieve the Software Radio concept.

Figure 1.7: Ideal Software Radio receiver architecture

#### From Software-Defined to Software Radio

Joseph Mitola defined SDR as follow: A Software-Defined Radio (SDR) is a radio that can accommodate a significant range of RF bands and air interface modes through software. For the ideal software radio, that range includes all the bands and modes required by the user/host platform [6]. As explained before, researches tend to bring closer and closer the ADC to the antenna in RF transceivers (Fig. 1.1). SDR is consequently a step toward SR. SDR is characterized by:

- A narrow band analog signal processing (under 20MHz).

- Baseband digital signal processing.

SR is characterized by:

- A wide-band analog signal processing (over 2GHz).

- Full RF spectrum covered.

#### 1.2.2 History

The US Army is the first to study SDR projects. The purpose was to secure radio communications between operational units on a hostile battlefield. Radio communications had to be reconfigured rapidly in order to prevent from being spied enemies. Defense Advanced Research Projects Agency (DARPA) financed researches. Project "Speakeasy" gave the first result at the

beginning of the 90's. The evolution was first to handle several standards on a 2MHz - 2GHz frequency band and reconfigure "on the fly" the communication device with one known standard. It went on the implementation of new standards through known standards in order to switch rapidly on a new way of communication. This necessity found obviously all its meaning in the military market.

#### A military market

The military market is more and more interested in that technology thanks to the differences existing between allied armies or any coalitions. At the end of the 90's, US army established the JPO (Joint Program Office) to launch JTRS (Joint Tactical Radio System) [7]. Today, JTRS finances projects on Software Radio to be operated in the US army at a term of 10 years. Companies start working on Software Radio systems at the demand of many countries. Several armies in the world are to be equipped in Software Radios, following the US army strategy.

#### A commercial market

Software Radio is not only a military subject. The wireless industry gave rapidly an interest to SR. An international organization, called SDR Forum promotes researches, development and use of SR technologies concerning communication systems. It brings together companies, universities and governmental organizations to give direction to researches and exchange ideas. The final aspiration is to provide worldwide, flexible and low cost handsets.

#### A civil market

An other market targeted by SR systems is the civil and emergency one. It took all its importance since the 9/11 attacks. Police and Fire departments, emergency units are able to inter-communicate thanks to a unique way of communication as coordination is an essential key in case of emergency. The fight against terrorism increased the demand of technological solutions to share information securely and as fast as possible.

#### First researches

Researches on SDR were brought by reconfigurable architectures (Fig. 1.8). Each part of the architecture is reconfigurable and thus can be changed while required. Filters scale on the best bandwidth, mixers down convert at the chosen frequency in order to optimize the A/D conversion. The DSP manages the configuration of each element.

Figure 1.8: Realistic Software-Defined Radio receiver architecture

Despite the concept of Software-Defined Radio is approached and may appear easy to be explained and designed, the system developed consumes a lot of power and cannot be adapted to a handset and at any kind of standards. Technological bottlenecks are clearly identified and pave the way to develop a Software Radio mobile terminal. An effort has to be done to work on new architectures. That is why each market is financing and pulling up researches for their interests.

#### 1.2.3 Software Radio Characteristics

Our researches are focused on commercial handsets. Software Radio brings flexibility and adaptability. Many gains are expected by telecommunication industry:

Gain of compatibility: a common system can address any kind of standards and thus can be used wherever in the world. A mass production leads to a cost reduction.

Gain of production time: research and development time is optimized between the apparition of a new standard and its use. As a basic architecture is to be designed, only updates (design, software) are required to accept new standards.

Gain of performance: a SR system is able to reconfigure itself depending on the context (geographical, data rate, etc). It can adapt the data rate and the bandwidth using the most efficient standard.

Performances of SR are not only technological. Industrial efficiency and easiness are thus proven.

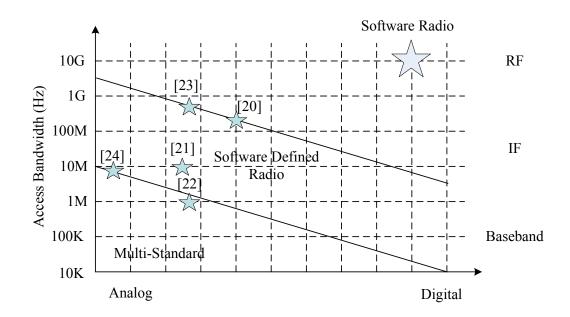

A graphical classification is proposed to point out the degree of flexibility of an architecture (Fig. 1.9). It is determined by the access frequency and the addressed bandwidth performed

into analog domain as digital part is the technological bottleneck. It can determine if a system is either a Software-defined or a Software Radio. The ideal Software Radio receives and handles a wide-band of RF signals. The architecture to be designed in this thesis is a Software Radio architecture.

Figure 1.9: Software-Defined to Software Radio Classification

#### 1.2.4 Technological Bottlenecks

To achieve the development of a SR RF device, 3 technological bottlenecks are described, from the most difficult to the less difficult to overcome.

#### 1.2.4.1 A/D conversion

SR receiving chain has to digitize as close as possible to the antenna any RF signal. A 0 to 5GHz RF band is the widest band to target in order to cover the entire RF spectrum. So, the SR ADC requirements are given by:

- At least a 10GHz sampling frequency ( $f_{\text{sampling}}$ ).

- A 16 Effective Number Of Bit  $(N_b)$  is required to accept any dynamic range among all defined RF standards.

- The power consumption (P(W)) is directly linked to the sampling frequency. The higher the frequency, the higher the power consumption. In a context of mobility, the battery life is the major parameter to take into account.

- Silicon area  $(A(mm^2))$  is important as it determines the component cost.

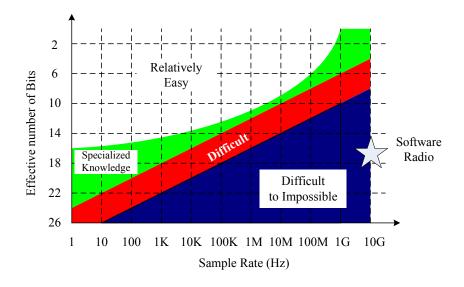

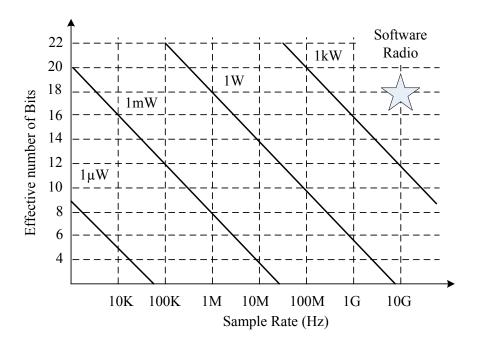

Given the figure 1.10, such an ADC at low power consumption (Fig. 1.11) [8], at high frequencies with an acceptable accuracy is nowadays not feasible.

Figure 1.10: ADC issues

Extrapolating current A/D converter characteristics, the A/D converter for SR would consumes about 1 kW (Fig. 1.11). This is far too much for handsets. The progress in A/D converters at the same power level (at the same sample frequency) is about 1.5 bit in 8 years [9]. As the power consumption issue depends on frequency and resolution, the next paragraph gives clues to understand the technological bottleneck [10].

Figure 1.11: ADC power consumption

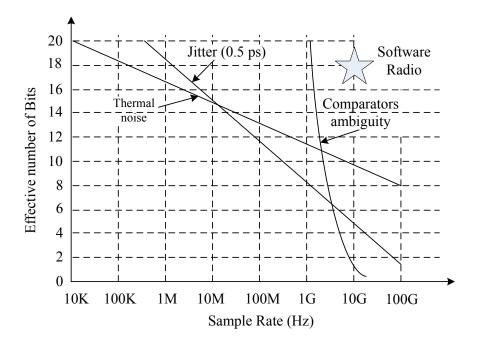

#### Limiting factors

Two main limiting factors are thus exhibited: frequency and resolution. Power consumption is considered as depending on these two factors. A/D converters performances are mainly limited by three physical phenomena: thermal noise, jitter and quantization (minimal resolution) (Fig. 1.12). Currently, ADCs found on the market have specifications approximately from 500kHz with a 24-bit resolution to 2GHz with a 8-bit resolution. These specifications are under the requirements of an ideal Software Radio system (Fig. 1.10). It can be estimated that at least 15 years of works are required to achieve a low power ADC answering to SR constraints, if one day feasible!

Figure 1.12: ADC limitations

Two parameters are commonly defined as a figure of merit to evaluate converters:

- $F_m$  which take into account all the variables of an ADC.

- $F_t$  which is limited to technological matters.

They are given by:

$$F_m = \frac{2^{N_b} \cdot f_{\text{sampling}}(MHz)}{P(mW) \cdot A(mm^2)}$$

(1.1)

$$F_t = \frac{P(W)}{2^{N_b} \cdot f_{\text{sampling}}} \tag{1.2}$$

These two parameters reflect the "cost" of an ADC in the case of SR. For instance,  $F_m$  exhibits the silicon area  $(A(mm^2))$  impact on the circuit, considering technological cost (the bigger, the more noisy the circuit is) and considering the price (the smallest, the cheapest, or at least the same price). If A decreases,  $F_m$  increases.

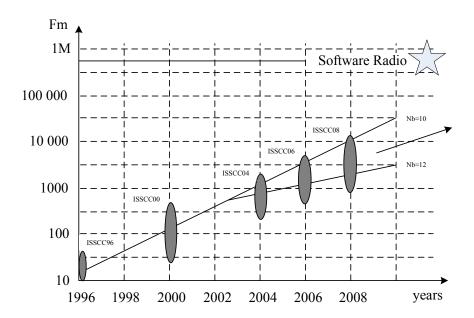

Figure 1.13 and Table 1.2 show the evolution of ADCs found in literature of ISSCC. It depicts the evolution of converters figure of merit in the past decade and thus draws directions for the next decade. It exhibits the hard trade-offs between resolution,  $f_{\text{sampling}}$  and power consumption (e.g. [11] [12]). Two observations are made:

- The progression of  $F_m$  is constant, it is done whereas  $N_b$  remained low at 10.

- $F_m$  is slowing down while  $N_b$  is increased.

This observation enables to draw a perspective of 15 years at least required to target the goal of  $F_m = 660000$  with  $N_b = 16$ .

| Parameters                   | Minimum | Typical | Maximal | ISSCC'04 [13] | ISSCC'06 [11] | ISSCC'08 [12] |

|------------------------------|---------|---------|---------|---------------|---------------|---------------|

| $N_b$                        | 12      | 14      | 16      | 10            | 9.5           | 11            |

| $f_{\rm sampling}({ m MHz})$ | 20      | 40      | 10 000  | 160           | 32            | 200           |

| P(mW)                        | 20      | 10      | 100     | 122           | 22            | 180           |

| $A(mm^2)$                    | 5       | 2       | 10      | 1.7           | 0.3           | 1.1           |

| $F_m$                        | 820     | 32 768  | 655 360 | 787           | 3500          | 2068          |

| $F_t(fJ)$                    | 244     | 15      | 0.15    | 747           | 949           | 630           |

Table 1.2: Figure of Merit

Figure 1.13: ADC Figure of merit

## Conclusion

Technical informations given in this part show how critical is the A/D conversion. ADCs suiting strong SR requirements are not expected to be achieved before 15 years or more. Designers must find new architectures which relax ADC requirements to achieve a SR system [10].

#### 1.2.4.2 Digital Processing

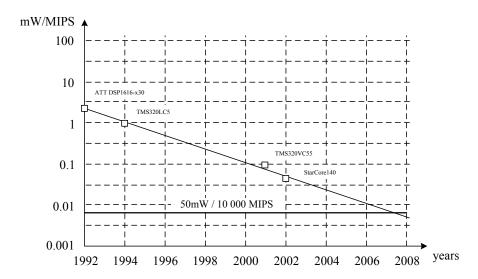

Considering an A/D conversion feasible at RF frequencies (>10GHz), a DSP should handle 16-bit words at 10GHz. This is equivalent to more than 600Gops which implies a minimal power consumption of 200W. This is not compatible with a handset limited by its battery life. Considering defined digital functions in the case of an ASIC, Moore's law is providing good hope to lower the huge power consumption coming from millions of instructions per seconds (MIPS). But, this progression is limited like ADCs and a 15-year perspective to obtain such chip is a very optimistic vision. In general, the performance of DSP will keep on increasing as chip sizes are reduced and the number of gates increased. New structures are also expected to improve DSP performance. Some technics such as decimation could lower the working frequency despite the fact that a part of the calculation would remain at RF frequencies. Figure 1.14 presents the power consumption per MIPS for DSP on the market thanks to a survey done in [14]. The barrier of the 50mW at 10 000 MIPS is said to be a step toward SR. It also exhibits how long the technical roadmap to a DSP adaptated to SR architectures is.

Figure 1.14: Power consumption per MIPS for DSP the last 20 years

## 1.2.4.3 RF Front End

RF Front End is also part of the technological bottleneck. It is composed by pure analog functions: LNA, Power Amplifier, Filter and Antenna. SR concept imposes these functions to be as wide-band as possible (0 to 5GHz typically). This section presents an overview of the technical difficulties to design such functions in the case of a SR receiver.

#### Antennas

A very wide-band antenna is required to cover the entire RF spectrum. Studies are done on "meta-materials" or MEMs (micro-switches) to target the unique SR antenna. But, a SR antenna is nowadays quite impossible to be realized and a panel of antennas, specifically designed for optimized performances are preferable.

# Amplifiers

LNA and PA topologies are based on few active (transistors) and passive components (inductors, capacitors). Technological reduction leads to decrease parasitic elements but, in the meantime, it lowers inductors performances. This enables to maintain good performances on dedicated devices which are narrow band and only used for specific standards. In the case of SR, LNA must be very wide-band (0 to 5GHz). Capacitors and inductors parasites must be as low as possible to guarantee a maximal linearity bandwidth. That is why new topologies are proposed to overcome these technological issues [15, 16].

#### Conclusion and Technological strategies

This section has exhibited the technological bottlenecks constrained by mobile context. The power consumption is the main one. It is driven by the A/D conversion and the digital signal processing. Consequently, researches are to be focused on exploring new structures in rupture with the traditional ones. As the digital domain is an obstacle to a SR system realization, analog signal processing becomes a key. The strategy consequently adopted in this work to develop a SR chip is to design an Analog Signal Processor. The next part offers a state of the art of SDR architectures to highlight difficulties encountered by designers. It will draw a technical strategy for an analog signal processor conception.

#### 1.2.5 Software Defined Radio Architectures

SDR and SR architectures only appeared the past few years. Researches are wide-spread and it is hardly possible to summarize SDR and SR works. This part gives clues to understand directions taken by designers to overcome technological bottlenecks. Solutions are proposed to bring closer and closer the digital part to the antenna. They are presented from the less flexible to the most advanced toward a SR system.

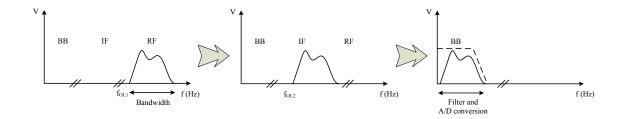

### 1.2.5.1 Baseband Conversion

The first step toward a SR system is an analog and continuous translation into baseband of RF signals [17]. A direct conversion architecture processes analogically the frequency translation

thanks to mixers (Fig. 1.15). Once in baseband, the signal can be converted into digital after filtering (Fig. 1.16). The major advantage is relaxed ADC requirements (low frequency) but at the cost of narrowband SDR systems, limited by mixers and filters characteristics. This architecture is considered as multi-standard.

Figure 1.15: Software Defined Radio by Baseband Conversion Architecture

Figure 1.16: RF signal to baseband translation by Baseband Conversion Architecture

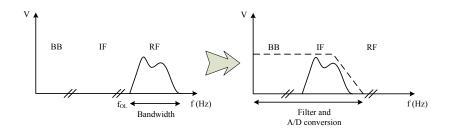

#### 1.2.5.2 IF Conversion

The idea presented before is extended to IF frequencies. The A/D conversion is processed at IF. The baseband translation is thus done digitally and only one mixer is required to down convert RF signal to IF. The number of reconfigurable parameters is consequently reduced to the only mixer but stronger requirements are imposed to the ADC such as a wider access band [18].

Figure 1.17: RF signal to IF translation by IF Conversion Architecture

#### 1.2.5.3 Sub-sampling

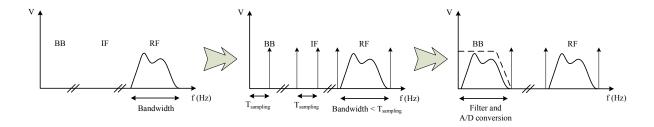

The sub-sampling principle is to keep the idea of an ideal SR system (Fig. 1.7). The signal is sub-sampled to be converted into digital. It implies an aliasing effect. Thus, the RF signal is translated into baseband thanks to aliasing (Fig. 1.18) [19]. Once in baseband, the signal is filtered and converted into digital.

Figure 1.18: Software Defined Radio by sub-sampling

Despite the easiness of this principle, three main drawbacks are mentioned:

**Filter:** As described in figure 1.18, once in baseband the signal is filtered. A very selective filter has to be chosen to avoid any interference with neighbor channels.

**ADC** bandwidth: The maximal bandwidth of the ADCs must address any channel bandwidth (while guaranteeing other requirements: resolution, ...). Hopefully, ADC requirements are relaxed thanks to the baseband translation, and that drawback does not appear as unfeasible.

**Dynamic loss:** The Signal to Noise Ratio (SNR) is decreased. The dynamic range is reduced. This is the major drawback of such a system.

The sub-sampling solution is an interesting solution for SDR but technological issues are still strong to be solved. Besides, this system is narrowband and can concern only one standard at a time. Among the three solutions listed here, it is the closest to a SR architecture. The technical idea of sampling the signal directly at RF frequencies in order to keep any degree of flexibility is retained to design a wide-band SR system.

#### 1.2.5.4 State of the Art

This section presents a state of the art of SDR architectures and technological ideas to provide reconfigurable structures. Five papers are chosen to give an overview of the recent researches in the domain.

Figure 1.19: Software Defined to Software Radio State of the Art

- [20] proposes a receiver which makes use of a windowed integrator to perform charge sampling, which provides inherent anti-aliasing. The approach is multi standard. Programmable decimation filters attenuate unwanted channels and scale on the desired signal. It addresses both narrow and wide-band standards.

- [21] presents a demonstrator that receives both Bluetooth and HiperLan. Despite only two standards are targeted by the chip, the paper exposed the problems encountered for a SDR design. The two selected standards are different in terms of frequency band, signal bandwidth and modulation types. Challenges implied by the wide range of frequencies covered are exhibited. Main requirements are explained: ADC, LNA, mixer, antenna. A multi-standard architecture is shown.

- [22] depicts a discrete-time receiver. It is dedicated to Bluetooth standard. The down-conversion is processed analogically thanks to a discrete-time analog signal processing. As proven the feasibility of this architecture, it is proposed to extend it to meet requirements of several standards.

- [23] describes a full SDR receiver. It plays on the aliasing effect, such as [20], by a windowed integration. The receiver acts as a signal conditioner for the ADC by emphasizing only the wanted channel. The ADC requirements are relaxed thanks to analog signal processing. One step is done toward SR, overcoming the A/D technological bottleneck. The chip designed is able to handle GSM and 802.11g modes.

• [24] offers a discrete time analog signal processor as an alternative to the DSP. It means that a part of the processing realized normally into digital is moved to the analog part. The proposed system is a sampled-data system. It exposes the advantages, such as the suitability to real time applications, the trade-off between speed and accuracy. Switched capacitor array is proposed to perform analog operations.

This selection draws the trend in the design of SDR architectures: researches are not only focused on traditional structures with reconfigurable elements but are also oriented toward new structures. Multi-standard era is arrived at its maturity and it is common to find chips dealing with several standards [21]. As a great part of the job is still to overcome the A/D technological bottleneck, solutions must be found to relax ADC requirements. Discrete-time analog signal processing is proposed to be one of the solutions. The next part offers an overview of architectures tending to bring closer the digital part to the antenna and a state of the art of analog signal processors as a technical solution to new RF structures.

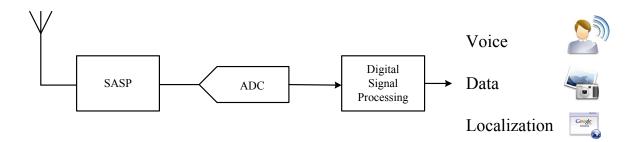

# 1.3 Analog Signal Processing

This thesis presents the design of a mixed signal architecture to overcome the A/D-conversion bottleneck. The RF signal is pre-conditioned analogically by a Sampled Analog Signal Processor (SASP) located between the LNA and the ADC (Fig. 1.20). The SASP does basic analog operations on discrete time voltage samples. The purpose is to reduce the RF signal data rate before digital conversion. The signal frequency has to be lowered. Analog operations give the opportunity to work directly at RF frequencies at acceptable power consumption and to display a low frequency output signal.

Figure 1.20: Proposed SR architecture

# **Analog Applications**

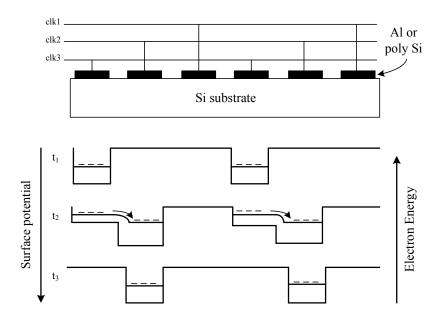

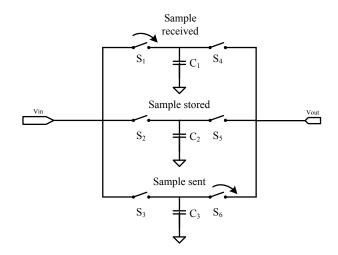

Sampled analog circuits are designed since the 70's. They were very used before the domination of digital circuit and gave many applications. A study on Charge Coupled Device (CCD) is a starting point of exploration on analog signal processing architectures. CCD was first introduced by Boyle and Smith [25]. It consists on storing charge in potential wells created at the surface of a semiconductor and moving the charge over the surface (Fig.1.21). Clock timing exhibits the moving charge in three operating phases. The number of carrier in a charge represents the value of the sampled signal. This is a continuous value. CCD enables integrating on a single chip capacitors, MOS switches and MOS sensors. A smaller silicon area is thus used and a higher yield is performed. One of the main interest in CCD is the low dissipated power because of the big part of capacitive device.

Figure 1.21: Charge Coupled circuit in 3 working phases

Many functions are designed thanks to this technology during the 70's. The easiest analog signal processing circuit designed with CCD is an input and an output, i.e. a delay line. Considered as a basic function, a delay line can give birth to more complex applications:

**Delay lines:** Delay lines are the first circuit designed thanks to CCD. The delay is provided thanks to the propagation time of the charges. It was mainly used for television applications as image correction circuits to delete ghost images [26].

**Filters:** One of the most successful application is discrete filtering. For instance, in [27], techniques are presented for making transversal filters using CCD. In a CCD transversal filter,

the delayed signals are sampled by measuring the current flowing in the clock lines during transfer, and the sampled signals are weighted by a split electrode technique (Fig. 1.22). Examples are given of CCD filters that are "matched" to particular signaling waveforms, and the limitations of charge-transfer devices (CTD) in matched filtering applications are discussed. Finally, the application of CTD transversal filters to other signal processing functions is debated.

Figure 1.22: Block Diagram of a Transversal Filter

[28] displays an other approach. It shows a programmable analog transversal filter disclosed for processing analog signals and for receiving a series of discrete analog signals to be delayed by increasing periods and applied to the outputs of a CCD, and a plurality of MNOS memory devices. CCD and MNOS devices are coupled to the taps of the CCD and programmed so that the output of a CCD tap is weighted by a particular factor (dedicated to filtering in that case). This particular factor is, as it appears today, the first step toward a discrete analog signal processor. In fact, the factor (if it can be changed) can lead to different application not only as filtering but also as Fourier Transform, correlators and adaptive filters.

**Resonators**: Resonators are applied to filtering applications with a high quality factor. [29] exhibits a discrete analog Chebyshev filter. [30] shows a passive CCD resonator as a recursive CCD building block with a high-Q band pass filters. Advantages of this approach are an extremely low sensitivity of the center frequency which is determined by an external

clock frequency, a relative bandwidth which does not depend on the center frequency but is controlled by a capacitance ratio.

Correlators: An analog correlator performs the convolution of two analog functions. It can lead to a hardware economy in complex signal processing circuit. A basic structure can be found in [31] and depicted in figure 1.23. A 20-stage analog CCD correlator has been constructed in [31]. Four quadrant analog multipliers have been used to combine the voltages from CCD taps to produce a correlation output. Multipliers achieve 1% linearity. Correlators are a new step toward complex analog signal processor because of their flexibility given by an operation between two variables.

Figure 1.23: Block Diagram of a Correlator

Chirp Transform: It is a signal processing algorithm which enables to process z-transform of a sampled signal. As described in [32], the Chirp Transform is based on CCD Correlators and CCD Delay Lines (Fig. 1.24). The design of complex applications thanks to basic ones is demonstrated. The Chirp Transform validates the transformation of a temporal signal into another domain (here z-domain). New applications can be envisaged in optimized domain, for instance in the spectral domain [33, 34, 35, 36]. That point is crucial in the research of disruptive architectures as it allows dreaming to new structures offering best requirements.

Figure 1.24: Block Diagram of a Chirp Transform

| References  | [26]        | [27]   | [29]      | [30]      | [31]       | [36] | [34]  |

|-------------|-------------|--------|-----------|-----------|------------|------|-------|

| Application | Delay Lines | Filter | Resonator | Resonator | Correlator | FFT  | FFT   |

| Year        | 1979        | 1973   | 1981      | 1981      | 1976       | 1978 | 1975  |

| $f_{max}$   | -           | 20MHz  | 4.75MHz   | 100kHz    | 5MHz       | 1MHz | 10MHz |

Table 1.3: Charge Coupled Devices Sum up

Researches in the 70's on CCD in the case of analog signal processing enable to offer a wide range of applications. Table 1.3 gives an overview of these applications and their maximal frequency of operation. Thus, discrete time analog signal processing can be a solution to find new architectures dedicated to SDR or SR to overcome the A/D technological bottleneck. If several megahertz was the maximal frequency and thanks to technology improvements, circuits designed 25 years ago may be scaled in the most recent technology and find an application at gigahertz frequencies. It allows thinking that RF functions can be processed directly in the analog domain. All constraints on the ADC and DSP are relaxed because major part of the signal processing is shifted in analog domain. A Sampled Analog Signal Processor (SASP) is technically feasible and its goal to relax ADC and DSP requirements can be considered to meet the requirements of Software Radio concept.

1.4. Conclusion 49

# 1.4 Conclusion

Telecommunication industry claims for new RF architectures. It is faced with the diversity and the multimedia convergence in mobile terminals. A concept called Software Radio brings the flexibility required by the market constraints. But, in the case of handsets, technological bottlenecks prevent from realizing this concept. The A/D conversion is the crucial part but it is limited by the current technology and the high power consumption. Hence, new analog architectures are explored. This thesis is focused on a discrete time, analog solution. State of the art has demonstrated the feasibility of discrete time analog signal processors. A Software Radio chip called Sampled Analog Signal Processor (SASP) is to be designed in the most recent technology from STMicroelectronics. The SASP processes RF signals and displays information at low frequency to an ADC. This chip is able to handle any RF signal and can reconfigure itself to accept any RF standard.

Technical options retain to implement a hardware **algorithm** thanks to **discrete time analog voltage samples** processing. Chapter 2 presents the chip architecture and the algorithm used. Chapter 3 depicts behavioral simulations and schematics design. Chapter 4 describes the chip layout, the technical issues and measurements.

# Chapter

2

# Sampled Analog Signal Processor

# Contents

| 2.1 | Prin  | ciple                             | 52        |

|-----|-------|-----------------------------------|-----------|

|     | 2.1.1 | Analog Signal Processor Principle | 52        |

|     | 2.1.2 | Frequency Translation             | 53        |

|     | 2.1.3 | A Fourier Transform               | 56        |

| 2.2 | A Fa  | ast Fourier Transform             | 57        |

|     | 2.2.1 | The Cooley-Tukey algorithm        | 57        |

|     | 2.2.2 | A pipelined DFT                   | 60        |

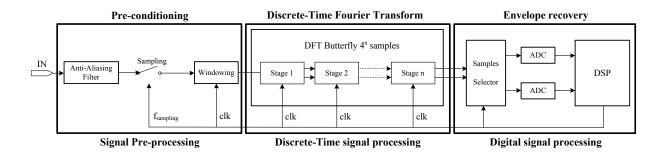

| 2.3 | Arch  | nitecture                         | 67        |

|     | 2.3.1 | Signal pre-processing             | 67        |

|     | 2.3.2 | DFT implementation                | 73        |

|     | 2.3.3 | Post-signal processing            | 76        |

| 2.4 | A So  | oftware Radio System              | <b>78</b> |

|     | 2.4.1 | Concurrent reception              | 78        |

|     | 2.4.2 | Frequency demodulation            | 79        |

| 2.5 | Con   | clusion                           | 82        |

Chapter 2 presents the principle of the Sampled Analog Signal Processor (SASP). A state of the art has exposed the challenges of a Software Radio system. As many technological bottlenecks need to be overcome, an idea is to designed a discrete analog signal processor. The main bottleneck of the A/D conversion is thus avoided and a lower processing speed can be envisaged concerning the digital part of the architecture. The SASP aims at selecting a spectral envelope of a RF signal among all RF signals. To reach this target, the SASP processes analogically the RF input signal spectrum thanks to an analog Discrete time Fourier Transform (DFT). Once the spectrum processed, voltage samples representing the spectral signal envelope to be treated are converted into digital. The selection of few voltage samples among thousands replaces the classical mixing and filtering operations. It reduces the A/D conversion frequency from GHz frequencies to MHz ones. Algorithm and design strategy are presented. Finally, applications are proposed.

**Key words**: Sampled Analog Signal Processor (SASP), Discrete Fourier Transform, frequency translation, concurrent reception, frequency demodulation

# 2.1 Principle

The Sampled Analog Signal Processor (SASP) principle will be presented. This designed is challenged by two ways:

- Discrete time analog voltage samples are used to analogically process RF signal.

- A Fourier Transform is the implemented algorithm to address the Software Radio concept.

This section presents the principle of the SASP.

# 2.1.1 Analog Signal Processor Principle

A mixed signal architecture is proposed to overcome the A/D-conversion bottleneck. The RF signal is pre-conditionned analogically by the SASP located between the antenna and the ADC (Fig. 2.1). The SASP does basic analog operations on discrete-time voltage samples. The

2.1. Principle 53

purpose is to reduce the RF signal data rate before digital conversion. The signal frequency has to be lowered. Analog operations give the opportunity to operate directly at RF frequencies at an acceptable power consumption given by mobile terminals constraints and to display a low frequency output signal.

Figure 2.1: Proposed SR architecture

In order to lower the output data rate, the idea of frequency translation was chosen.

## 2.1.2 Frequency Translation

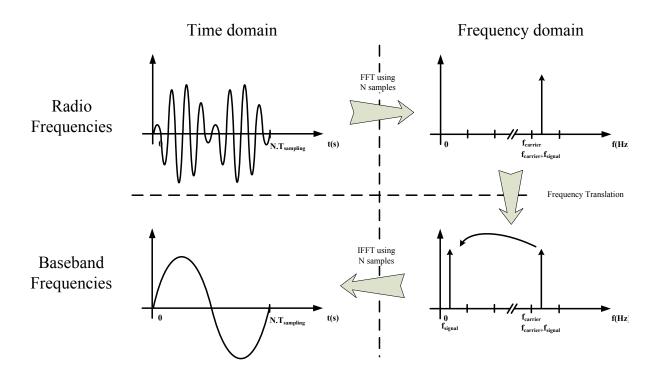

The SASP principle is based on the frequency translation (Fig. 2.2). The idea is to work in frequency domain instead of working in time domain. The constatation is that a RF signal envelope varies slowly compared to its carrier frequency. Signal processing on the RF signal envelope is focused. Given the criterium of reconfigurability constrained by SR, the SASP aims at processing any RF signal envelope in a 0 to 5GHz frequency range. Consequently, it is decided to work on all the RF frequency spectrum.

The principle of the SASP is to receive any RF signal. It processes analogically a Fast Fourier Transform (FFT) with discrete time voltage samples. Voltage sample carry out analog signal processing. They are the way to transform a temporal discrete signal in a frequencial signal. The frequencial signal is displayed in the time domain. A frequency image of all the RF spectrum is thus given. The information of RF input signal is still contained in discrete voltage samples.

Figure 2.2 exposes the purpose which is to extract the desired input signal spectrum envelope by recovering its spectrum. The RF signal is sampled and transformed. Among thousands of voltage samples, only the ones representing the RF signal envelope are sent out towards an A/D converter (Fig. 2.3). The selection provides a frequency translation as once in digital domain, the signal is considered to be baseband. An Inverse Fast Fourier Transform (IFFT) or an optimized signal processing is done to demodulate the RF signal.

Figure 2.2: Principle of the frequency translation

The goals of SR are fulfilled thanks to 2 major choices:

- The FFT enables to switch from time to frequency domain. All the RF spectrum is considered and any RF signal can be thus processed. The system is consequently wideband.

- Discrete time voltage samples guarantee the signal resolution. Their selection before the A/D conversion reduces the data rate and requires a low frequency conversion and a low working frequency of the DSP.

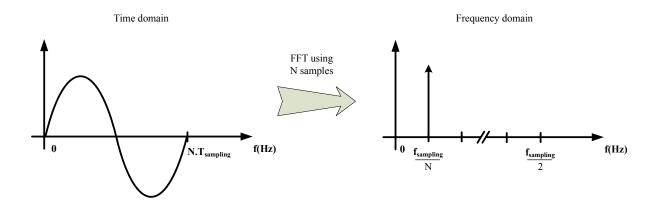

The example of a pure sinewave is given. Figure 2.4 depicts the FFT of such a signal. The FFT is a Dirac at the frequency of the signal. Figure 2.5 exhibits an Amplitude Modulation (AM). It is characterised by a carrier ( $f_{\text{carrier}}$ ) and a modulated signal ( $f_{\text{signal}}$ ). The FFT is given by a Dirac at the frequency of  $f_{\text{carrier}} + f_{\text{signal}}$ . The SASP enables to select the Dirac and translate it into baseband in the frequency domain. Once done, it is just a matter to process an IFFT to recover the modulated signal. Consequently, the principle of the SASP is to remove any RF

2.1. Principle 55

carrier of RF signals. Figure 2.5 represents both time domain and frequency domain whereas the SASP only works in time domain. In the case of the SASP, frequency domain is projected in time domain.

Figure 2.3: Envelope selection and digitization

Figure 2.4: Sinewave FFT

Figure 2.5: Frequency Translation of a modulated signal

# 2.1.3 A Fourier Transform

The SASP aims at processing the RF input signal spectrum. The spectral envelope of the target RF signal is analogically selected and sent to the ADC (Fig. 2.2). To carry out the operation, the SASP implements an analog Discrete Fourier Transform (DFT). Parameters inherited from the DFT equation (Eq. 2.2) master the SR requirements such as reprogrammability and flexibility: the sampling frequency  $f_{\text{sampling}}$  and the number of voltage samples N are taken into account to determine the spectral accuracy.

The Fourier Transform equation in continuous time domain is given by:

$$X(f) = \int_{-\infty}^{+\infty} x(t) \exp(-j2\pi f t) dt$$

(2.1)

The SASP is based on a discretization of the input signal x(t). x(t) is sampled at a period of  $T_{\text{sampling}}$  in an infinite range of time. The Discrete time Fourier Transform is thus given by:

$$x(k) = x(t)_{t=kT_{\text{sampling}}}$$

$$X(\nu) = \sum_{k=-\infty}^{+\infty} x(k) \exp\left(-j2\pi\nu k T_{\text{sampling}}\right), \quad -\infty < \nu < +\infty$$

(2.2)

The Discrete time Fourier Transform calculation is limited to a finite number of points N. As N samples are selected in the time domain, N frequencies are processed thanks to a Discrete Fourier Transform (DFT).  $n_{\text{sample}}$  is the frequency sample number in a DFT processing sequence. It gives the equation:

$$X(n_{\text{sample}}) = \sum_{k=0}^{N-1} x(k) \exp\left(\frac{-j2\pi n_{\text{sample}}k}{N}\right), \qquad n_{\text{sample}} = 0, 1, \dots, N-1$$

(2.3)

Equation 2.3 requires:

- N equations to represent each frequency.

- For each equation, N complex multiplications and N-1 complex additions.

In terms of operations, equation 2.3 needs  $N^2$  complex multiplications and N(N-1) complex additions. N is an integer that can be very high. Consequently, the signal processing asked by a DFT can cost a lot of processing complexity and consequently in die area and power consumption. An other solution has to be found: a FFT.

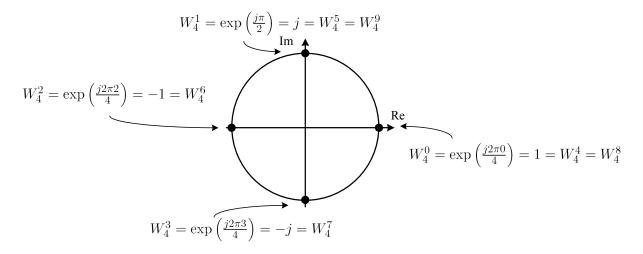

In order to simplify the SASP architecture, the FFT algorithm [37] in its pipeline form was used [38, 39]. It reduces the number of operations from  $N^2$  to  $N.\log_2(N)$ . [38, 39] efficiently computes a DFT.

# 2.2 A Fast Fourier Transform

#### 2.2.1 The Cooley-Tukey algorithm